一种带有两个周期的高速ROM电路的制作方法

一种带有两个周期的高速rom电路

技术领域

1.本发明涉及高速rom电路技术领域,具体是一种带有两个周期的高速rom电路。

背景技术:

2.rom(read-only memory)是一种只读存储器,在芯片制造阶段,预存数据(例如,启动程序)通过特定光罩烧录在rom中,并且不能被更改。在超大规模集成电路芯片中往往嵌入有cpu,在芯片上电初始化的过程中,cpu需要从rom中读取初始化数据以顺利完成cpu的上电初始化。现有的初始化数据的读取方式是cpu通过spi(serial peripheral interface,串行外设接口)模块读取rom中的初始化数据,并且在cpu上电初始化完成后不能再读取rom中的数据。

3.现有技术中的rom电路如图4-6所示,其每个周期均precharge,读取速度不足,连续工作时,反而功耗较大。

技术实现要素:

4.本发明的目的在于提供一种带有两个周期的高速rom电路,以解决现有技术中的问题。

5.为实现上述目的,本发明提供如下技术方案:一种带有两个周期的高速rom电路,包括中央处理器、存储控制模块、rom存储器、第一加密模块、ram存储器、第二加密模块、eeprom存储器和第三加密模块,所述中央处理器和存储控制模块连接,所述rom存储器和第一加密模块连接,所述ram存储器和第二加密模块连接,所述eeprom存储器和第三加密模块连接;所述rom存储器、第一加密模块、ram存储器、第二加密模块、eeprom存储器和第三加密模块均与中央处理器连接;所述rom存储器、第一加密模块、ram存储器、第二加密模块、eeprom存储器和第三加密模块均与存储控制模块连接;

6.所述rom存储器包含两个周期,分别为active mode和low power mode。

7.优选的,还包括flash存储器和第四加密模块,所述flash存储器和第四加密模块连接,所述flash存储器分别与中央处理器和存储控制模块连接,所述第四加密模块分别与中央处理器和存储控制模块连接。

8.优选的,还包括报警模块,所述报警模块与中央处理器连接。

9.优选的,还包括备份模块,所述备份模块与中央处理器连接,所述备份模块与存储控制模块连接。

10.优选的,所述rom存储器设计包括以下步骤:

11.s1:将原有时序拆分为两个周期,分别为active mode和low power mode;

12.s2:当进入低功耗模式时,关闭precharge,自动降低bl电位,降低功耗。

13.优选的,还包括通过片选信号ce,来控制pre信号,当ce无效,便进入low power模式。

14.优选的,还包括增加lpw信号,外部控制pre信号。当lpw有效时,进入低功耗模式。

15.与现有技术相比,本发明的有益效果是:将原有时序拆分为两个周期,分别为active mode和low power mode;当进入低功耗模式时,关闭precharge,自动降低bl电位,降低功耗;通过片选信号ce,来控制pre信号,当ce无效,便进入low power模式;增加lpw信号,外部控制pre信号;当lpw有效时,进入低功耗模式。

附图说明

16.附图用来提供对本发明的进一步理解,并且构成说明书的一部分,与本发明的实施例一起用于解释本发明,并不构成对本发明的限制。在附图中:

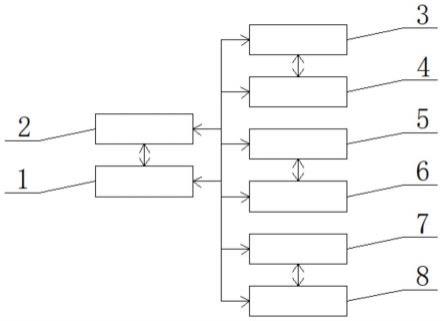

17.图1是本发明的原理图;

18.图2是本发明读取时序的流程图;

19.图3是本发明另一情况读取时序的流程图;

20.图4是现有技术的电路图;

21.图5是现有技术的读取电路图;

22.图6是现有技术的读取时序图。

23.图中:1、中央处理器;2、存储控制模块;3、rom存储器;4、第一加密模块;5、ram存储器;6、第二加密模块;7、eeprom存储器;8、第三加密模块。

具体实施方式

24.为使本发明实施方式的目的、技术方案和优点更加清楚,下面将结合本发明实施方式中的附图,对本发明实施方式中的技术方案进行清楚、完整地描述,显然,所描述的实施方式是本发明一部分实施方式,而不是全部的实施方式。基于本发明中的实施方式,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施方式,都属于本发明保护的范围。因此,以下对在附图中提供的本发明的实施方式的详细描述并非旨在限制要求保护的本发明的范围,而是仅仅表示本发明的选定实施方式。基于本发明中的实施方式,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施方式,都属于本发明保护的范围。

25.实施例一

26.请参阅图1-3,本发明实施例中,一种带有两个周期的高速rom电路,包括中央处理器、存储控制模块、rom存储器、第一加密模块、ram存储器、第二加密模块、eeprom存储器和第三加密模块,所述中央处理器和存储控制模块连接,所述rom存储器和第一加密模块连接,所述ram存储器和第二加密模块连接,所述eeprom存储器和第三加密模块连接;所述rom存储器、第一加密模块、ram存储器、第二加密模块、eeprom存储器和第三加密模块均与中央处理器连接;所述rom存储器、第一加密模块、ram存储器、第二加密模块、eeprom存储器和第三加密模块均与存储控制模块连接;

27.所述rom存储器包含两个周期,分别为active mode和low power mode。

28.优选的,还包括flash存储器和第四加密模块,所述flash存储器和第四加密模块连接,所述flash存储器分别与中央处理器和存储控制模块连接,所述第四加密模块分别与中央处理器和存储控制模块连接。

29.优选的,还包括报警模块,所述报警模块与中央处理器连接。

30.优选的,还包括备份模块,所述备份模块与中央处理器连接,所述备份模块与存储控制模块连接。

31.优选的,所述rom存储器设计包括以下步骤:

32.s1:将原有时序拆分为两个周期,分别为active mode和low power mode;

33.s2:当进入低功耗模式时,关闭precharge,自动降低bl电位,降低功耗。

34.优选的,还包括通过片选信号ce,来控制pre信号,当ce无效,便进入low power模式。

35.优选的,还包括增加lpw信号,外部控制pre信号。当lpw有效时,进入低功耗模式。

36.本发明的工作原理是:将原有时序拆分为两个周期,分别为active mode和low power mode;当进入低功耗模式时,关闭precharge,自动降低bl电位,降低功耗;通过片选信号ce,来控制pre信号,当ce无效,便进入low power模式;增加lpw信号,外部控制pre信号;当lpw有效时,进入低功耗模式。

37.实施例二

38.请参阅图1-3,本发明实施例中,一种带有两个周期的高速rom电路,包括中央处理器、存储控制模块、rom存储器、第一加密模块、ram存储器、第二加密模块、eeprom存储器和第三加密模块,所述中央处理器和存储控制模块连接,所述rom存储器和第一加密模块连接,所述ram存储器和第二加密模块连接,所述eeprom存储器和第三加密模块连接;所述rom存储器、第一加密模块、ram存储器、第二加密模块、eeprom存储器和第三加密模块均与中央处理器连接;所述rom存储器、第一加密模块、ram存储器、第二加密模块、eeprom存储器和第三加密模块均与存储控制模块连接;

39.所述rom存储器包含两个周期,分别为active mode和low power mode。

40.优选的,还包括报警模块,所述报警模块与中央处理器连接。

41.优选的,还包括备份模块,所述备份模块与中央处理器连接,所述备份模块与存储控制模块连接。

42.优选的,所述rom存储器设计包括以下步骤:

43.s1:将原有时序拆分为两个周期,分别为active mode和low power mode;

44.s2:当进入低功耗模式时,关闭precharge,自动降低bl电位,降低功耗。

45.优选的,还包括通过片选信号ce,来控制pre信号,当ce无效,便进入low power模式。

46.优选的,还包括增加lpw信号,外部控制pre信号。当lpw有效时,进入低功耗模式。

47.本发明的工作原理是:将原有时序拆分为两个周期,分别为active mode和low power mode;当进入低功耗模式时,关闭precharge,自动降低bl电位,降低功耗;通过片选信号ce,来控制pre信号,当ce无效,便进入low power模式;增加lpw信号,外部控制pre信号;当lpw有效时,进入低功耗模式。

48.实施例三

49.请参阅图1-3,本发明实施例中,一种带有两个周期的高速rom电路,包括中央处理器、存储控制模块、rom存储器、第一加密模块、ram存储器、第二加密模块、eeprom存储器和第三加密模块,所述中央处理器和存储控制模块连接,所述rom存储器和第一加密模块连接,所述ram存储器和第二加密模块连接,所述eeprom存储器和第三加密模块连接;所述rom

存储器、第一加密模块、ram存储器、第二加密模块、eeprom存储器和第三加密模块均与中央处理器连接;所述rom存储器、第一加密模块、ram存储器、第二加密模块、eeprom存储器和第三加密模块均与存储控制模块连接;

50.所述rom存储器包含两个周期,分别为active mode和low power mode。

51.优选的,还包括flash存储器和第四加密模块,所述flash存储器和第四加密模块连接,所述flash存储器分别与中央处理器和存储控制模块连接,所述第四加密模块分别与中央处理器和存储控制模块连接。

52.优选的,还包括备份模块,所述备份模块与中央处理器连接,所述备份模块与存储控制模块连接。

53.优选的,所述rom存储器设计包括以下步骤:

54.s1:将原有时序拆分为两个周期,分别为active mode和low power mode;

55.s2:当进入低功耗模式时,关闭precharge,自动降低bl电位,降低功耗。

56.优选的,还包括通过片选信号ce,来控制pre信号,当ce无效,便进入low power模式。

57.优选的,还包括增加lpw信号,外部控制pre信号。当lpw有效时,进入低功耗模式。

58.本发明的工作原理是:将原有时序拆分为两个周期,分别为active mode和low power mode;当进入低功耗模式时,关闭precharge,自动降低bl电位,降低功耗;通过片选信号ce,来控制pre信号,当ce无效,便进入low power模式;增加lpw信号,外部控制pre信号;当lpw有效时,进入低功耗模式。

59.最后应说明的是:以上所述仅为本发明的优选实施例而已,并不用于限制本发明,尽管参照前述实施例对本发明进行了详细的说明,对于本领域的技术人员来说,其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1