一种基于存储器冗余的SRAM型FPGA配置系统的制作方法

一种基于存储器冗余的sram型fpga配置系统

技术领域

1.本发明涉及一种基于存储器冗余的sram型fpga配置系统,属于卫星数据处理与传输领域,增强了sram型fpga配置电路的可靠性和灵活性,适用于各类适用sram型fpga的卫星应用场景。

背景技术:

2.sram型fpga因其通用性、快速开发等特点在卫星技术领域得到了广泛应用,但随着晶体管和半导体制造工艺的迅速发展,该类fpga工艺尺寸不断减小,内核电压不断降低,对于空间高能粒子所引发的单粒子效应的敏感度不断增强。现有技术方案通常使用逻辑的三模冗余或硬件的定时刷新技术,从而减小单粒子效应的影响,然而这两类方式功能单一、灵活性不足,逐渐不能满足应用需求。因此,如何对该类fpga采取一定的防护措施,并支持配置、刷新、回读校验、程序上注等多种功能,满足对航天器载荷可靠性和灵活性的要求,成为了关键问题。

技术实现要素:

3.本发明解决的技术问题为:克服现有技术不足,提出一种基于存储器冗余的sram型fpga配置系统,使用3片可读写(以下简称为存储器)存储器对配置文件进行器件级冗余存储,并结合配置、刷新、回读校验和程序上注功能,提高系统的可靠性和灵活性。本发明适用于各类使用sram型fpga的卫星应用场景。

4.本发明的技术解决方案是:

5.一种基于存储器冗余的sram型fpga配置系统,包括:多个可读写存储器、高可靠逻辑器件和sram型fpga;

6.可读写存储器:用于响应高可靠逻辑器件的读写操作,并反馈读写操作结果至高可靠逻辑器件;

7.高可靠逻辑器件:接收外部输入的控制指令;接收外部发送的sram型fpga配置数据包,进行解析和拼接处理,获得解析和拼接后的sram型fpga配置数据包,根据控制指令传输给可读写存储器或sram型fpga;根据控制指令从任意一个可读写存储器中读取sram型fpga配置数据包,进行校验和计算,获得校验和计算结果并存储;根据控制指令将任意一片可读写存储器中读取的sram型fpga配置数据包传输给sram型fpga并获得sram型fpga反馈的配置操作结果和刷新操作结果;根据控制指令从多片可读写存储器中同时读取sram型fpga配置数据包,进行三选二表决,获得表决后的sram型fpga配置数据包并传输给sram型fpga,并获得sram型fpga反馈的配置操作结果和刷新操作结果;接收可读写存储器反馈的读写操作结果,将读写操作结果、配置操作结果、刷新操作结果、校验结果和计算结果组成状态信息帧,并根据控制指令向外部输出;

8.sram型fpga:接收高可靠逻辑器件传输的sram型fpga配置数据包,根据控制指令进行只配置不刷新处理,或进行配置并刷新处理。

9.可选地,可读写存储器的个数大于或等于3。

10.可选地,所述控制指令包括:第一程序上注指令、第二程序上注指令、回读校验指令、只配置不刷新指令、配置刷新指令、三模冗余只配置不刷新指令、三模冗余配置并刷新指令或状态信息请求指令。

11.可选地,在接收到第一程序上注指令时,高可靠逻辑器件将解析和拼接后的sram型fpga配置数据包传输给第一程序上注指令中指定的可读写存储器;

12.在接收到第二程序上注指令时,高可靠逻辑器件将解析和拼接后的sram型fpga配置数据包传输给sram型fpga,对sram型fpga进行配置处理,并获得sram型fpga反馈的配置操作结果。

13.可选地,在接收到回读校验指令时,高可靠逻辑器件从回读校验指令中指定的可读写存储器中读取sram型fpga配置数据包,进行校验和计算,获得校验和计算结果并存储。

14.可选地,在接收到只配置不刷新指令时,高可靠逻辑器件从可读写存储器中读取的sram型fpga配置数据包传输给sram型fpga,对sram型fpga进行配置处理,并获得sram型fpga反馈的配置操作结果;

15.在接收到配置刷新指令时,高可靠逻辑器件从可读写存储器中读取的sram型fpga配置数据包传输给sram型fpga,对sram型fpga进行配置并刷新处理,并获得sram型fpga反馈的配置操作结果和刷新操作结果。

16.可选地,在接收到三模冗余只配置不刷新指令时,高可靠逻辑器件从多片可读写存储器中同时读取sram型fpga配置数据包,进行三选二表决,获得表决后的sram型fpga配置数据包并传输给sram型fpga,对sram型fpga进行配置处理,并获得sram型fpga反馈的配置操作结果。

17.可选地,在接收到三模冗余配置并刷新指令时,高可靠逻辑器件从多片可读写存储器中同时读取sram型fpga配置数据包,进行三选二表决,获得表决后的sram型fpga配置数据包并传输给sram型fpga,对sram型fpga进行配置和刷新处理,并获得sram型fpga反馈的配置操作结果和刷新操作结果。

18.可选地,在接收到状态信息请求指令时,高可靠逻辑器件接收可读写存储器反馈的读写操作结果,将读写操作结果、配置操作结果、刷新操作结果、校验结果和计算结果组成状态信息帧,并向外部输出。

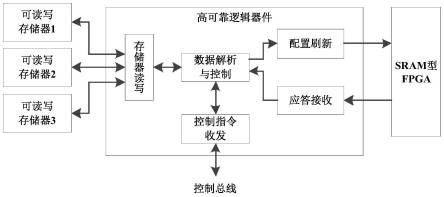

19.可选地,高可靠逻辑器件包括:控制指令收发模块、数据解析与控制模块、存储器读写模块、配置刷新模块和应答接收模块;

20.控制指令收发模块:接收外部输入的控制指令;接收外部发送的sram型fpga配置数据包,并输出给数据解析与控制模块;将数据解析与控制模块发送的状态信息帧通过控制总线向外部输出;

21.数据解析与控制模块:接收控制指令收发模块发送的sram型fpga配置数据包,进行解析和拼接处理,获得解析和拼接后的sram型fpga配置数据包;在收到第一程序上注指令时,将sram型fpga配置数据包传输给存储器读写模块;在收到第二程序上注指令时,将sram型fpga配置数据包传输给配置刷新模块,并获得sram型fpga反馈的配置操作结果;在收到回读校验指令时,接收存储器读写模块传输的sram型fpga配置数据包,进行校验和计算,获得校验和计算结果并存储;在收到配置刷新指令时,接收存储器读写模块传输的sram

型fpga配置数据包并传输给配置刷新模块,并获得sram型fpga反馈的配置操作结果和刷新操作结果;在收到三模冗余只配置不刷新指令和三模冗余配置并刷新指令时,接收存储器读写模块传输的三个sram型fpga配置数据包进行三选二表决,获得表决后的sram型fpga配置数据包并传输给配置刷新模块,并获得sram型fpga反馈的配置操作结果和刷新操作结果;在收到状态信息请求指令时,接收存储器读写模块反馈的读写操作结果,将读写操作结果、配置操作结果、刷新操作结果、校验结果和计算结果组成状态信息帧转发给控制指令收发模块;

22.配置刷新模块:接收数据解析与控制模块发送的sram型fpga配置数据包;在收到第二程序上注指令时,将sram型fpga配置数据包传输给sram型fpga,对sram型fpga进行配置处理,并获得sram型fpga反馈的配置操作结果;在收到只配置不刷新指令时,将sram型fpga配置数据包传输给sram型fpga,对sram型fpga进行配置处理,并获得sram型fpga反馈的配置操作结果;在收到配置刷新指令时,将sram型fpga配置数据包传输给sram型fpga,对sram型fpga进行配置和刷新处理,并获得sram型fpga反馈的配置操作结果和刷新操作结果;在收到三模冗余只配置不刷新指令时,使用表决后的sram型fpga配置数据包对sram型fpga进行配置处理,并获得sram型fpga反馈的配置操作结果;在收到三模冗余配置并刷新指令时,使用表决后的sram型fpga配置数据包对sram型fpga进行配置刷新处理,并获得sram型fpga反馈的配置操作结果和刷新操作结果;

23.存储器读写模块:接收数据解析与控制模块传输的sram型fpga配置数据包并转发给可读写存储器;从可读写存储器中读取sram型fpga配置数据包,并转发给数据解析与控制模块;接收可读写存储器反馈的读写操作结果,并转发给数据解析与控制模块;

24.应答接收模块:接收sram型fpga反馈的配置操作结果和刷新操作结果并传输给数据解析与控制模块。

25.本发明与现有技术相比的优点在于:本发明设计了一种基于存储器冗余的sram型fpga配置系统,使用基于存储器的冗余方案,达到了对sram型fpga配置数据包的器件级冗余存储,避免了存储器器件失效和空间粒子效应等异常状况导致的sram型fpga配置数据包错误。同时,结合控制总线的各类控制指令,实现了配置刷新、回读校验和程序上注的功能,在增强空间环境下可靠性的同时,丰富了功能和工作模式,提升系统的灵活性。

附图说明

26.图1为本发明的硬件原理框图。

27.图2为本发明支持的工作模式。

具体实施方式

28.本发明公开了一种基于存储器冗余的sram型fpga配置系统,使用基于存储器的冗余方案,达到了对sram型fpga配置数据包的器件级冗余存储,避免了存储器器件失效和空间粒子效应等异常状况导致的sram型fpga配置数据包错误。同时,结合控制总线的各类控制指令,实现了配置刷新、回读校验和程序上注的功能,在增强空间环境下可靠性的同时,丰富了功能和工作模式,提升系统的灵活性。

29.如图1所示,本发明一种基于存储器冗余的sram型fpga配置系统,包括1条控制总

线、3片可读写存储器、1片高可靠逻辑器件和1片sram型fpga。

30.控制总线:完成本方案中控制指令和sram型fpga配置数据包的接收,以及本方案状态信息的发送。其中,控制指令包括配置刷新、回读校验、程序上注和状态信息请求等,状态信息包括配置刷新、回读校验和程序上注的执行结果,以及存储器校验和的计算结果等。具体的控制指令包括:可读写存储器1只配置不刷新指令a1、可读写存储器2只配置不刷新指令a2、可读写存储器3只配置不刷新指令a3、可读写存储器1配置并刷新指令a4、可读写存储器2配置并刷新指令a5、可读写存储器3配置并刷新指令a6、存储器三模冗余只配置不刷新指令a7、存储器三模冗余配置并刷新指令a8、可读写存储器1回读校验指令b1、可读写存储器2回读校验指令b2、可读写存储器3回读校验指令b3、可读写存储器1程序上注指令c1、可读写存储器2程序上注指令c2、可读写存储器3程序上注指令c3、直接配置sram型fpga指令c4或状态信息请求指令d1。

31.可读写存储器:响应高可靠逻辑器件的读写操作,接收高可靠逻辑器件发送的sram型fpga配置数据包并进行存储,完成写操作,反馈写操作结果给高可靠逻辑器件;接收高可靠逻辑器件的请求信息,并将存储的数据输出,完成读操作,反馈读操作结果给高可靠逻辑器件。其中,3片存储器为器件级冗余设计,相互独立、功能相同,并可用于实现配置文件的存储器三模冗余。

32.高可靠逻辑器件:

33.1)接收和校验控制总线发送的配置刷新、回读校验和程序上注等控制指令,并完成相应的配置刷新、回读校验和程序上注功能;

34.2)接收和校验控制总线发送的sram型fpga配置数据包,并对其进行解析和拼接,获得解析和拼接后的sram型fpga配置数据包;

35.3)对可读写存储器反馈的读写操作结果、sram型fpga反馈的配置操作结果和刷新操作结果、sram型fpga配置数据包的校验和计算结果等信息组成状态信息帧,并进行存储;

36.4)在控制指令为配置刷新指令a1、a2、a3、a4、a5、a6时,从指令指定的1片可读写存储器中读取sram型fpga配置数据包,并将其输出至sram型fpga,完成只配置不刷新或配置并刷新功能,并获得sram型fpga反馈的配置操作结果和刷新操作结果;

37.5)在控制指令为配置刷新指令a7、a8时,从3片可读写存储器中同时读取sram型fpga配置数据包,进行三选二表决,从而纠正空间粒子效应引起的存储器数据错误,获得表决后配置数据包并输出至sram型fpga,完成存储器三模冗余只配置不刷新或配置并刷新功能,并获得sram型fpga反馈的配置操作结果和刷新操作结果;

38.6)在控制指令为回读校验指令b1、b2、b3时,从指令指定的1片可读写存储器中读取sram型fpga配置数据包,进行校验和计算,并存储校验和计算结果,完成回读校验功能。

39.7)在控制指令为程序上注指令c1、c2、c3时,将解析和拼接后的sram型fpga配置数据包输出至可读写存储器,在控制指令为程序上注指令c4时,将解析和拼接后的sram型fpga配置数据包输出至sram型fpga,完成数据程序上注功能;

40.8)在控制指令为状态信息请求指令d1时,将存储的状态信息帧通过控制总线输出。

41.sram型fpga:接收高可靠逻辑器件发来的配置指令或刷新指令,以及sram型fpga配置数据包,完成本fpga的配置或刷新,获得配置操作结果和刷新操作结果;并将配置操作

结果和刷新操作结果输出至高可靠逻辑器件。

42.所述高可靠逻辑器件,包括:控制指令收发模块、数据解析与控制模块、存储器读写模块、配置刷新模块和应答接收模块。

43.控制指令收发模块:接收控制总线发送的控制指令ram型fpga配置数据包,并输出给数据解析与控制模块;将数据解析与控制模块发送的状态信息帧通过控制总线输出。

44.数据解析与控制模块:

45.1)接收控制指令收发模块发送的控制指令,控制各模块完成相应操作;

46.2)接收控制指令收发模块发送的sram型fpga配置数据包,并对其进行解析和拼接;

47.3)在控制指令为配置刷新指令a1、a2、a3、a4、a5、a6时,从指令指定的1片可读写存储器中读取sram型fpga配置数据包,并将其输出至配置刷新模块;

48.4)在控制指令为配置刷新指令a7、a8时,从3片可读写存储器中同时读取sram型fpga配置数据包,进行三选二表决,并将表决后配置数据包输出至配置刷新模块;

49.5)在控制指令为回读校验指令b1、b2、b3时,从指令指定的1片可读写存储器中读取sram型fpga配置数据包,进行校验和计算,并存储校验和计算结果。

50.6)在控制指令为程序上注指令c1、c2、c3时,将解析和拼接后的sram型fpga配置数据包输出至存储器读写模块。

51.7)在控制指令为程序上注指令c4时,将解析和拼接后的sram型fpga配置数据包输出至配置刷新模块;

52.8)接收存储器读写模块发来的读写操作结果,应答接收模块发来的配置操作结果和刷新操作结果,与校验和计算结果等信息组成状态信息帧,并进行存储;

53.9)在控制指令为状态信息请求指令d1时,将存储的状态信息帧输出至控制指令收发模块;

54.存储器读写模块:接收数据解析与控制模块发送的sram型fpga配置数据包,并输出至可读写存储器;从可读写存储器中读取sram型fpga配置数据包,并输出至数据解析与控制模块;接收可读写存储器反馈的读写操作结果,并转发给数据解析与控制模块。

55.配置刷新模块:接收数据解析与控制模块发送的sram型fpga配置数据包或三选二表决后的配置数据包,并输出至sram型fpga。

56.应答接收模块:接收sram型fpga反馈的配置操作结果和刷新操作结果,并输出至数据解析与控制模块。

57.在控制总线的模式控制下,如图2所示,本方案支持的工作模式有:

58.(1)配置刷新模式:

59.a)只配置不刷新:3片可读写存储器中的配置数据包可相同,也可不同。高可靠逻辑器件读取指令指定的1片可读写存储器中的配置数据包,实现对sram型fpga的配置;

60.b)配置并刷新:3片可读写存储器中的配置数据包可相同,也可不同。高可靠逻辑器件读取指令指定的1片可读写存储器中的数据包,实现对sram型fpga的配置与刷新;

61.c)存储器三模冗余只配置不刷新:3片可读写存储器中的配置数据包相同。高可靠逻辑器件同时读取3片可读写存储器中的数据包,并进行三选二表决,从而纠正空间粒子效应引起的存储器数据错误,实现对sram型fpga的三模冗余配置;

62.d)存储器三模冗余配置并刷新:3片可读写存储器中的配置数据包相同。高可靠逻辑器件同时读取3片可读写存储器中的数据包,并进行三选二表决,从而纠正空间粒子效应引起的存储器数据错误,实现对sram型fpga的三模冗余配置与刷新。

63.(2)回读校验模式:

64.a)回读校验:高可靠逻辑器件读取其中1片可读写存储器中的配置数据包,计算校验和结果,并将结果通过控制总线输出。如结果错误,则通过控制总线传输sram型fpga配置数据包,对可读写存储器中数据进行更新;如果结果正确,则不更新可读写存储器中的数据。

65.b)不回读校验:不进行任何回读校验;

66.(3)程序上注模式:

67.a)存储器程序上注:高可靠逻辑器件接收来自控制总线的控制指令和配置数据包,将sram型fpga配置数据包存储于对应存储器中,从而实现存储器中配置数据包的更新。

68.b)直接配置sram型fpga:高可靠逻辑器件接收来自控制总线的控制指令和配置数据包,将sram型fpga配置数据包直接用于对sram型fpga进行配置,而不更改任一存储器中的数据包。

69.为使本发明的方法更易理解,对本发明进行举例说明。

70.方案中的存储器选用具备一定抗单粒子能力的可读写存储器如抗辐照加固的flash或ram,高可靠逻辑器件选用actel公司的反熔丝fpga、xilinx公司的sram型fpga,控制总线选用rs422总线。

71.方案可实现的工作模式为:

72.(1)方案中系统上电后,反熔丝fpga从可读写存储器1中读取配置数据包,对sram型fpga进行配置;

73.(2)完成配置后,反熔丝fpga从可读写存储器1中读取配置数据包,对sram型fpga进行刷新;

74.(3)完成刷新后,依次从可读写存储器1、可读写存储器2和可读写存储器3中读取其中存储的配置数据包,计算校验和,并存储校验和计算结果;

75.(4)如需对可读写存储器1进行程序上注,则控制总线发送相应指令和配置数据包至反熔丝fpga,再通过反熔丝fpga将控制总线发送的配置数据包存储于可读写存储器1中,从而完成对可读写存储器1的程序上注;

76.(5)如需对sram型fpga直接配置,则通过控制总线发送相应指令和配置数据包至反熔丝fpga,再通过反熔丝fpga将控制总线发送的配置数据包直接用于对sram型fpga进行配置。

77.本发明虽然已以较佳实施例公开如上,但其并不是用来限定本发明,任何本领域技术人员在不脱离本发明的精神和范围内,都可以利用上述揭示的方法和技术内容对本发明技术方案做出可能的变动和修改,因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化及修饰,均属于本发明技术方案的保护范围。在不冲突的情况下,本技术实施例以及实施例中的技术特征可以相互组合。

78.本发明说明书中未作详细描述的内容属本领域技术人员的公知技术。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1