基于虚拟指令集平台的异常测试方法、系统及存储介质与流程

1.本发明属于安全关键领域的软件测试技术,特别涉及一种基于虚拟指令集平台的异常测试方法、系统及存储介质。

背景技术:

2.fadec控制软件属于安全关键领域的重要技术,当控制软件发生异常时,cpu芯片必须能够及时响应,执行异常处理,以防代码跑飞或执行错误指令。所以,异常测试是控制软件测试的必做工作。传统的测试方法是基于硬件控制器通过插桩和串口打印测试结果,这种方法受限于串口协议,无法准确显形寄存器、内存变化,只能显示部分变量测试结果,难以从微观的角度捕捉并分析cpu异常状态,可信度和准确度大大降低;此外,硬件测试需要配合控制器,测试台以及适配箱等,统一协调不易,在硬件控制器上人为插桩测试时,每个用例的测试方法不同,且需重复执行复位烧写过程,效率低,易出错。

技术实现要素:

3.发明目的:本发明的目的是提出一种基于虚拟指令集平台的异常测试方法,测试效率高且不受硬件资源限制,提高测试人员的测试效率。

4.本发明的另一目的是提出一种可以实施上述异常测试方法的测试系统及存储有上述异常测试方法实例化的计算机程序的存储介质。

5.技术方案:本发明所述的基于虚拟指令集平台的异常测试方法,包括如下步骤:

6.s1:根据待测硬件信息,在虚拟指令集平台上搭建虚拟目标系统;

7.s2:根据选择的vcpu和测试计划,从异常测试构件库中选择异常测试构件,并根据选择的异常测试构件生成动态链接库文件;

8.s3:在虚拟目标系统上加载控制软件的bin文件,启动虚拟目标系统进入正常运行模式,确认各个监视变量符合期望值;

9.s4:发动机仿真模型上位机通过动态链接库文件动态触发异常测试构件,执行自动化测试,并存储构件的输出结果。

10.进一步的,所述步骤s2中的异常测试构件由异常构件模型生成,异常构件模型包括如下项目:

11.输入接口,用于配置构件的输入参数;

12.访问地址,用于配置构件运行的地址空间;

13.权限配置,用于配置构件的访问权限;

14.指令操作,用于设置构件的具体动作;

15.输出接口,用于配置构件的输出参数。

16.进一步的,所述步骤s2中的动态链接库文件遵循以下原则:所有异常测试构件需在无其他高优先级中断触发时触发,且触发后进行中断处理过程。

17.进一步的,所述步骤s3中,每个被触发的异常测试构件均在虚拟目标系统的头地

址开始执行。

18.本发明所述的基于虚拟指令集平台的异常测试系统,包括虚拟目标系统、异常测试构件库、异常测试用例生成模块及发动机仿真模型上位机,所述虚拟目标系统根据待测硬件信息在虚拟指令集平台上搭建,所述异常测试用例生成模块用于根据从异常测试构件库中选择的异常测试构件生成动态链接库文件,所述发动机仿真模型上位机根据动态链接库文件在所述虚拟目标系统上动态触发异常测试构件。

19.本发明所述的存储介质,存储有计算机程序,所述计算机程序被设计为运行时实现上述基于虚拟指令集平台的异常测试方法。

20.有益效果:与现有技术相比,本发明具有如下优点:通过在虚拟指令集平台上搭设虚拟目标系统进行测试,不受限于硬件资源,测试方便同时避免测试环境影响造成的测试失误。通过构件异常测试构件,并通过发动机仿真模型上位机动态触发,提升了测试效率,且异常测试构件易于迁移,测试过程统一且不易出错。

附图说明

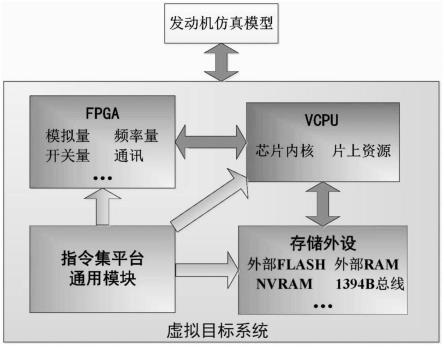

21.图1为本发明实施例的虚拟目标系统的结构图;

22.图2为本发明实施例的异常测试用例生成模块的界面图;

23.图3为本发明实施例的异常测试用例运行界面图。

具体实施方式

24.下面结合附图对本发明的技术方案作进一步说明。

25.根据本发明实施例的基于虚拟指令集平台的异常测试方法,包括如下步骤:

26.s1:根据待测硬件信息,在虚拟指令集平台上搭建虚拟目标系统;

27.s2:根据选择的vcpu和测试计划,从异常测试构件库中选择异常测试构件,并根据选择的异常测试构件生成动态链接库文件;

28.s3:在虚拟目标系统上加载控制软件的bin文件,启动虚拟目标系统进入正常运行模式,确认各个监视变量符合期望值;

29.s4:发动机仿真模型上位机通过动态链接库文件动态触发异常测试构件,执行自动化测试,并存储构件的输出结果。

30.上述测试方法,通过根据待测试的硬件建立的虚拟目标系统上运行控制软件,并采用全数字的发动机仿真模型上位机动态触发预先建立的异常测试构件,测试过程自动化,提升了测试效率,不受限于串口协议,可以准确显形寄存器和内存变化,提升测试可信度及准确度,避免由于测试环境影响造成侧测试失误。同时测试过程不受限于硬件资源,建立的异常测试构件易于迁移,可以重复使用,保证测试过程统一,测试不易出错。

31.参照图1,虚拟目标系统的构件如图所示,根据待测的硬件的cpu信息、fpga以及存储外设的信息选择虚拟指令集平台上的指令集,配置虚拟cpu及存储外设的资源等构成虚拟目标系统。在本实施例中,虚拟指令集平台基于qemu虚拟机开发,支持包括mpc5554芯片、mpc5674芯片及p2020芯片三种芯片的指令集,并能根据测试需求增加外设模块功能。

32.异常测试构件库中的异常测试构件具有统一的构件模板,模板包括如下信息:

33.输入接口,用于配置构件的输入参数;

34.访问地址,用于配置构件运行的地址空间;

35.权限配置,用于配置构件的访问权限;

36.指令操作,用于设置构件的具体动作;

37.输出接口,用于配置构件的输出参数。

38.根据上述模板,结合实际测试需求进行设置即可得到不同类别的异常测试构件。常用的fadec控制软件的异常包括及其检查异常、数据读写访问异常、指令访问异常、看门狗异常、数据tlb错误异常、数据非对其访问异常、浮点除零异常、数据缓存未命中异常、指令缓存未命中异常、减数器中断异常及固定定时器中断异常,上述异常的异常测试构件基本设置如下:

39.1)机器检查异常:[访问地址]配置为不可用地址空间,[权限配置]配置为可访问,[指令操作]配置为跳转指令,其余默认配置;

[0040]

2)数据读写访问异常:[访问地址]配置为虚拟内存地址空间,[权限配置]配置为不可读取权限,[指令操作]配置为数据读取指令,其余默认配置;

[0041]

3)指令访问异常:[访问地址]配置为虚拟内存地址空间,[权限配置]配置为禁止执行权限,[指令操作]配置为跳转指令,其余默认配置;

[0042]

4)看门狗异常:[指令操作]配置使能看门狗寄存器指令,并设置看门狗定时器长度,其余默认配置;

[0043]

5)数据tlb错误异常:[访问地址]配置为虚拟flash地址空间,[权限配置]配置为禁止tlb权限,[指令操作]配置为数据读取指令,其余默认配置;

[0044]

6)指令tlb错误异常:[访问地址]配置为虚拟flash地址空间,[权限配置]配置为禁止tlb权限,[指令操作]配置为跳转指令,其余默认配置;

[0045]

7)数据非对齐访问异常:[访问地址]配置为虚拟内存地址空间(非4字节对齐),[权限配置]配置为可访问,[指令操作]配置为数据读取指令,其余默认配置;

[0046]

8)浮点除零异常:[访问地址]配置为某段虚拟内存地址空间,[权限配置]配置为可访问,[指令操作]配置为除零代码对应指令,其余默认配置;

[0047]

9)数据缓存未命中异常:[访问地址]配置为mmu未配置的数据地址空间,[权限配置]配置为可访问,[指令操作]配置为数据写入指令,其余默认配置;

[0048]

10)指令缓存未命中异常:[访问地址]配置为mmu未配置的指令地址空间,[权限配置]配置为可访问,[指令操作]配置为跳转指令,其余默认配置;

[0049]

11)减数器中断:[指令操作]配置为减数定时器中断使能指令,其余默认配置;

[0050]

12)固定定时器中断:[指令操作]配置为固定定时器中断使能指令,其余默认配置。

[0051]

其中在步骤s2中,异常测试构件的动态触发需要遵循以下规则:1、所有异常测试构件需要在无其他高优先级中断触发时才可以被触发,且触发后异常测试构件按中断处理过程处理。2、每个被触发的异常测试构件均在虚拟目标系统的头地址开始执行。发动机仿真模型上位机根据选择的异常测试构件生成的dll文件触发异常测试构件的运行界面如图3所示。其中规则1可以有效避免多重中断嵌套触发,便于识别终端类型和定位,从而便于定位异常。规则2则由于cpu复位后代码会从起始地址运行的软件执行流,实现虚拟与真实测试统一,提高测试的准确性。

[0052]

根据本发明实施例的基于虚拟指令集平台的异常测试系统,包括根据待测的硬件配置信息在虚拟指令集平台上搭建的虚拟目标系统,包含有多个根据统一模板生成的异常测试构件的异常测试构件库,根据选择的异常测试构件生成dll文件的异常测试用例生成模块,以及用于模拟仿真发动机的发动机仿真模型上位机。其中异常测试用例生成模块的界面如图2所示,左侧窗口显示异常测试构件库中的异常测试构件,可以选中左侧窗口中的异常测试构件并通过“add”虚拟按键添加至右侧被选择的构件的窗口,也可以通过选中右侧窗口中的构件并通过“delete”虚拟按键删除被选中的构件。选择完毕需要的异常测试构件后,点击“生成代码”虚拟按键即可根据已选择的异常测试构件,按照上述动态触发规则生成用于发动机仿真模型上位机触发用的dll文件。根据本发明实施例的存储介质,存储有上述异常测试方法实例化的计算机程序。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1