一种芯片加密方法及加密芯片与流程

本发明涉及半导体,特别是涉及一种芯片加密方法及加密芯片。

背景技术:

1、微处理器(microcontroller unit;mcu)集成电路芯片的程序和数据通常存放在非易失性存储器中,mcu类集成芯片商一般都会为客户设计加密机制,用来保护其客户的程序代码不受到他人盗版。第一种实现芯片仿破解的方法是软件加密,即软件方法对程序代码进行加密,主要有:使用不同反汇编软件造成正常程序的反汇编乱套,或者使用把部分程序代码和数据代码混淆,或使用加密软件加密待执行的程序等。第二种实现芯片防破解的方法是借助外部加密芯片或是内置加密模块,通过硬件电路实现对数据流进行同步加解密,因增加了算法加密的模块处理而增加了破解难度。第三种是利用芯片自带的加密功能,通过自带的加密锁或加密字节保护片内程序,来实现芯片程序的保护。第四种防破解方式将非易失性存储单元区分为可擦除存储器和只读存储单元,可擦除存储器里面存放重要的程序数据,而只读存储器中存放引导加载程序(bootload程序),一旦进入bootload程序,会对可擦除存储器中的数据进行第一时间按擦除,以保证芯片商业程序的安全性。还有一种破仿解方式通过记录电路对非易失性存储器的擦除读保护位次次数,对于超出给定次数阈值的读保护位擦除操作给出忽略的原理,来保护电路的读保护位,达到仿破解的效果。

2、但是上述加密方法有如下局限,第一种软件加密方法使得软件程序开发员不得不在设计初期在商业程序中加入隐蔽性好,可靠性高,算法设计漏洞少的加密算法,这给软件程序开发带来了不便,极大影响了其开发效率。第二种防破解方法或在芯片内部增加了加密模块,或是增加一块加密芯片,算法复杂,需要一定的面积开销,成本较高。第三种防破解方法需单独为bootload程序提供只读存储单元(read-only memory,rom),增加了芯片的面积,不适用于不含rom存储器的系统,成本较高。第四种方法的通过限制擦除保护位次数达到防破解效果,但对于不同的客户,读保护的方式均高度统一,缺乏客户专用性。

3、此外在以上所述所有防破解方法均只是为防止客户商业程序被盗,而在遇到芯片短缺的情况下,有些企业不需要盗窃对手企业的商业程序,而是想盗窃对手企业的芯片,那他无需破解芯片,只需将芯片擦成空片,并烧录自己的商业程序,取得非法收益,同时给原持有芯片的企业造成经济损失。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种芯片加密方法及加密芯片,用于解决现有技术中芯片加密需要复杂的加密算法、需要额外的加密模块及增加存储单元从而导致系统复杂成本增加的问题。

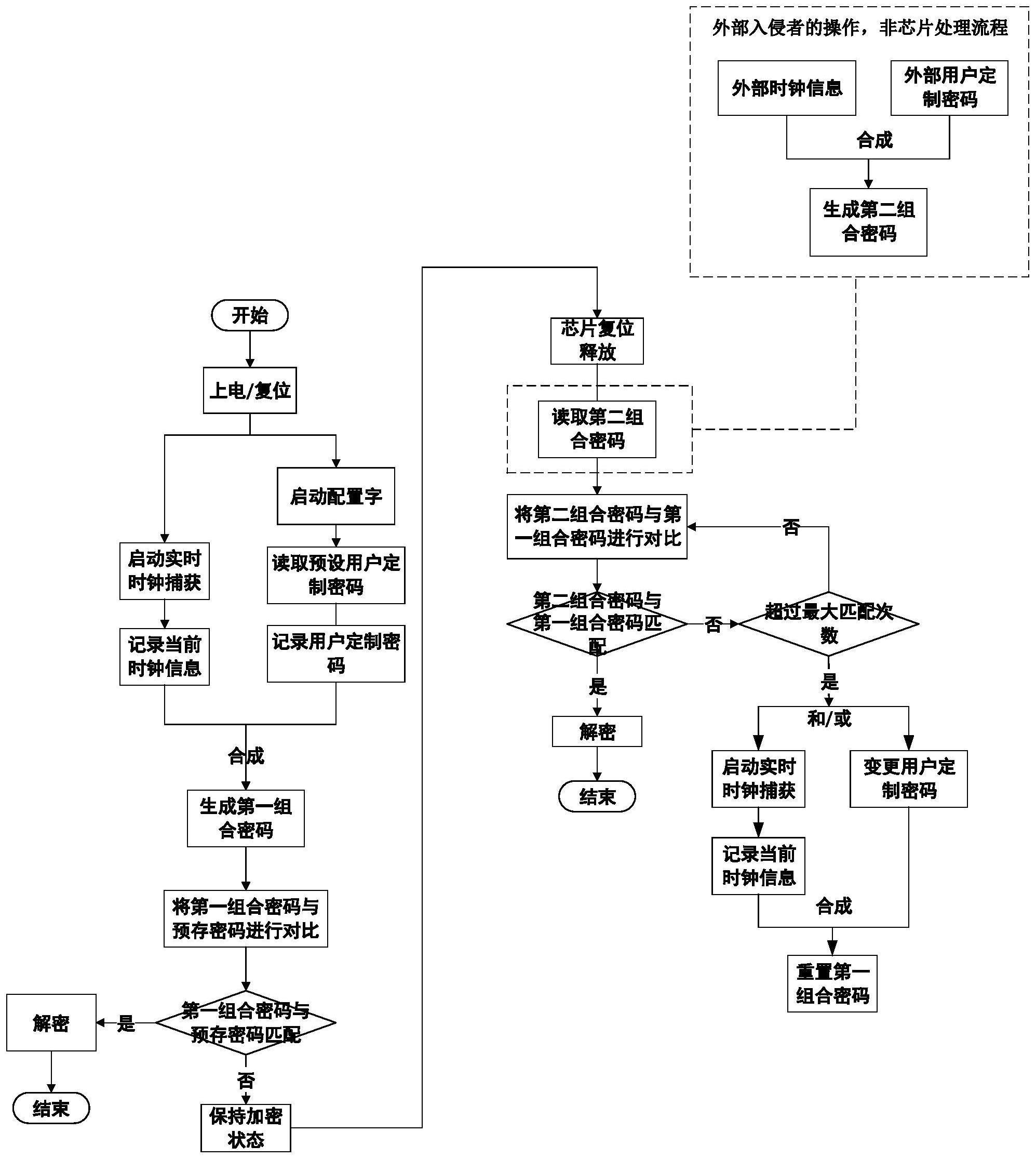

2、为实现上述目的及其他相关目的,本发明提供一种芯片加密方法,其特征在于,所述芯片加密方法至少包括:

3、1)进行上电或复位,启动配置字并捕获实时时钟;

4、2)记录用户定制密码与当前时钟信息,将所述用户定制密码与所述当前时钟信息合成,并生成第一组合密码;

5、3)将预存密码与所述第一组合密码进行对比,当所述第一组合密码与所述预存密码匹配时,进行解密操作,待所述解密操作完成后,结束所有操作;当所述第一组合密码与所述预存密码不匹配时,保持加密状态,并执行步骤4);

6、4)芯片复位释放,读取第二组合密码;

7、5)将所述第一组密码与所述第二组密码进行对比,当所述第一组密码与所述第二组密码匹配时,进行解密操作,待所述解密操作完成后,结束所有操作;

8、当所述第一组密码与所述第二组密码不匹配时,则重置所述第一组合密码。

9、可选地,所述用户定制密码包括:分级字段、组合方式字段及用户定义字段。

10、可选地,所述分级字段定义为程序级加密或芯片级加密,当所述分级字段定义为所述程序级加密时,所述芯片加密方法只对芯片进行读保护、写保护及页擦除保护;当所述分级字段定义为所述芯片级保护时,所述芯片加密方法对芯片进行读保护、写保护、页擦除保护及片擦除保护。

11、可选地,所述组合方式字段包括:最高有效位异或操作、最低有效位异或操作及去除实时时钟信息操作。

12、可选地,所述用户定制密码与所述实时时钟信息的合成方式为按位异或方式。

13、可选地,所述第二组合密码的一种生成方式为:入侵者将自己穷举的用户定制密码进行自定义加密处理,生成所述第二组合密码。

14、可选地,所述第二组合密码的另一种生成方式为:入侵者将自己穷举的用户定制秘密与实时获取的外部时钟信息合成,生成所述第二组合密码。

15、可选地,所述第一组合密码与所述第二组合密码匹配的方式包括:所述第一组合密码与所述第二组合密码首次对比即实现匹配;以及所述第一组合密码与所述第二组合密码首次不匹配,继续进行对比操作,当对比操作的次数小于等于最大匹配次数时,所述第一组合密码与所述第二组合密码完成匹配。

16、可选地,所述第一组合密码与所述第二组合密码不匹配的方式包括:所述第一组合密码与所述第二组合密码首次对比不匹配,继续进行对比操作,直至超过最大匹配次数,其中,在进行对比操作的过程中,所述第一组合密码与所述第二组合密码都不匹配。

17、可选地,重置所述第一组合密码的一种方式为:捕获实时时钟,记录当前时钟信息,将所述当前时钟信息与所述用户定制密码合成,重置所述第一组合密码。

18、可选地,重置所述第一组合密码的另一种方式为:捕获实时时钟,记录当前时钟信息,并变更用户定制密码,将变更后的所述用户定制密码与所述当前时钟信息合成,重置所述第一组合密码。

19、本发明提供一种加密芯片,所述加密芯片的架构为微处理器或数字信号处理器,包括映射模块和加密模块,用于实现所述的芯片加密方法,其中,所述映射模块与所述加密模块将所述加密芯片的烧录通道、调试通道及中央处理器访问通道合并。

20、可选地,所述加密模块包括:配置字读取模块、实时时钟模块、用户定制密码寄存器、分级组合密码产生逻辑、实时时钟捕获寄存器、匹配密码寄存器、匹配计数器、加解密产生逻辑及或门,其中:所述配置字模块及实时时钟模块的输入端接收由晶振提供的时钟信号;所述用户定制密码寄存器的输入端连接于所述配置字读取模块的输出端;所述实时时钟捕获寄存器的输入端连接于所述实时时钟模块的输出端;所述分级组合密码产生逻辑的输入端连接于所述用户定制密码寄存器与所述实时时钟捕获寄存器的输出端;所述匹配密码寄存器的输入端接收经外设总线传输的所述外部输入密码;所述加解密产生逻辑的输入端连接于所述分级组合密码产生逻辑与所述匹配密码寄存器的输出端,基于所述合成密码与所述外部输入密码进行对比操作的结果输出加密状态或解密状态;所述匹配计数器连接于所述匹配密码寄存器的控制端,用于对所述对比操作进行计数;所述或门的第一输入端连接于所述配置字读取模块的输出端,第二输入端连接于所述匹配计数器的输出端,输出端与所述用户定制密码寄存器及所述实时时钟捕获寄存器的控制端连接。

21、可选地,所述晶振的频率为32.768khz。

22、可选地,所述映射模块基于触发指令更改所述加密芯片的总线映射地址,将所述加密芯片的启动方式由闪存启动转化为由内存启动。

23、可选地,所述加密模块基于触发质量对所述加密芯片的总线地址进行加密保护,将保护区域从闪存区域扩展为闪存区域加内存区域。

24、如上所述,本发明的一种芯片加密方法及加密芯片,具有以下有益效果:

25、1)本发明通过将用户密码与实时时钟信息进行合成,使得加密芯片在不同的上电时间拥有不同的密码,利用极少量的硬件开销,大幅度增加解密的难度。

26、2)本发明通过修改总线映射地址,将加密芯片的启动方式由闪存启动转化为由内存启动,减少启动时间,增加破解芯片的难度。

27、3)本发明通过扩展保护区域,将保护区域从闪存区域扩展至闪存区域加内存区域,有效弥补漏洞,进一步增加破解芯片的难度。

- 还没有人留言评论。精彩留言会获得点赞!