一种基于FPGA芯片的人工智能编译技术管理系统的制作方法

一种基于fpga芯片的人工智能编译技术管理系统

技术领域

1.本发明涉及fpga芯片相关技术领域,具体为一种基于fpga芯片的人工智能编译技术管理系统。

背景技术:

2.fpga(field programmable gate array)是在pal(可编程阵列逻辑)、 gal(通用阵列逻辑)等可编程器件的基础上进一步发展的产物,它是作为专用集成电路(asic)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点,但是fpga芯片在面向用户自定义网络模态的需求,sdn网络在技术上无法通过灵活编程满足包含计算、存储、转发、安全在内的各种功能,在性能上也无法满足对复杂的网络模态进行高速处理;因此,在sdn网络中,研发一套软硬件协同编译处理系统,可以充分释放多种fpga目标系统编译模态数据的最大潜能,进而满足在不同的应用场景下,差异化的业务能力需求,为此,本发明提出一种基于fpga芯片的人工智能编译技术管理系统用以解决上述问题。

技术实现要素:

3.本发明的目的在于提供一种基于fpga芯片的人工智能编译技术管理系统,以解决上述背景技术中提出的问题。

4.为实现上述目的,本发明提供如下技术方案:一种基于fpga芯片的人工智能编译技术管理系统,所述基于fpga芯片的人工智能编译技术管理系统包括:

5.fpga芯片,以及配置在fpga芯片上的;

6.环境配置器,所述环境配置器用于配置编译环境所需的参数设置;

7.命令接收器,所述命令接收器用于接受用户的编译指令;

8.命令解析器,所述命令解析器用于对命令接收器接受到的编译指令进行解析处理;

9.一次代码填充器,所述代码填充器用于对命令解析器解析获取的数据进行输出,并获取用户源程序路径,读取源码并根据其中宏定义识别fpga目标系统,并填充补全fpga目标系统相关的代码,得到针对fpga目标系统的一次填充源码;

10.二次代码填充器,所述二次代码填充器通过对一次填充源码文件进行再处理,根据模态类型采用标准的vlan封装自定义vlan包头,填充到解析数据包代码部分,并输出二次填充源码文件;

11.调度器,所述调度器用于实现编译调度和执行调度功能;

12.fpga目标系统,所述fpga目标系统包括不少于两个fpga目标子系统。

13.优选的,所述一次代码填充器包括一次预处理识别器和一次接口定义器,所述一次预处理识别器用于根据命令解析器的输出,获取用户源程序路径,读取源码并根据其中宏定义识别fpga目标系统,并填充补全fpga目标系统相关的代码,输出针对这些fpga目标

系统的一次填充源码。

14.优选的,所述二次代码填充器包括二次预处理识别器和二次接口定义器,二次接口定义器用于对所述一次预处理识别器输出的一次填充源码文件再处理,根据模态类型采用标准的vlan封装自定义vlan包头,填充到解析数据包代码部分,并输出二次填充源码文件。

15.优选的,所述调度器包括编译调度器和执行调度器,所述编译调度器用于编译调度,所述执行调度器用于执行调度。

16.优选的,所述编译调度器用于编译调度,所述编译调度具体为,将二次接口定义器输出的二次填充源码文件传输到fpga目标系统上,依次启动fpga 目标系统进行分布式编译。

17.优选的,所述编译调度器在启动fpga目标系统进行分布式编译时,按照 fpga目标系统的处理性能由低到高启动。

18.优选的,所述执行调度器用于执行调度,所述执行调度具体为,将接收目标相关的后端编译器输出的可运行的目标文件与配置文件,依次将可运行的目标文件与配置文件分发到fpga目标系统中对应的目标子系统的运行环境中。

19.优选的,所述fpga目标系统的每个目标子系统均包括与目标相关的前端编译器、中端编译器、后端编译器以及与目标相关的运行环境;所述fpga目标系统用于编译处理用户模态数据。

20.优选的,所述fpga目标系统包括基于cpu的目标子系统、基于asic的目标子系统和基于fpga的目标子系统。

21.与现有技术相比,本发明的有益效果是:

22.通过设置包括fpga芯片,和配置在fpga芯片上的环境配置器、命令接收器、命令解析器、一次代码填充器、二次代码填充器、调度器、fpga目标系统组合构成的fpga芯片人工智能编译技术管理系统,其通过软硬件协同编译系统支持用户实现安全自定义的灵活编程,并对ip模态的数据包进行加密处理的加密算法和对数据认证的算法进行配置和封装如ipsec,实现对敏感数据的安全性进行加固,并且本发明的软硬件协同编译处理方法及系统支持用户实现转发自定义的灵活编程,如用户通过编程,实现组播和vlan标签。

附图说明

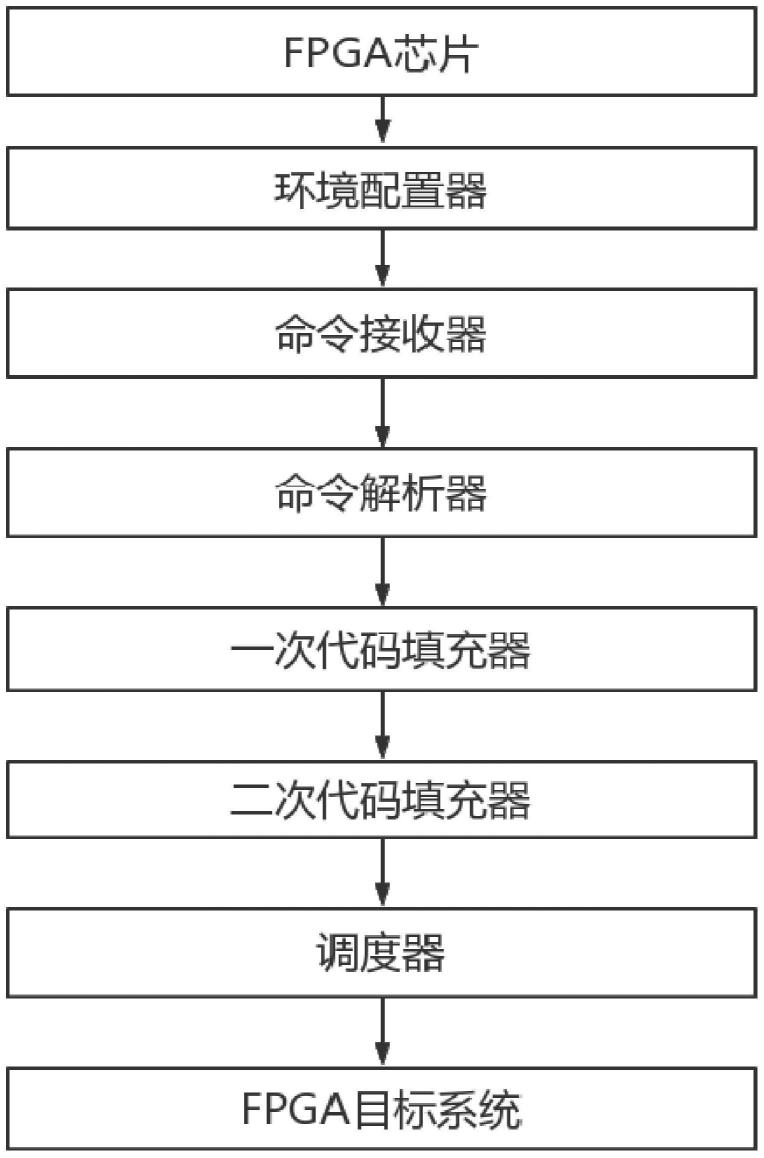

23.图1为本发明系统编译处理流程示意图。

具体实施方式

24.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

25.为了使本发明的目的、技术方案进行清楚、完整地描述,及优点更加清楚明白,以下结合附图对本发明实施例进行进一步详细说明。应当理解,此处所描述的具体实施例是本发明一部分实施例,而不是全部的实施例,仅仅用以解释本发明实施例,并不用于限定本

发明实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

26.在本发明的描述中,需要说明的是,术语“中心”、“中”、“上”、“下”、“左”、“右”、“内”、“外”、“顶”、“底”、“侧”、“竖直”、“水平”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。此外,术语“一”、“第一”、“第二”、“第三”、“第四”、“第五”、“第六”仅用于描述目的,而不能理解为指示或暗示相对重要性。

27.在本发明的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本发明中的具体含义。

28.出于简明和说明的目的,实施例的原理主要通过参考例子来描述。在以下描述中,很多具体细节被提出用以提供对实施例的彻底理解。然而明显的是,对于本领域普通技术人员,这些实施例在实践中可以不限于这些具体细节。在一些实例中,没有详细地描述公知方法和结构,以避免无必要地使这些实施例变得难以理解。另外,所有实施例可以互相结合使用。

29.请参阅图1,本发明提供一种技术方案:一种基于fpga芯片的人工智能编译技术管理系统,基于fpga芯片的人工智能编译技术管理系统包括fpga 芯片,以及配置在fpga芯片上的环境配置器、命令接收器、命令解析器、一次代码填充器、二次代码填充器、调度器和fpga目标系统,环境配置器用于配置编译环境所需的参数设置,命令接收器用于接受用户的编译指令,命令解析器用于对命令接收器接受到的编译指令进行解析处理,代码填充器用于对命令解析器解析获取的数据进行输出,并获取用户源程序路径,读取源码并根据其中宏定义识别fpga目标系统,并填充补全fpga目标系统相关的代码,得到针对fpga目标系统的一次填充源码,二次代码填充器通过对一次填充源码文件进行再处理,根据模态类型采用标准的vlan封装自定义vlan包头,填充到解析数据包代码部分,并输出二次填充源码文件,调度器用于实现编译调度和执行调度功能,fpga目标系统包括不少于两个fpga目标子系统。

30.一次代码填充器包括一次预处理识别器和一次接口定义器,一次预处理识别器用于根据命令解析器的输出,获取用户源程序路径,读取源码并根据其中宏定义识别fpga目标系统,并填充补全fpga目标系统相关的代码,输出针对这些fpga目标系统的一次填充源码。

31.二次代码填充器包括二次预处理识别器和二次接口定义器,二次接口定义器用于对一次预处理识别器输出的一次填充源码文件再处理,根据模态类型采用标准的vlan封装自定义vlan包头,填充到解析数据包代码部分,并输出二次填充源码文件。

32.调度器包括编译调度器和执行调度器,编译调度器用于编译调度,执行调度器用于执行调度。

33.编译调度器用于编译调度,编译调度具体为,将二次接口定义器输出的二次填充

源码文件传输到fpga目标系统上,依次启动fpga目标系统进行分布式编译。

34.编译调度器在启动fpga目标系统进行分布式编译时,按照fpga目标系统的处理性能由低到高启动。

35.执行调度器用于执行调度,执行调度具体为,将接收目标相关的后端编译器输出的可运行的目标文件与配置文件,依次将可运行的目标文件与配置文件分发到fpga目标系统中对应的目标子系统的运行环境中。

36.fpga目标系统的每个目标子系统均包括与目标相关的前端编译器、中端编译器、后端编译器以及与目标相关的运行环境;fpga目标系统用于编译处理用户模态数据。

37.fpga目标系统包括基于cpu的目标子系统、基于asic的目标子系统和基于fpga的目标子系统;

38.通过设置包括fpga芯片,和配置在fpga芯片上的环境配置器、命令接收器、命令解析器、一次代码填充器、二次代码填充器、调度器、fpga目标系统组合构成的fpga芯片人工智能编译技术管理系统,其通过软硬件协同编译系统支持用户实现安全自定义的灵活编程,并对ip模态的数据包进行加密处理的加密算法和对数据认证的算法进行配置和封装如ipsec,实现对敏感数据的安全性进行加固,并且本发明的软硬件协同编译处理方法及系统支持用户实现转发自定义的灵活编程,如用户通过编程,实现组播和vlan标签。

39.尽管上面对本技术说明性的具体实施方式进行了描述,以便于本技术领域的技术人员能够理解本技术,但是本技术不仅限于具体实施方式的范围,对本技术领域的普通技术人员而言,只要各种变化只要在所附的权利要求限定和确定的本技术精神和范围内,一切利用本技术构思的申请创造均在保护之列。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1