门级电路的并行仿真方法、系统、存储介质及设备

1.本发明涉及仿真技术领域,特别涉及一种门级电路的并行仿真方法、系统、存储介质及设备。

背景技术:

2.在高端数字ic产业中,门级电路仿真是关键技术。而随着集成电路规模的极大发展,现今的芯片设计已经达到万亿门级的集成度,日趋增加的系统复杂性使得仿真验证时间不断增加,并且对处理器、内存等计算资源的需求也随之增长,加之单机处理能力和计算资源的增长有限,因此传统的仿真验证方法已经难以满足目前芯片系统的规模及复杂度。

3.目前,传统的门级仿真技术存在如下几个很明显的缺陷:大多只能实现串行或部分并行门级仿真,导致仿真验证周期过长,研究表明,现有的仿真消耗的时间占整个计算机硬件系统设计周期的50%以上,这已成为大规模、复杂计算机系统设计过程中的一大痛点;有些仿真器虽然能实现对门级电路的高并行加速,但只能针对特定的门级电路结构,无法适配所有门级电路结构;不具备可扩展性,只能在特定的硬件平台上进行实行仿真。因此,急需提供一种快速高效的门级电路的仿真技术来解决这些难题。

技术实现要素:

4.基于此,本发明的目的是提出一种门级电路的并行仿真方法、系统、存储介质及设备,以解决上述提到的问题。

5.根据本发明提出的门级电路的并行仿真方法,所述方法包括:对电路结构文件中各门节点的网络的状态及各主输入门节点的输入进行赋初始值以得到各网络的状态初始值及各主输入门节点的初始激励值;从电路激励文件中获取对各主输入门节点施加的激励信号值,并将对各主输入门节点施加的激励信号值与其初始激励值进行对比以判断各主输入门节点的激励信号是否发生变化;若主输入门节点的激励信号发生变化,则对与主输入门节点的输出端连接的网络的状态值进行求解,并将求解后的网络的状态值与其对应的状态初始值进行对比以判断网络的状态是否发生变化,若网络的状态发生变化,则创建与网络相关的网表事件并加入到事件队列中;若不再产生新的网表事件,则对所述事件队列中的所有网表事件进行并行处理以同时将与各网表事件对应的网络的状态值赋予其输入端与网络连接的门节点,并将被赋值的门节点依次加入到门队列中,及将处理后的网表事件调出所述事件队列,直至所述事件队列变为空;判断所述门队列是否为空,若所述门队列不为空,则对所述门队列中的所有门节点进行并行仿真求解以得到各门节点的新的输出值,并将门节点的新的输出值与其旧的输出值进行对比以判断门节点的输出是否发生变化,若门节点的输出发生变化,则为与门节

点的输出端连接的网络创建一个网表事件,并将网表事件加入到事件队列中,及将相应的门节点调出所述门队列,直至所述门队列变为空;判断所述事件队列是否为空,若所述事件队列为空,则结束仿真。

6.综上,根据上述的门级电路的并行仿真方法,对电路结构文件中各个门节点连接的网络状态及各主输入节点的输入进行赋初始值,再从电路激励文件中获取各主输入门节点的激励信号,与其初始激励信号进行对比,若发生变化,则根据因变化的激励信号引起的网络状态的变化创建新的网表事件并加入到事件队列中,再对事件队列中的所有网表事件进行并行处理,以将网表事件对应的网络的状态值赋予相关联的门节点,并将该门节点加入到门队列中进行调度,门队列中各个门节点的电路求解逻辑相同,可以同时并行执行,本发明对事件队列中的所有网表事件及门队列中的门节点均采用并行处理,极大的提高了仿真速率及效率,能够对大规模门级电路的仿真实现高并行加速,且相对于串行仿真,该双队列结构能够减少仿真过程中对不必要门(输出值没有发生变化的门)的计算,降低了仿真算法的复杂度及计算次数,进一步提高了仿真速率及效率,且仿真过程由门队列与事件队列交替处理完成,能够避免事件的遗漏,以保证仿真的准确、有序执行。

7.进一步地,所述判断所述事件队列是否为空的步骤后还包括:若所述事件队列不为空,则对所述事件队列中的所有网表事件进行并行处理以同时将与各网表事件对应的网络的状态值赋予其输入端与网络连接的门节点,并将被赋值的门节点依次加入到门队列中,及将处理后的网表事件调出所述事件队列,直至所述事件队列变为空;判断所述门队列是否为空,若所述门队列为空,则结束仿真。

8.进一步地,所述若门节点的输出发生变化,则为与门节点的输出端连接的网络创建一个网表事件的步骤包括:若门节点的输出发生变化,则从所述电路结构文件中获取与门节点的输出端连接的网络的标签和状态值,并根据网络的标签和状态值创建一个网表事件。

9.进一步地,所述对所述事件队列中的所有网表事件进行并行处理以同时将与各网表事件对应的网络的状态值赋予其输入端与网络连接的门节点的步骤包括:获取所述事件队列中的所有网表事件的信息,所述网表事件的信息包括与网表事件对应的网络的标签和状态值;根据与网表事件对应的网络的标签在所述电路结构文件中进行查找以获取其输入端与网络连接的门节点的输入节点标签和输入端口号;将与网表事件对应的网络的状态值赋予其输入端与网络连接的门节点的输入端口号上;所述将被赋值的门节点依次加入到门队列中的步骤包括:判断输入端口被赋值的门节点是否存在于所述门队列中;若输入端口被赋值的门节点不存在于所述门队列中则将其调入所述门队列中。

10.进一步地,所述对电路结构文件中各门节点的网络的状态及各主输入门节点的输入进行赋初始值以得到各网络的状态初始值及各主输入门节点的初始激励值的步骤前还包括:加载及解析输入的电路结构文件,并将所述电路结构文件中输入类型为常量的门

节点加入到门队列中。

11.进一步地,所述将所述电路结构文件中输入类型为常量的门节点加入到门队列中的步骤包括:判断所述电路结构文件中各门节点的输入类型是否为常量;若门节点的输入类型为常量,则将门节点加入到所述门队列之中,并将门节点的输入的字符串类型转化为bit类型及在所述电路结构文件中进行更新。

12.进一步地,所述对电路结构文件中各门节点的网络的状态及各主输入门节点的输入进行赋初始值以得到各网络的状态初始值及各主输入门节点的初始激励值的步骤前还包括:加载及解析输入的电路激励文件,并将所述电路激励文件中被施加激励信号的主输入门节点加入到门队列中。

13.本发明还提供一种门级电路的并行仿真系统,包括:初始化赋值模块:用于对电路结构文件中各门节点的网络的状态及各主输入门节点的输入进行赋初始值以得到各网络的状态初始值及各主输入门节点的初始激励值;激励读取模块:用于从电路激励文件中获取对各主输入门节点施加的激励信号值,并将对各主输入门节点施加的激励信号值与其初始激励值进行对比以判断各主输入门节点的激励信号是否发生变化;新事件生成模块:用于若主输入门节点的激励信号发生变化,则对与主输入门节点的输出端连接的网络的状态值进行求解,并将求解后的网络的状态值与其对应的状态初始值进行对比以判断网络的状态是否发生变化,若网络的状态发生变化,则创建与网络相关的网表事件并加入到事件队列中;事件队列处理模块:用于若不再产生新的网表事件,则对所述事件队列中的所有网表事件进行并行处理以同时将与各网表事件对应的网络的状态值赋予其输入端与网络连接的门节点,并将被赋值的门节点依次加入到门队列中,及将处理后的网表事件调出所述事件队列,直至所述事件队列变为空;门队列并行处理模块:用于判断所述门队列是否为空,若所述门队列不为空,则对所述门队列中的所有门节点进行并行仿真求解以得到各门节点的新的输出值,并将门节点的新的输出值与其旧的输出值进行对比以判断门节点的输出是否发生变化,若门节点的输出发生变化,则为与门节点的输出端连接的网络创建一个网表事件,并将网表事件加入到事件队列中,及将相应的门节点调出所述门队列,直至所述门队列变为空;仿真调度模块:用于判断所述事件队列是否为空,若所述事件队列为空,则结束仿真。

14.本发明还提出一种计算机可读存储介质,其上存储有计算机程序,该程序被处理器执行时实现上述的门级电路的并行仿真方法。

15.本发明还提出一种门级电路的并行仿真设备,包括存储器、处理器以及存储在存储器上并可在处理器上运行的计算机程序,所述处理器执行所述程序时实现上述的门级电路的并行仿真方法。

16.本发明的附加方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本发明的实施例了解到。

附图说明

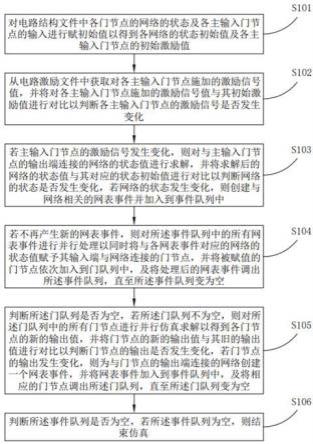

17.本发明的上述和/或附加的方面和优点从结合下面附图对实施例的描述中将变得明显和容易理解,其中:图1为本发明第一实施例门级电路的并行仿真方法的流程图;图2为本发明第二实施例门级电路的转译方法的流程图;图3为本发明第三实施例门级电路的并行仿真系统的系统框图;图4为本发明第四实施例门级电路的并行仿真设备的第一结构示意图;图5为本发明第四实施例门级电路的并行仿真设备的第二结构示意图。

具体实施方式

18.为了便于理解本发明,下面将参照相关附图对本发明进行更全面的描述。附图中给出了本发明的若干实施例。但是,本发明可以以许多不同的形式来实现,并不限于本文所描述的实施例。相反地,提供这些实施例的目的是使对本发明的公开内容更加透彻全面。

19.需要说明的是,当元件被称为“固设于”另一个元件,它可以直接在另一个元件上或者也可以存在居中的元件。当一个元件被认为是“连接”另一个元件,它可以是直接连接到另一个元件或者可能同时存在居中元件。本文所使用的术语“垂直的”、“水平的”、“左”、“右”以及类似的表述只是为了说明的目的。

20.除非另有定义,本文所使用的所有的技术和科学术语与属于本发明的技术领域的技术人员通常理解的含义相同。本文中在本发明的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本发明。本文所使用的术语“及/或”包括一个或多个相关的所列项目的任意的和所有的组合。

21.实施例1请参阅图1,本发明提出一种门级电路的并行仿真方法,该方法包括步骤s101至s106:s101,对电路结构文件中各门节点的网络的状态及各主输入门节点的输入进行赋初始值以得到各网络的状态初始值及各主输入门节点的初始激励值。

22.在对电路结构文件中各门节点的网络的状态及各主输入门节点的输入进行赋初始值以得到各网络的状态初始值及各主输入门节点的初始激励值之前,还需要加载及解析输入的电路结构文件,并将所述电路结构文件中输入类型为常量的门节点加入到门队列中。具体步骤为:判断所述电路结构文件中各门节点的输入类型是否为常量;若门节点的输入类型为常量,则将门节点加入到所述门队列之中,并将门节点的输入的字符串类型转化为bit类型及在所述电路结构文件中进行更新。

23.需要说明的是,本发明实施例中的网络连接在各门节点之间,而网络的状态用于表示两个门节点之间的连接关系,网络的状态值等于输出端与其连接的门节点的输出值,所述电路结构文件包含json格式的非自定义节点的全局电路信息字典和json格式的自定义节点的全局电路信息字典,将所述电路结构文件作为输入文件放置在目标项目工程的.exe 可执行文件的同级目录下,其中,所述电路结构文件中包含自定义的电路结构信息,所述.exe可执行文件中包含加载所述输入文件的命令行,例如:./glsimtor.exe

‑‑

filecircuit=multiplier_16.json。

24.所述电路结构文件加载完成后,再对所述电路结构文件进行解析:首先判断所述电路结构文件是否能够正确打开,若不能正确打开,则结束程序并输出解析出错的提示信息,若能正确打开,则对电路结构文件进行检测并判断所述电路结构文件中的门节点的类型是否加载正确,若加载不正确,则结束程序并输出解析出错的提示信息,若加载正确,则对所述电路结构文件中的数据进行加载。

25.进而对所述电路结构文件中的数据进行加载:检测并判断所述电路结构文件中各门节点的输入类型是否为常量(const_vec4),若门节点的输入类型是常量,则将门节点的输入的字符串类型转化为bit类型并在电路结构文件中进行更新,并将输入类型是常量的门节点调入门队列之中,若门节点的输入类型不是常量,则将门节点的输入定义为变量x。

26.在对电路结构文件中各门节点的网络的状态及各主输入门节点的输入进行赋初始值以得到各网络的状态初始值及各主输入门节点的初始激励值之前,还需要加载及解析输入的电路激励文件,并将所述电路激励文件中被施加激励信号的主输入门节点加入到门队列中。具体步骤为:判断所述电路激励文件中被施加激励信号的各主输入门节点是否存在于所述电路结构文件中;若被施加激励信号的主输入门节点存在于所述电路结构文件中,则主输入门节点加入到所述门队列中。

27.需要说明的是,加载电路激励文件:将所述电路激励文件作为输入文件放置在目标项目工程的.exe 可执行文件的同级目录下,其中,所述电路激励文件中包含自定义的电路激励信息,所述.exe 可执行文件中包含加载所述输入文件的命令行,如:./glsimtor.exe

ꢀ‑‑

signalfile=input_signal.ini。

28.判断所述电路激励文件中的各激励信号对应的门节点是否存在于电路结构文件中,若所述激励信号对应的门节点存在于电路结构文件中,则将所述激励信号对应的门节点的名称及值保存在预仿真事件变量中以生成相应的预仿真事件;将所有的预仿真事件存储至预仿真事件容器中,并对预仿真事件容器中的预仿真事件进行遍历以加入到门队列容器中。

29.s102,从电路激励文件中获取对各主输入门节点施加的激励信号值,并将对各主输入门节点施加的激励信号值与其初始激励值进行对比以判断各主输入门节点的激励信号是否发生变化。

30.s103,若主输入门节点的激励信号发生变化,则对与主输入门节点的输出端连接的网络的状态值进行求解,并将求解后的网络的状态值与其对应的状态初始值进行对比以判断网络的状态是否发生变化,若网络的状态发生变化,则创建与网络相关的网表事件并加入到事件队列中。

31.s104,若不再产生新的网表事件,则对所述事件队列中的所有网表事件进行并行处理以同时将与各网表事件对应的网络的状态值赋予其输入端与网络连接的门节点,并将被赋值的门节点依次加入到门队列中,及将处理后的网表事件调出所述事件队列,直至所述事件队列变为空。

32.具体的,所述若门节点的输出发生变化,则为与门节点的输出端连接的网络创建一个网表事件的步骤包括:若门节点的输出发生变化,则从所述电路结构文件中获取与门节点的输出端连接的网络的标签和状态值,并根据网络的标签和状态值创建一个网表事件。

33.进一步地,所述对所述事件队列中的所有网表事件进行并行处理以同时将与各网表事件对应的网络的状态值赋予其输入端与网络连接的门节点的步骤包括:获取所述事件队列中的所有网表事件的信息,所述网表事件的信息包括与网表事件对应的网络的标签和状态值;根据与网表事件对应的网络的标签在所述电路结构文件中进行查找以获取其输入端与网络连接的门节点的输入节点标签和输入端口号;将与网表事件对应的网络的状态值赋予其输入端与网络连接的门节点的输入端口号上;所述将被赋值的门节点依次加入到门队列中的步骤包括:判断输入端口被赋值的门节点是否存在于所述门队列中;若输入端口被赋值的门节点不存在于所述门队列中则将其调入所述门队列中。

34.需要说明的是,对事件队列中的网表事件进行仿真求解时,通过节点操作指针指向与网表事件对应的网络的标签,根据该标签信息在电路结构文件中查找获取其输入端与当前网络连接的门节点的输入节点标签和输入端口号,并存储至targetnodevec容器中。

35.再通过临时变量outfuninput从targetnodevec容器中获取当前for循环迭代次数下的其输入端与当前网络连接的门节点的输入节点标签和输入端口号,如autooutfuninput = targetnodevec[j],则表明通过临时变量outfuninput从targetnodevec容器中获取当前第j次循环下的其输入端与当前网络连接的门节点的输入节点标签和输入端口号,再通过其输入端与当前网络连接的门节点的标签在电路结构文件中找到相应门节点,并将节点操作指针指向该门节点,由节点操作指针调用赋值函数以将当前网表事件中的当前网络的状态值netvalue赋值到其输入端与当前网络连接的门节点的输入端口上。

[0036]

然后对其输入端与当前网络连接的门节点的标志位进行检测,如果该门节点的标志位为false,则说明该门节点没有被调入到门队列中,则将该门节点插入到全局的门队列之中,并将该门节点的标志位更改为true。

[0037]

s105,判断所述门队列是否为空,若所述门队列不为空,则对所述门队列中的所有门节点进行并行仿真求解以得到各门节点的新的输出值,并将门节点的新的输出值与其旧的输出值进行对比以判断门节点的输出是否发生变化,若门节点的输出发生变化,则为与门节点的输出端连接的网络创建一个网表事件,并将网表事件加入到事件队列中,及将相应的门节点调出所述门队列,直至所述门队列变为空。

[0038]

需要说明的是,本发明实施例为电路结构中的每个门节点均设置一标志位,若所述门节点加入所述门队列,则将所述门节点的标志位置为true,若所述门节点从所述门队列中出来,则将所述门节点的标志位置为false。因此,可以根据所述门节点的标志位来判断所述门节点是否存在于所述门队列中。

[0039]

需要进一步说明的是,用来对所述门队列中的门事件处理的模块为门事件处理模块,在所述门队列中,一个门节点对应一个门事件,对门事件的处理即为对门节点的仿真求解,门事件处理模块内定义有并行循环块,如::#pragma omp parallel for,通过并行循环块设置一个执行次数为门队列长度的循环来遍历整个门队列,对门队列中的门节点进行仿真求解,直到门队列为空,循环结束。

[0040]

对门队列执行仿真操作:使用一个临时字符串变量来取出当前循环下执行的门事件的标签,如果标签是空值,则跳过本轮循环,如果标签不为空值,则再调用一个预定义的功能函数来获取与当前门节点的输出端对接的所有门节点的相关输入信息(输入端口号及输入节点标签),并使用一个临时变量vecoutnode来保存,然后调用预定义的仿真计算函数来进行逻辑运算仿真以得到当前门节点的最新输出值并将当前门节点的最新输出值存储至bit变量容器中,再使用一个全局键值对来保存在这次仿真过程中进行了运算的当前门节点的信息,其键为当前门节点的标签,其值为由bit变量容器中提取的bit变量转换为当前门节点最新的输出值newoutval。

[0041]

再通过bool型的函数vecvaleeq()对输入参数进行比对,该函数的输入参数为两个bit变量容器,其中一个bit变量容器存储有当前门节点最新的输出值newoutval,另一个bit变量容器存储有当前门节点的上一个输出值oldoutval,如果两个 bit变量容器中的bit 流不相同则创建一个新的网表事件并加入事件队列,并将指向该事件的指针填入到临时容器tempnetqueue的对应位置上。

[0042]

s106,判断所述事件队列是否为空,若所述事件队列为空,则结束仿真。

[0043]

若所述事件队列不为空,则对所述事件队列中的所有网表事件进行并行处理以同时将与各网表事件对应的网络的状态值赋予其输入端与网络连接的门节点,并将被赋值的门节点依次加入到门队列中,及将处理后的网表事件调出所述事件队列,直至所述事件队列变为空;判断所述门队列是否为空,若所述门队列为空,则结束仿真。

[0044]

需要说明的是,本发明实施例在所述门队列为空后再立即对所述事件队列中的事件进行处理,在所述事件队列为空后再立即对所述门队列中的事件进行处理,交替进行,直至所述门队列与所述事件队列中的事件均处理完,均为空,这样就能够避免事件的遗漏,保证仿真的准确性及有序性,在对所述门队列中的门节点进行仿真求解时,可以所有门节点同时并行仿真求解,在对所述事件队列中的网表事件进行处理时,也可以所有网表事件同时并行处理,这样可以大大提高仿真效率,实现对大规模门级电路仿真的高并行加速。

[0045]

本发明实施例的门级电路仿真相对于串行仿真能实现3~5倍的初步加速,后期还有不断提升空间。同时扩展性及适配性良好,支持多种并行通用技术和特定硬件平台上实现:例如众核服务器、gpu等多种硬件上。

[0046]

综上,根据上述的门级电路的并行仿真方法,对电路结构文件中各个门节点连接的网络状态及各主输入节点的输入进行赋初始值,再从电路激励文件中获取各主输入门节点的激励信号,与其初始激励信号进行对比,若发生变化,则根据因变化的激励信号引起的网络状态的变化创建新的网表事件并加入到事件队列中,再对事件队列中的所有网表事件进行并行处理,以将网表事件对应的网络的状态值赋予相关联的门节点,并将该门节点加入到门队列中进行调度,门队列中各个门节点的电路求解逻辑相同,可以同时并行执行,本发明对事件队列中的所有网表事件及门队列中的门节点均采用并行处理,极大的提高了仿真速率及效率,能够对大规模门级电路的仿真实现高并行加速,且相对于串行仿真,该双队列结构能够减少仿真过程中对不必要门(输出值没有发生变化的门)的计算,降低了仿真算法的复杂度及计算次数,进一步提高了仿真速率及效率,且仿真过程由门队列与事件队列交替处理完成,能够避免事件的遗漏,以保证仿真的准确、有序执行。

[0047]

实施例2如图2所示,本实施例为门级电路的转译方法,用于将门级网表文件转译得到第一实施例中的电路结构文件,包括步骤s201~s205。

[0048]

s201,根据目标门级网表文件与工艺库文件生成vvp文件,所述目标门级网表为用于描述各电路器件之间连接关系的门级语义的文本文件,所述工艺库文件中包含了组成各电路器件的逻辑元件,所述vvp文件为用于描述各节点的逻辑元件之间连接关系的门级语义的文本文件。

[0049]

需要说明的是,本发明实施例中的vvp文件可以通过icarus verilog仿真器生成,icarus verilog仿真器在仿真电路文件时便会产生中间文件vvp文件,vvp文件的格式为test.vvp。

[0050]

在根据目标门级网表文件与工艺库文件生成vvp文件的步骤前需要先选取的目标门级网表文件及工艺库文件,选取的目标门级网表文件的格式可以为:test.v(.v后缀为verilog文件),选取的工艺库文件的格式可以为:smic_13.v。在使用icarus verilog仿真器生成vvp文件时,输入如下命令“iverilog

ꢀ‑

o test.vvptest.v smic_13.v”便可以生成vvp文件test.vvp。

[0051]

s202,从命令行输入vvp文件名及所述目标门级网表文件的顶层模块名并将所述顶层模块名设置为全局变量。

[0052]

其中,顶层模块名如:top_module。

[0053]

s203,获取预设逻辑关键字表,根据所述全局变量及所述预设逻辑关键字表中的各逻辑关键字的索引对所述vvp文件进行解析并提取与各所述逻辑关键字对应的节点的门级关键信息。

[0054]

需要说明的是,工艺库特定的工艺器件无非是由以下几种基本逻辑器件组成:与(and)或(or)非(not)、用户自定义原语udp、路径延时及器件延时、延时单位等,因此只需要在vvp文件当中依序查找并提取这些逻辑器件的关键门级信息(门级语言)进行提取即可,而逻辑器件在vvp文件中由相应的逻辑关键字进行体现,便可借由这些逻辑关键字来查找提取关键门级信息,本发明实施例根据需要涉及到的逻辑关键字预先制作一个逻辑关键字表,再对应预设逻辑关键字表在vvp文件中进行对应查找提取信息,下表1为预设逻辑关键字表。

[0055]

表1进一步的,所述根据所述全局变量及所述预设逻辑关键字表中的各逻辑关键字的

索引对所述vvp文件进行解析并提取与各所述逻辑关键字对应的节点的门级关键信息的步骤具体包括:从所述vvp文件的文件头开始依次读取所述vvp文件中的每一行信息并查询行信息中是否存在顶层模块;若不存在顶层模块,则判断所述vvp文件中的行信息中是否存在组合逻辑udp关键字或时序逻辑udp关键字;若存在所述组合逻辑udp关键字或所述时序逻辑udp关键字,则对组合逻辑udp或时序逻辑udp的相关段进行解析,并对与所述组合逻辑udp关键字或所述时序逻辑udp关键字对应的节点的真值表及门级关键信息进行提取及存储至第一全局字典udp_definitions中。

[0056]

具体的,若出现.udp关键字,则从出现.udp关键字的行(开始行)开始进行解析,并解析至分号结尾行(结束行)。若解析出的节点信息中包含具体的关键字:.udp/comb(即组合逻辑udp关键字)或.udp/sequ(即时序逻辑udp关键字),则将解析出的节点信息对应存储至第一全局字典udp_definitions中,解析出的节点信息还包含udp节点的实例名(即节点id,如udp_udp_mux2)、udp节点的类型名(如udp_mux2)、udp节点的初始值(0表示信号0,1表示信号1,2表示信号x,3表示无信号值)。

[0057]

进一步的,所述从所述vvp文件的文件头开始依次读取所述vvp文件中的每一行信息并查询行信息中是否存在顶层模块的步骤后还包括:若存在顶层模块,则对所述vvp文件中顶层模块后面的所有行信息进行解析并根据所述预设逻辑关键字表中的其它逻辑关键字对与所述其它逻辑关键字对应的门级关键信息进行提取及存储至全局列表gate_statements中,所述其它逻辑关键字为所述预设逻辑关键字表中除组合逻辑udp关键字及时序逻辑udp关键字以外的逻辑关键字。

[0058]

s204,根据与各所述逻辑关键字对应的重定义规则对与各所述逻辑关键字对应的节点的门级关键信息进行门级语义的重定义以得到重定义后的各节点的门级关键信息。

[0059]

进一步的,所述根据与各所述逻辑关键字对应的重定义规则对与各所述逻辑关键字对应的节点的门级关键信息进行门级语义的重定义以得到重定义后的各节点的门级关键信息的步骤具体包括:创建第二全局字典gate_dict;对所述全局列表gate_statements进行遍历并依序获取所述全局列表gate_statements中各节点的门级关键信息的字符串;对各节点的门级关键信息的字符串进行解析并提取各节点的门级关键信息的关键字;将各节点的门级关键信息的关键字对照所述预设逻辑关键字表进行匹配查询以在所述预设逻辑关键字表中找到对应的逻辑关键字并根据所述逻辑关键字确定各节点的类型及各节点的门级关键信息的重定义规则;根据各节点的门级关键信息的重定义规则及各节点的门级关键信息设置第二全局字典gate_dict的键及值。

[0060]

进一步的,所述根据各节点的门级关键信息的重定义规则及各节点的门级关键信息设置第二全局字典gate_dict的键及值的步骤具体包括:

若所述节点为基本逻辑门节点,则按照四输入一输出的门级定义规则及所述节点的门级关键信息对所述第二全局字典gate_dict的键及值进行设定。

[0061]

进一步的,所述按照四输入一输出的门级定义规则及所述节点的门级关键信息对所述第二全局字典gate_dict的键及值进行设定的步骤具体包括:从所述节点的门级关键信息中提取节点id、节点的类型名、节点的输入id、节点的输出id和节点的输出位宽;将所述节点id存入至所述第二全局字典gate_dict的键中;将所述节点的类型名存入至所述第二全局字典gate_dict的值的类型列表中;将所述节点的输入id和常数值依次存入至所述第二全局字典gate_dict的值的四输入列表中;将所述节点的输出id存入至所述第二全局字典gate_dict的值的输出列表中;将所述节点的输出位宽存入至所述第二全局字典gate_dict的值的位宽列表中。

[0062]

需要说明的是,所述vvp文件包含的节点类型至少有:信号类型节点、逻辑仿真节点和门级信号连接节点,其中,所述逻辑仿真节点又具体包含基本逻辑门节点与udp节点(用户自定义节点)。

[0063]

所述基本逻辑门节点是数字电路中的常用逻辑门,所有类型如表2所示,一般基本逻辑门节点多为二输入一输出(如与、或、非门),少部分基本逻辑门节点为三输入一输出(如cmos),而在门级仿真过程中可能需要加入一些其它的功能,如在与门的门级仿真过程中需要加入调试接口和逻辑锁功能,而二输入的与门结构便无法满足仿真要求,因此vvp文件对于一些基本逻辑门节点存在门级电路语义描述不足的问题,需要对基本逻辑门节点的门级关键信息进行定义以满足实际仿真需求。本发明实施例为了保证输入输出的拓扑结构与门结构一致,将基本逻辑门节点统一定义为四输入单输出。而其中没有用到的输入门则引入不同的常量值,使其生成的逻辑表与原有二输入逻辑真值表的含义相同。n_func_andn_func_orn_func_nandn_func_norn_func_xnorn_func_xorn_func_notn_func_notif0n_func_notif1n_func_bufif0n_func_bufif1n_func_cmosn_func_nmosn_func_pmosn_func_rcmosn_func_rnmosn_func_rpmos

……

[0064]

表2门级网表文件是rtl文件经过综合之后生成的用于表征底层电路连接关系的文件,由于综合软件无法对udp语法进行综合,因此,从rtl文件综合生成的门级网表文件一般不含有用户自定义原语udp,而在进行门级仿真中工艺库器件内部往往会使用udp节点,udp大致分为两类组合udp与时序udp。由于udp节点的处理较为复杂,大部分现有仿真器无法支持门级仿真中出现udp的情况,主要有两大难点:1、udp节点定义多种多样,逻辑真值表较为复杂难以进行处理;2、仿真用户自定义udp门实现难度大,无法保证组合逻辑及时序逻辑正确。

[0065]

本发明实施例参考vvp文件中对udp节点的语义描述及实际仿真情况,对udp节点进行了如下定义来解决上述难点:多输入单输出、输入位宽均为1bit、输入端口数量为udp

真值表列数-1,真值表最右边一列为输入匹配后的输出结果值。定义方式如下:若所述节点为udp节点,则按照多输入单输出的门级定义规则及所述节点的门级关键信息对所述第二全局字典gate_dict的键及值进行设定,具体步骤包括:从所述节点的门级关键信息中提取节点id、节点的类型名、节点的输入值、节点的输出值和节点的真值表列数;将所述节点id存入至所述第二全局字典gate_dict的键中;将所述节点的类型名存入至所述第二全局字典gate_dict的值的类型列表中;根据所述节点的真值表列数构建所述第二全局字典gate_dict的值的输入列表,并将所述节点的输入值依次存入至所述第二全局字典gate_dict的值的输入列表中,其中,所述第二全局字典gate_dict的值的输入列表的列数为所述节点的真值表列数减1;将所述节点的输出值存入至所述第二全局字典gate_dict的值的输出列表中;将1bit存入至对所述第二全局字典gate_dict的值的输入位宽列表中。

[0066]

所述信号类型节点主要起到提供指定信号的作用,可以给予电路初始值。该类型的节点主要有以下三种:n_var、n_func_buft和n_func_bufz。信号类型节点主要为单输入单输出,通常门级电路中需要常值为x的信号则用到n_var,其它值的信号则用到n_func_buft与n_func_bufz,其中,n_func_buft可以传递信号的强度信息,n_func_bufz 忽略信号的强度信息。

[0067]

除了上面介绍的具有仿真功能的节点之外,本发明中需要重定义的节点类型还有一种表征门级连接关系的节点。此类型节点能够起到各个节点信号连接及选择的作用,包括信号位选节点(n_vpart_sel)与信号合并节点(n_concat8、n_concat)。

[0068]

信号合并节点主要起到多个信号值的合并作用,该节点为四输入单输出节点,可以将四个输入上的多比特信号进行合并,其中,n_concat8信号合并节点会传递信号强度信息,n_concat信号合并节点会忽略强度信息。信号位选节点为单输入单输出节点,根据给定的位选起始下标和输出位宽来确定输出信号。

[0069]

定义方式为:若所述节点为信号合并节点,则从所述节点的门级关键信息中提取节点id、节点的每个输入信号的输出位宽和节点的输入信号值;将所述节点id存入至所述第二全局字典gate_dict的键中;将所述节点的输入信号值依次存入至所述第二全局字典gate_dict的值的输入列表中;对所述节点的输入信号值依序进行合并以得到节点的输出信号值,并将所述节点的输出信号值存入至所述第二全局字典gate_dict的值的输出列表中;将所述节点的每个输入信号的输出位宽依次存入至对所述第二全局字典gate_dict的值的位宽列表中。

[0070]

s205,对重定义后的各节点的门级关键信息以预设通用格式进行转译以得到电路结构文件。

[0071]

其中,所述对重定义后的各节点的门级关键信息以预设通用格式进行转译以得到电路结构文件的步骤包括:对所述第二全局字典gate_dict进行遍历并将所述第二全局字典gate_dict中的信息进行json格式的转换以得到json格式的非自定义节点的全局电路信息字典;对所述第

一全局字典udp_definitions进行遍历并将所述第一全局字典udp_definitions中的信息进行json格式的转换以得到json格式的自定义节点的全局电路信息字典。预设通用格式还可以是protocol buffers格式。

[0072]

需要说明的是,通过前期对vvp文件中的每个节点的门级关键信息进行处理使得每个门都具有一个唯一的id,因此其对应的输入输出端口也都会拥有一个唯一的id。由于门级网表文件本身就含有连接关系,因此通过每个门的id及其输入输出id便可以组成一个有向图。该有向图中的每个节点相当于一个逻辑门,且此门并非单纯的数字电路的门而是前面重定义优化后的门。

[0073]

转译得到的电路结构文件(第一json文件和第二json文件)用于将电路表征为有向图,每一个图节点代表着一个门。每一个门有唯一的id属性用于查找其在有向图当中位置。而转译成json格式文件是由于 json格式文件的语法非常易于使用,而且轻量,能够以更快的方式执行响应,并且能够清晰地表示结构关系。json格式作为一种更好的互联网传输结构化文件格式,已经被各类联网或者单机软件使用,具有极强的通用性。

[0074]

实施例3请参阅图3,本发明还提出一种门级电路的并行仿真系统,该系统包括:初始化赋值模块:用于对电路结构文件中各门节点的网络的状态及各主输入门节点的输入进行赋初始值以得到各网络的状态初始值及各主输入门节点的初始激励值。

[0075]

所述初始化赋值模块还用于:加载及解析输入的电路结构文件,并将所述电路结构文件中输入类型为常量的门节点加入到门队列中。

[0076]

所述初始化赋值模块还用于:判断所述电路结构文件中各门节点的输入类型是否为常量;若门节点的输入类型为常量,则将门节点加入到所述门队列之中,并将门节点的输入的字符串类型转化为bit类型及在所述电路结构文件中进行更新。

[0077]

所述初始化赋值模块还用于:加载及解析输入的电路激励文件,并将所述电路激励文件中被施加激励信号的主输入门节点加入到门队列中。

[0078]

所述初始化赋值模块还用于:判断所述电路激励文件中被施加激励信号的各主输入门节点是否存在于所述电路结构文件中;若被施加激励信号的主输入门节点存在于所述电路结构文件中,则主输入门节点加入到所述门队列中。

[0079]

激励读取模块:用于从电路激励文件中获取对各主输入门节点施加的激励信号值,并将对各主输入门节点施加的激励信号值与其初始激励值进行对比以判断各主输入门节点的激励信号是否发生变化,将激励信号值发生变化的主输入设为目标主输入。

[0080]

新事件生成模块:用于若主输入门节点的激励信号发生变化,则对与主输入门节点的输出端连接的网络的状态值进行求解,并将求解后的网络的状态值与其对应的状态初始值进行对比以判断网络的状态是否发生变化,若网络的状态发生变化,则创建与网络相关的网表事件并加入到事件队列中。

[0081]

事件队列处理模块:用于若不再产生新的网表事件,则对所述事件队列中的所有网表事件进行并行处理以同时将与各网表事件对应的网络的状态值赋予其输入端与网络连接的门节点,并将被赋值的门节点依次加入到门队列中,及将处理后的网表事件调出所述事件队列,直至所述事件队列变为空。

[0082]

所述事件队列处理模块还用于:获取所述事件队列中的所有网表事件的信息,所述网表事件的信息包括与网表事件对应的网络的标签和状态值;根据与网表事件对应的网络的标签在所述电路结构文件中进行查找以获取其输入端与网络连接的门节点的输入节点标签和输入端口号;将与网表事件对应的网络的状态值赋予其输入端与网络连接的门节点的输入端口号上;判断输入端口被赋值的门节点是否存在于所述门队列中;若输入端口被赋值的门节点不存在于所述门队列中则将其调入所述门队列中。

[0083]

门队列并行处理模块:用于判断所述门队列是否为空,若所述门队列不为空,则对所述门队列中的所有门节点进行并行仿真求解以得到各门节点的新的输出值,并将门节点的新的输出值与其旧的输出值进行对比以判断门节点的输出是否发生变化,若门节点的输出发生变化,则为与门节点的输出端连接的网络创建一个网表事件,并将网表事件加入到事件队列中,及将相应的门节点调出所述门队列,直至所述门队列变为空。

[0084]

所述门队列并行处理模块还用于:若门节点的输出发生变化,则从所述电路结构文件中获取与门节点的输出端连接的网络的标签和状态值,并根据网络的标签和状态值创建一个网表事件。

[0085]

仿真调度模块:用于判断所述事件队列是否为空,若所述事件队列为空,则结束仿真。

[0086]

所述仿真调度模块还用于:若所述事件队列不为空,则对所述事件队列中的所有网表事件进行并行处理以同时将与各网表事件对应的网络的状态值赋予其输入端与网络连接的门节点,并将被赋值的门节点依次加入到门队列中,及将处理后的网表事件调出所述事件队列,直至所述事件队列变为空;判断所述门队列是否为空,若所述门队列为空,则结束仿真。

[0087]

实施例4请参考图4,本发明还提出一种门级电路的并行仿真设备,包括存储器20、处理器10以及存储在存储器上并可在处理器上运行的计算机程序30,所述处理器10执行所述计算机程序30时实现如上述的门级电路的并行仿真方法。

[0088]

其中,所述门级电路的并行仿真设备具体可以为计算机、服务器、上位机等,处理器10在一些实施例中可以是中央处理器(central processing unit, cpu)、控制器、微控制器、微处理器或其他数据处理芯片,用于运行存储器20中存储的程序代码或处理数据,例如执行访问限制程序等。

[0089]

其中,存储器20至少包括一种类型的可读存储介质,所述可读存储介质包括闪存、硬盘、多媒体卡、卡型存储器(例如,sd或dx存储器等)、磁性存储器、磁盘、光盘等。存储器20在一些实施例中可以是门级电路的并行仿真设备的内部存储单元,例如该门级电路的并行

仿真设备的硬盘。存储器20在另一些实施例中也可以是门级电路的并行仿真设备的外部存储装置,例如门级电路的并行仿真设备上配备的插接式硬盘,智能存储卡(smart media card, smc),安全数字(secure digital, sd)卡,闪存卡(flash card)等。进一步地,存储器20还可以既包括门级电路的并行仿真设备的内部存储单元也包括外部存储装置。存储器20不仅可以用于存储安装于门级电路的并行仿真设备的应用软件及各类数据,还可以用于暂时地存储已经输出或者将要输出的数据。

[0090]

需要指出的是,图4示出的结构并不构成对门级电路的并行仿真设备的限定,在其它实施例当中,该门级电路的并行仿真设备可以包括比图示更少或者更多的部件,或者组合某些部件,或者不同的部件布置,可参考图5,为对门级电路的并行仿真设备的进一步限定。

[0091]

本发明实施例还提出一种计算机可读存储介质,其上存储有计算机程序,该程序被处理器执行时实现如上述的门级电路的并行仿真方法。

[0092]

以上所述实施例仅表达了本发明的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对本发明范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。因此,本发明的保护范围应以所附权利要求为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1