考虑最大时延优化的FPGA布线方法

考虑最大时延优化的fpga布线方法

技术领域

1.本发明属于集成电路计算机辅助设计技术领域,具体涉及一种考虑最大时延优化的fpga布线方法。

背景技术:

2.逻辑验证在超大规模集成电路(very large scale integration circuit,vlsi)物理设计自动化中起着重要的作用。随着超大规模集成电路尺寸的快速增加,用于实现逻辑验证的时间变长,复制成本也越来越高。因此,对于现代先进的超大规模集成电路,需要一种有效的、可扩展的逻辑验证方法。现有的vlsi逻辑验证方法分为以下三类:(1)软件仿真方法、(2)硬件仿真方法和(3)现场可编程逻辑门阵列(field programmable gate array,fpga)原型设计方法。基于软件的模拟器是可视化的,并为vlsi开发人员提供了调试能力。然而,这样的模拟器需要在单个处理器上依次模拟所有的逻辑门,所以它的运行时间对于大型的vlsi设计来说太长了。与软件仿真相比,硬件仿真方法大大加快了电路的生成过程,但实施代价将会大大增加。现在因集成电路技术的发展,使用的芯片规模越来越大,之前所述的两种验证方法的劣势愈加明显。

3.目前,现场可编程逻辑门阵列已被广泛运用于云计算、人工智能中的深度学习和fpga原型系统。与逻辑仿真和硬件仿真的方法不同,fpga原型方法在成本和运行时间上花费更少,因此在工业上得到了广泛的应用。对于fpga原型设计,如果是很小规模的电路,则可以在单个fpga上进行逻辑验证。但是,目前的超大规模集成电路设计的尺寸是巨大的,fpga原型系统很难仅在一个fpga中进行设计。因此,人们开发了多fpga原型系统,将给定的超大规模集成电路设计划分为子电路,每个子电路可以在单个fpga中实现。由于单个fpga的物理上的限制,电路间信号通常超过i/o引脚的数量。因此提出了时分复用技术(timing division multiplexing,tdm)技术被提出解决i/o引脚数量不足的问题。tdm技术有效地提高了fpga原型系统的信号传输能力。但是,由于时分多路复用延长了fpga间的信号延迟,因此大大降低了系统的时钟频率,如何优化tdm比率仍是一个重要的问题。

技术实现要素:

4.有鉴于此,本发明的目的在于提供一种考虑最大时延优化的fpga布线方法,以优化系统运行时间和优化最大时延为目标,有效提升多fpga原型系统的可用性。

5.为实现上述目的,本发明采用如下技术方案:

6.一种考虑最大时延优化的fpga布线方法,包括以下步骤:

7.步骤s1:采用布线驱动的布局优化算法,将电路设计划分为系统时延更小的分区;

8.步骤s2:采用基于拉格朗日松弛方法的tdm比率初次分配方法,得到最优的tdm比率分配结果;

9.步骤s3:基于实际约束条件的tdm比率合法化算法对tdm比率分配结果进行合法化操作;

10.步骤s4:基于协商交换的最大时延优化算法,进一步减少tdm比率,缩小系统时延。

11.进一步的,所述布线驱动的布局优化算法,具体为:

12.(1)为每个逻辑元素提供一个初始位置,并调整逻辑元素的面积;

13.(2)基于约束将逻辑元素打包到基本逻辑元素中;

14.(3)拥塞驱动的全局布局,为合法化提供全局布局结果;

15.(4)确定每个逻辑元素的确切位置;

16.(5)采用改进贪婪算法进行的详细布局。

17.进一步的,所述步骤s2具体为:

18.步骤s21:根据约束条件将tdm分配问题建模为公式(1),公式(1)如下所示:

[0019][0020]

其中,at

sink

是到达目标节点的系统时延,ati是到达节点i的系统时延,xi是第i条边上的tdm比率,pi是第i个连接对上边的数目;

[0021]

其中,公式(1)中的第二个约束条件展开后可以得到公式(2),公式(2)如下所示:

[0022][0023]

步骤s22:对公式(2)中所示的约束进行松弛,对于每一个约束条件,引入一个非负的拉格朗日乘子变量;

[0024]

步骤s23:基于拉格朗日松弛法求解约束优化问题,得到最优的tdm比率分配结果。

[0025]

进一步的,所述步骤s22具体为:

[0026]

对每个fpga引入了λi,并且对每条边e

p,q

上的约束引入μ

p,q

,松弛后的公式如下所示:

[0027][0028]

综上,与拉格朗日乘子μ,λ相关的拉格朗日松弛子问题(lrs)将定义为:

[0029][0030]

进一步的,所述步骤s23具体为:

[0031]

在kkt条件下,pp的较优解也是拉格朗日松弛子问题的较优解,因此,μ和λ必须满足kkt条件和在求解拉格朗日对偶问题(ldp)的(μ,λ)时,只考虑那些满足这些条件的乘子,同时这也表明了乘子上的最优性条件,如公式(5)所示:

[0032][0033]

因此,通过(μ,λ)就可以得到x,如公式(6)所示:

[0034][0035]

由于μ和λ是两组非负变量,所以lrs/(μ,λ)的最优值并不大于pp目标值,如果最大化l

μ,λ

的最小值,得到一个更紧密的pp下界

[0036]

通过迭代更新μ和λ,l

μ,λ

的下界将更接近pp的最优解,最终达到收敛,设q(μ,λ)表示lrs/(μ,λ)的最优值,ldp的公式如下:

[0037][0038]

当优化ldp时,只需要考虑公式(7)定义的解空间ω中的(μ,λ);之前的工作通常使用任意分配的乘子作为初始拉格朗日乘子,然后通过不断迭代更新乘子;为了更新乘子;

[0039]

将μ

p,q

的初始值与影响at

p,q

的tdm边数联系起来,通过将μ

p,q

与影响at

p,q

的tdm边的数量成正比来获得μ的初始分配。

[0040]

进一步的,所述λ的初始化方法如下:

[0041][0042]

在求解lrs/(μ,λ)后,根据每条边的时间临界值来更新μ,使用公式(9)来控制收敛速度和质量;

[0043]

[0044]

其中,i为当前迭代次数;

[0045]

进一步的,采用贪心算法来更新μ,首先,更新目标节点的μ

i,sink

,如公式(10)所示:

[0046]

μ

′

i,sink

=μ

i,sink

·

(1+r),if at

i,sink

≥c

·

at

sink

ꢀꢀ

(10)

[0047]

然后,对中间节点的拉格朗日乘数进行更新;当一个节点g

p

输出边的拉格朗日乘数更新后,该布线图会出现违反约束的情况。

[0048]

违反约束的情况可分为两种:(1)和(2)第一种情况推断at

p

至少在一个关键路径上,需要减少at

p

以改善at

sink

,将输出边与输入边的差值平均分配给边{e

i,p

|at

i,p

≥c

·

at

p

}。其中,c的值为常数如公式(12)所示:

[0049][0050]

在情况(2)中,更新以g

p

作为输出节点的边上的拉格朗日乘子;为了最小化at

sink

,首先只对所有的j∈{k|at

k,p

<at

p

}减少乘数μ

j,p

;当不能仅通过减少这些乘数来满足约束时,将每条边上的拉格朗日乘子的差值按比例进行减少;但是,当出现每个输入边的到达时间等于at

p

时,将通过公式(12)对每条边的拉格朗日乘子进行更新;更新μ后,λ仍然按照公式(8)方式进行更新。

[0051]

进一步的,所述步骤s3具体为:首先,遍历每条边上的每一个网,并通过向上取整的方式来使分配的tdm比率合法化;然后,如果得到的结果为奇数,将它们增加1,以使它们成为偶数;由于一个数的增加减小了它的倒数,所以上述操作保证了每条边上的tdm比率倒数和小于1。

[0052]

进一步的,所述基于协商交换的最大时延优化算法具体为:通过交换两个fpga间的边的tdm比率判断最大tdm比率是否减少,如果最大tdm比率减少,则交换这两条边的tdm比率;如果在上一次迭代中进行了交换,并且结果与前预设次迭代相比得到了改进,则认为系统时钟周期有改进的空间。

[0053]

本发明与现有技术相比具有以下有益效果:

[0054]

本发明有效优化系统运行时间和优化最大时延,提升多fpga原型系统的可用性。

附图说明

[0055]

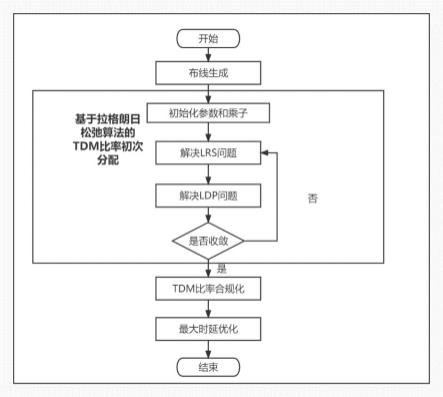

图1是本发明方法流程图;

[0056]

图2是本发明一实施例中解决ldp问题算法流程图。

具体实施方式

[0057]

下面结合附图及实施例对本发明做进一步说明。

[0058]

请参照图1,本发明提供一种考虑最大时延优化的fpga布线方法,包括以下步骤:

[0059]

步骤s1:采用布线驱动的布局优化算法,将电路设计划分为系统时延更小的分区;

[0060]

步骤s2:采用基于拉格朗日松弛方法的tdm比率初次分配方法,得到最优的tdm比率分配结果;

[0061]

步骤s3:基于实际约束条件的tdm比率合法化算法对tdm比率分配结果进行合法化操作;

[0062]

步骤s4:基于协商交换的最大时延优化算法,进一步减少tdm比率,缩小系统时延。

[0063]

在本实施例中,对于多fpga原型系统来说,需要使用高效的布线方法来对其进行fpga片间的初始布线,来确定哪些fpga是相互连通的。使用fpga布线图、线网列表和线网组信息作为输入的信息,在这一阶段考虑线网组的临界性是非常重要的,因为优化tdm比率受到路由拓扑的限制。所有的线网首先基于kmb算法进行布线,这是一种斯坦纳树近似算法。然后,进行拆线和重复布线,进一步提高布线结果。具体来说就是根据线网组规模来评估布线顺序,按序使用一些最短路径算法来找到每个需要完成的连接对的路径。最后,对布线好的线网进行评价,对不好的线网布线进行重新布线,提高布线结果,完成布线生成。

[0064]

优选的,在本实施例中,基于布线驱动的布局优化算法被用来进行布局操作。算法包括以下五个阶段:(1)划分,为每个逻辑元素提供一个初始位置,并调整逻辑元素的面积;(2)打包,基于约束将逻辑元素打包到基本逻辑元素(basic logic elements,ble)中;(3)拥塞驱动的全局布局,为合法化提供全局布局结果;(4)合法化,确定每个逻辑元素的确切位置;(5)详细布局,改进贪婪算法的布局。

[0065]

优选的,在本实施例中,tdm比率初次分配具体包括:

[0066]

(1)问题建模与转换

[0067]

将tdm分配问题进行建模和转换,以得到较优的tdm比率,从而减少系统时延。首先,根据约束条件将问题建模为公式(1),公式(1)如下所示:

[0068][0069]

其中,at

sink

是到达目标节点的系统时延,ati是到达节点i的系统时延,xi是第i条边上的tdm比率,pi是第i个连接对上边的数目。

[0070]

其中,公式(1)中的第二个约束条件展开后可以得到公式(2),公式(2)如下所示:

[0071][0072]

(2)拉格朗日松弛法

[0073]

拉格朗日松弛(lagrangian relaxation,lr)法是一种求解约束优化问题的近似优化方法。这种算法在许多方面都有应用。在拉格朗日松弛过程中,可以将问题中难以解决的约束条件转移到优化目标上。lr是解决约束优化问题的一个通用框架。通过对原始问题(primal problem,pp)中的困难约束进行二元化,可以得到拉格朗日松弛子问题

(lagrangian relaxation subproblem,lrs)。lrs是一个更容易解决的问题。对于最小化问题,lrs的最优解是pp上的一个下界。pp中违反的约束通过lrs中的拉格朗日乘子(lagrangian multipliers,lms)进行惩罚。此外,关于lms的下界最大化的问题被称为拉格朗日对偶问题(lagrangian dual problem,ldp)。由于往往很难找到pp的最优lm,因此采用迭代方法对lm进行更新。

[0074]

本实施例提出了一种新的更新策略,以减少迭代更新次数。首先,对公式(2)中所示的约束进行松弛。对于每一个约束条件,引入一个非负的拉格朗日乘子变量,这样任何违反这些约束的结果都将受到惩罚,从而避免产生更差的tdm比率分配结果。

[0075]

具体地说,对每个fpga引入了λi,并且对每条边e

p,q

上的约束引入μ

p,q

。松弛后的公式如下所示:

[0076][0077]

综上,与拉格朗日乘子μ,λ相关的拉格朗日松弛子问题(lrs)将定义为:

[0078][0079]

(3)解决拉格朗日松弛子问题

[0080]

在kkt条件下,pp的较优解也是拉格朗日松弛子问题的较优解。因此,μ和λ必须满足kkt条件和在求解拉格朗日对偶问题(ldp)的(μ,λ)时,只考虑那些满足这些条件的乘子。同时这也表明了乘子上的最优性条件,如公式(5)所示。

[0081][0082]

因此,通过(μ,λ)就可以得到x,如公式(6)所示:

[0083][0084]

(4)解决拉格朗日对偶问题

[0085]

由于μ和λ是两组非负变量,所以lrs/(μ,λ)的最优值并不大于pp目标值。因此,如果最大化l

μ,λ

的最小值,就可以得到一个更紧密的pp下界。通过迭代更新μ和λ,l

μ,λ

的下界将更接近pp的最优解,最终达到收敛。设q(μ,λ)表示lrs/(μ,λ)的最优值。ldp的公式如下:

[0086][0087]

当优化ldp时,只需要考虑公式(7)定义的解空间ω中的(μ,λ)。之前的工作通常使用任意分配的乘子作为初始拉格朗日乘子,然后通过不断迭代更新乘子。为了更新乘子,通常采用次梯度公式优化来更新乘子。然而,本发明从解空间ω中的乘子找到一个良好的初始赋值开始,然后,通过所示的一种新方法对乘子进行更新,并考虑了在更新期间的kkt条件。

[0088]

参考图2,是求解ldp的流程图。

[0089]

μ

p,q

的初始值与影响at

p,q

的tdm边数联系起来,通过将μ

p,q

与影响at

p,q

的tdm边的数量成正比来获得μ的初始分配。此外,λ的初始化方法如下:

[0090][0091]

在求解lrs/(μ,λ)后,根据每条边的时间临界值来更新μ。使用公式(9)来控制收敛速度和质量。

[0092][0093]

其中,i为当前迭代次数。

[0094]

本实施例中,应用贪心算法来更新μ,试图减少每次迭代中关键路径上的tdm比率,以此减少最大系统时延。首先,更新目标节点的μ

i,sink

,如公式(10)所示:

[0095]

μ

′

i,sink

=μ

i,sink

·

(1+r),if at

i,sink

≥c

·

at

sink

ꢀꢀ

(10)

[0096]

然后,对中间节点的拉格朗日乘数进行更新。当一个节点g

p

输出边的拉格朗日乘数更新后,该布线图会出现违反约束的情况。违反约束的情况可分为两种:(1)和(2)第一种情况推断at

p

至少在一个关键路径上,需要减少at

p

以改善at

sink

。因此,本发明将输出边与输入边的差值平均分配给边{e

i,p

|at

i,p

≥c

·

at

p

}。其中,c的值为常数,为0.95。如公式(12)所示:

[0097][0098]

在情况(2)中,虽然节点g

p

比之前的时间关键更少,但它可能仍然在一个关键路径上。因此,更新以g

p

作为输出节点的边上的拉格朗日乘子。为了最小化at

sink

,首先只对所有的j∈{k|at

k,p

<at

p

}减少乘数μ

j,p

。当不能仅通过减少这些乘数来满足约束时,将每条边上

的拉格朗日乘子的差值按比例进行减少。但是,当出现每个输入边的到达时间等于at

p

时,将通过公式(12)对每条边的拉格朗日乘子进行更新。

[0099]

更新μ后,λ仍然按照公式(8)方式进行更新。

[0100]

优选的,在本实施例中,tdm比率合法化,具体包括:由于连续求解器以全局的方式优化了tdm比率,因此其结果在离散化过程中应该得到尊重。由于连续求解器得到的结果为连续解,不满足tdm比率应为偶数的约束条件。因此,tdm比率需要进行合法化操作。首先,遍历每条边上的每一个网,并通过向上取整的方式来使分配的tdm比率合法化。然后,如果得到的结果为奇数,将它们增加1,以使它们成为偶数。由于一个数的增加减小了它的倒数,所以上述操作保证了每条边上的tdm比率倒数和小于1。

[0101]

优选的,在本实施例中,tdm比率优化,具体为:基于交换的tdm比率优化算法。例如,给定一个连续解at

p

=8,atm=16,delay

p,q

=16和delay

m,n

=8。由此可知,这两条边的最优结果位移为0。但当考虑时序图中其他边的离散化结果时,at

p

和atq的值变为15和9。如果交换e

p,q

和e

m,n

的tdm比率,max(atn,atq)可以提高6。具体算法是通过交换两个fpga间的边的tdm比率判断最大tdm比率是否减少,如果最大tdm比率减少,则交换这两条边的tdm比率,以改善系统时钟周期。如果在上一次迭代中进行了交换,并且结果与前10次迭代相比得到了改进,则认为系统时钟周期有改进的空间。如果一个tdm线网netj满足以下两个约束条件,则认为它是neti的候选对象:(1)neti的tdm比值小于netj。(2)对于给定的resslackj应大于0。resslackj是与neti交换后netj的最大松弛量。在优化阶段中首先尝试交换resslackj更大的边的tdm比率,通过此交换方式更有可能减少系统时钟周期。

[0102]

以上所述仅为本发明的较佳实施例,凡依本发明申请专利范围所做的均等变化与修饰,皆应属本发明的涵盖范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1