一种基于FPGA单热点分布的信息表示方法及其电路结构

一种基于fpga单热点分布的信息表示方法及其电路结构

技术领域

1.本发明属于电路的自热效应领域,更具体地说,尤其涉及一种基于fpga 单热点分布的信息表示方法及其电路结构。

背景技术:

2.对于电路热效应产生的温度进行信息表示的研究来源于利用电路热效应进行信息传输。

3.guri等人通过热信号在两台空间相邻的但网络隔离的计算机之间构建了 bitwhisper气隙隐蔽信道,利用机器的热排放控制周围环境的温度,从而根据温度的差异表示不同的隐蔽信息,为热效应信息表示提供了理论指导。

4.此外,masti等人通过cpu温度的高低变化实现信息的隐蔽通信。该信道发送比特1时会执行rsa破解算法,产生大量的cpu密集型任务,使得温度传感器的测量值升高;发送比特0时,信道则保持静默,令温度传感器的测量值变低。显而易见,这种利用电路整体温度的高低表示信息的方式,资源占用较大且单次信息的含量上略显不足。

技术实现要素:

5.本发明的目的是为了解决现有技术中存在的缺点,能够搭载更多的信息,在同样的信息表示周期内能够表示更多的信息,且编码信息相对自由,更具安全性。此外,相比通过执行算法提高整体温度的方式,基于lut的发热电路结构和基于dsp的发热电路结构能够在占用较小的资源开销的情况下实现信息的有效表示,在同样的面积开销下,环形振荡器电路通过反相器信号不断翻转产生更高的功耗使得区域温度能够显著提升,从而能够增加信息表达的范围与有效性,而提出的一种基于fpga单热点分布的信息表示方法及其电路结构。

6.为实现上述目的,本发明提供如下技术方案:一种基于fpga单热点分布的信息表示方法,包括如下步骤:

7.s1、为了实现热点分布信息表示,首先将fpga器件按物理位置进行区域分块,为实现八种信息表示对其物理空间进行4

×

2的区域划分,并对区域进行独热编码,即每一个“热点”表示对应的1位数据;

8.s2、根据分块区域的编码,在目标信息匹配的物理区域内布置合适的电路结构使其工作时与其他区域产生温度差,进而通过热成像仪对fpga的温度分布进行检测,得到表示的信息。

9.优选的,所述合适的电路结构包括两种利用自热效应实现信息表示的电路结构,一是基于fpga的lut资源,二是基于fpga的dsp资源。

10.本发明还提供一种基于fpga单热点分布的信息表示方法的电路结构,包括基于lut的发热电路结构和基于dsp的发热电路结构,所述基于lut的发热电路结构是由环形振荡器实现的,利用一定数量、级联级数的环形振荡器电路输入输出信号不断反向产生功耗,

并进一步调节电压使得该区域能够更加高效发热,进而在fpga的整个热分布图上通过观察热点得到信息。

11.优选的,所述环形振荡器起振的源于头部lut,延迟单元buffer的输入输出同相,工作时在延迟链的延迟下产生相应的振荡频率,环形振荡器工作频率公式为:

[0012][0013]

优选的,所述环形振荡器工作频率公式中的f

ro

表示环形振荡器的振荡频率,d

ro

表示环形振荡器的延迟。

[0014]

优选的,所述环形振荡器由lut构成,d

ro

为串联的lut延迟之和。即级联越深,即串联的buffer越多,反相工作频率越低,功耗越低,发热效果不明显,因而想要提高环形振荡器工作频率,以增强其发热效应,需要减少级联深度,可只保留头部lut而不连接延迟单元。

[0015]

优选的,所述基于dsp的发热电路结构是基于乘加运算实现的,设定由dsp实现一系列乘加运算,并将dsp的输入输出数据首尾相连,使得dsp持续工作,所在区域高效发热,进而在fpga的整个热分布图上通过观察热点得到信息。

[0016]

优选的,在基于dsp实现乘加运算时,为了使得dsp电路产生足够的功耗且能够使得生成的热分布图具有良好的分辨性,本发明实现了16bit输入的一维离散卷积运算,输入的多项式为4项,得到七个32bit输出。

[0017]

与现有技术相比,本发明的技术效果和优点:

[0018]

通过基于lut的发热电路结构和基于dsp的发热电路结构的设计,本发明能够搭载更多的信息,在同样的信息表示周期内能够表示更多的信息,且编码信息相对自由,更具安全性。此外,相比通过执行算法提高整体温度的方式,基于lut的发热电路结构和基于dsp的发热电路结构能够在占用较小的资源开销的情况下实现信息的有效表示,在同样的面积开销下,环形振荡器电路通过反相器信号不断翻转产生更高的功耗使得区域温度能够显著提升,从而能够增加信息表达的范围与有效性。

附图说明

[0019]

图1为本发明fpga器件的4

×

2区域划分图;

[0020]

图2为本发明环形振荡器的内部结构图;

[0021]

图3为本发明的物理约束布局示意图;

[0022]

图4为本发明的约束区域内的占用资源情况图;

[0023]

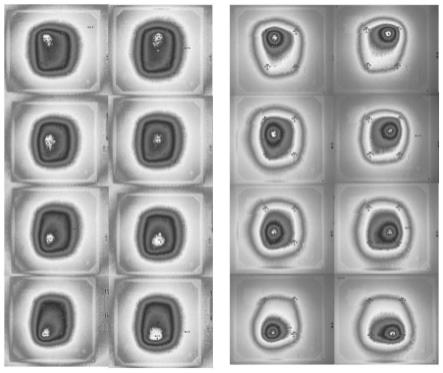

图5为本发明的热分布图。

具体实施方式

[0024]

为了使本发明的目的、技术方案及优点更加清楚明白,以下结合具体实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0025]

请参阅图1-5,本发明提出一种基于fpga单热点分布的信息表示方法,包括如下步骤:

[0026]

s1、为了实现热点分布信息表示,首先将fpga器件按物理位置进行区域分块,为实现八种信息表示对其物理空间进行4

×

2的区域划分,并对区域进行独热编码,即每一个“热点”表示对应的1位数据;

[0027]

s2、根据分块区域的编码,在目标信息匹配的物理区域内布置合适的电路结构使其工作时与其他区域产生温度差,进而通过热成像仪对fpga的温度分布进行检测,得到表示的信息。

[0028]

fpga的型号设置为xilinx xc7a100t。

[0029]

所述合适的电路结构包括两种利用自热效应实现信息表示的电路结构,一是基于fpga的lut资源,二是基于fpga的dsp资源。

[0030]

本发明还提供一种基于fpga单热点分布的信息表示方法的电路结构,包括基于lut的发热电路结构和基于dsp的发热电路结构,所述基于lut的发热电路结构是由环形振荡器实现的,利用一定数量、级联级数的环形振荡器电路输入输出信号不断反向产生功耗,并进一步调节电压使得该区域能够更加高效发热,进而在fpga的整个热分布图上通过观察热点得到信息;

[0031]

其中,环形振荡器的深度设置为1,即只需要利用fpga的lut资源实现反相器,并使其输入输出相连而成环。为了产生足够的功耗,使得对应区域的热量能够区别于其他区域,需要在对应区域放置足够数量的环形振荡器,本发明在约束的区域内布局100个环形振荡器。

[0032]

所述环形振荡器起振的源于头部lut,延迟单元buffer的输入输出同相,工作时在延迟链的延迟下产生相应的振荡频率,环形振荡器工作频率公式为:

[0033][0034]

所述环形振荡器工作频率公式中的f

ro

表示环形振荡器的振荡频率,d

ro

表示环形振荡器的延迟。

[0035]

所述环形振荡器由lut构成,d

ro

为串联的lut延迟之和。即级联越深,即串联的buffer越多,反相工作频率越低,功耗越低,发热效果不明显,因而想要提高环形振荡器工作频率,以增强其发热效应,需要减少级联深度,可只保留头部lut而不连接延迟单元。

[0036]

所述基于dsp的发热电路结构是基于乘加运算实现的,设定由dsp实现一系列乘加运算,并将dsp的输入输出数据首尾相连,使得dsp持续工作,所在区域高效发热,进而在fpga的整个热分布图上通过观察热点得到信息。

[0037]

在基于dsp实现乘加运算时,为了使得dsp电路产生足够的功耗且能够使得生成的热分布图具有良好的分辨性,本发明实现了16bit输入的一维离散卷积运算,输入的多项式为4项,得到七个32bit输出。

[0038]

其中一种信息表示(8’b00000001)对应的电路布局在vivado综合工具下的约束示意如图3所示,左侧为基于lut的环形振荡器约束,右侧为基于 dsp的运算电路约束。图4为本发明提出的电路结构在该约束区域内的占用资源情况,左侧为基于lut的环形振荡器资源占用情况,右侧为基于dsp的运算电路占用情况。

[0039]

利用综合工具将电路信息转化为bit流文件,将其配置进fpga后,通过热成像仪对fpga芯片的温度进行检测,得到相应的热分布图,根据“热点”来判断信息的表示内容。本发

明探索了将上述环形振荡器约束在八个不同的区域内进行信息表示的热分布效果,在调节电路电压为1.51v的条件下,得到结果如下图5所示,可以看出该电路结构能够有效实现4

×

2的信息表示。

[0040]

综上所述,本发明能够搭载更多的信息,在同样的信息表示周期内能够表示更多的信息,且编码信息相对自由,更具安全性。此外,相比通过执行算法提高整体温度的方式,基于lut的发热电路结构和基于dsp的发热电路结构能够在占用较小的资源开销的情况下实现信息的有效表示,在同样的面积开销下,环形振荡器电路通过反相器信号不断翻转产生更高的功耗使得区域温度能够显著提升,从而能够增加信息表达的范围与有效性。

[0041]

最后应说明的是:以上所述仅为本发明的优选实施例而已,并不用于限制本发明,尽管参照前述实施例对本发明进行了详细的说明,对于本领域的技术人员来说,其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1