一种系统DDR内存可使用容量的自动化识别方法与流程

一种系统ddr内存可使用容量的自动化识别方法

技术领域

1.本发明涉及ddr技术领域,尤其涉及一种系统ddr内存可使用容量的自动化识别方法。

背景技术:

2.ddr(double data rate,代表双倍数据速率)是目前最常见的内存接口,绝大多数芯片都需要用到内存,尤其是soc(system on a chip),片上系统)芯片。soc芯片内通常需要集成一个dmc(ddr控制器),将来自内部业务上游的读写命令,解释,调度转化为标准ddr接口命令与dram(dynamic random access memory,动态随机存取存储器)颗粒存取数据;这其中很重要的一项也是本专利重点关注的便是将来自上游业务的读写地址映射为ddr接口物理地址。ddr作为世界最通用的技术协议家族之一,经过几十年的发展,从低速到高速依次发展出ddr1/ddr2/ddr3/ddr4/ddr5,以及其他衍生类lpdd r/gddr/hbm/等协议。

3.ddr接口总体分为两类信号:1)ca(控制)信号传递命令/地址;2)dq/dm/dqs(数据)等信号传递数据,如图1所示。ca的地址信号由ba以及addr构成(addr在不同时钟周期又可分为row地址跟col地址),所以ba与addr(row+col)地址线位宽决定了dram最大可寻址范围;dq总的位宽决定了整颗dram数据总线位宽;寻址范围乘以数据总线位宽代表了该dram支持的最大内存容量。dram颗粒按照dq位宽区分,有三种位宽规格——x4,x8,x16;按照容量区分则有四~五种规格(如ddr3就有512mb,1gb,2gb,4gb,8gb等规格,如图2所示8gb规格);ddr接口总线位宽设计为16bit,如果用x16的dram颗粒,只需要一颗(如图1,图1即表达的是与x16 dram颗粒对接的ddr接口构成。),那么我们芯片的可使用内存大小就是这一颗dram容量决定;如果用x8的dram颗粒,则需要两颗(如图3),那么我们芯片的可使用内存大小就是由这两颗dram容量决定;如果用x4的颗粒,则需要4颗,那么我们芯片的可使用内存大小就是由这四颗dram容量决定。因为我们在设计soc芯片时,其ddr数据总线位宽已经确定,后期ddr内存可使用容量主要就由对接的dram颗粒的数量与容量决定,而dram颗粒的容量其实是由dq位宽乘以2^(ba地址位宽+row地址位宽+col地址位宽)决定,因为2^(ba地址位宽+row地址位宽+col地址位宽)表示dram颗粒寻址空间,dq位宽表示每个地址可存放的数据bit。当ddr总线总的数据位宽dq确定,无论我们最终用几颗dram颗粒拼接,最终dram内存可使用容量都仅仅由2^(ba地址位宽+row地址位宽+col地址位宽)确定。假设我们ddr3总线数据位宽dq设计为16bit,内存容量需要8gb,那么只需要一颗容量为8gb的x16颗粒(三位ba地址+16位row地址+10位col地址=29),或者是用两颗容量为4gb的x8颗粒(三位ba地址+16位row地址+10位col地址=29),又或者是四颗容量为2gb的x4颗粒(三位ba地址+15位row地址+11位col地址=29),这三种方案总的地址位宽是一样的,都是29位。注意:从这里我们知道,ddr接口数据总线位宽确定的条件下,颗粒有效地址位宽决定了总的可使用dram内存容量。

4.dram颗粒内存储架构如图4所示:以最基本的电容阵列来存储计算机逻辑bit信息,对电容的充放电来完成写读操作。整体架构根据容量不同,分为几个bank(由ca中的ba

信号作为地址选择寻址);bank下面就是由一块纵横排列的电容整列,分为行地址row(由ca中的addr[0:17]信号做地址选择寻址),列地址col(由ca中的addr[0:9]信号做地址选择寻址)。当我们要往dram颗粒某个地址存取数据时,首先要通过ca线发一个带ba地址跟行地址row的act(activate)命令,来选择把命中bank选中row行的整行电容数据load到bank自带缓存buffer中;然后再通过ca线发一个带列地址col的写读命令到该bank的buffer命中列地址col去存取数据;最后还要发一个pre(precharge)命令让dram颗粒把buffer中的数据再次存回行地址row选中的一行电容中,保持数据不丢失,并方便上游业务对该bank其他row行的act访问(因为每个bank只有一行数据缓存buffer)。注意:dmc为了提升访问dram颗粒的效率,并不是每次写读dram后,都会立刻发出pre(precharge)命令,而是时刻监测内部来自业务上游的访问队列,通过算法调度把访问dram颗粒同一bank,同一row行的相关请求都响应完后,才会发出pre(precharge)命令。

[0005]

现有技术的缺陷和不足:

[0006]

目前较新版本ddr类协议,如ddr4/5等可以通过读出颗粒中mpr寄存器的厂商自定义格式内容来识别颗粒容量等信息,但是不同颗粒厂商自定义的格式不一样,且无法通过该方法获得ddr3等较早期版本协议的颗粒信息,因为ddr3没有定义该寄存器。目前大家在设计芯片时普遍没有做自动识别ddr内存容量并自适应配置的方案,都是根据客户在使用芯片时的pcb板设计规划,定制化更改ddr初始化配置软件代码,这样不能做到自动化适配,增加了芯片在二次开发应用过程中的使用门槛与维护成本。

[0007]

为了解决现有技术中的不足,本发明提出了一种系统ddr内存可使用容量的自动化识别方法,通过多次读写ddr地址边界,根据地址卷绕空间的大小,自动识别ddr类协议内存容量;本发明原理简单,实现方便,在ddr类内存系统中具有普适性,无论ddr/lpddr/gddr/hbm等,可无缝拓展迁移,在初始化配置ddr子系统的过程中,增加了软件自动化程度,减少后续维护成本。

技术实现要素:

[0008]

为了解决现有技术中的不足,本发明提出了一种系统ddr内存可使用容量的自动化识别方法,通过多次读写边界,根据卷绕工作原理,自动识别ddr类协议内存容量;本发明原理简单,实现方便,在ddr类内存系统中具有普适性,无论ddr/lpddr/gddr/hbm等,可无缝拓展迁移,在初始化配置ddr子系统的过程中,增加了软件自动化程度,减少后续维护成本。

[0009]

为实现上述目的,本发明采用如下的技术方案。

[0010]

在本发明实施例中,提出了一种系统ddr内存可使用容量的自动化识别方法,该方法包括如下步骤:

[0011]

s1完成ddr的常规初始化;

[0012]

s2根据ddr最大设计内存容量,按照row/bank/colddr物理地址排列顺序,配置dmc系统地址到ddr物理地址的映射关系;

[0013]

s3根据ddr所外接的dram内存颗粒容量的规格,确定相应容量的边界地址,并向所述边界地址写入特定数据值;

[0014]

s4根据读取ddr最大容量边界地址所获取的数据值,自动识别出ddr实际可用的内存容量。

[0015]

进一步的,首先确定ddr最大设计容量的边界地址并写入相应的特定数据值,然后逐级向低容量的边界地址写入相应的特定数据值。

[0016]

进一步的,读取ddr最大容量边界地址,获取相应的数据值,将读取到的数据值与所写入相应内存容量边界地址的数据值进行比较,根据卷绕的原理,由所获取到的数据值即可自动确定真正ddr所外接的dram可使用容量,即ddr实际可用的容量。

[0017]

本发明的有益效果在于,针对现有的ddr技术领域中存在的问题,提出了一种系统ddr内存可使用容量的自动化识别方法,通过多次读写边界,根据卷绕工作原理,自动识别ddr类协议内存容量;本发明原理简单,实现方便,在ddr类内存系统中具有普适性,无论ddr/lpddr/gddr/hbm等,可无缝拓展迁移,在初始化配置ddr子系统的过程中,增加了软件自动化程度,减少后续维护成本。

附图说明

[0018]

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。在附图中:

[0019]

图1为本发明背景技术中ddr3接口信号示意图;

[0020]

图2为本发明背景技术中ddr3颗粒容量示意图;

[0021]

图3为本发明背景技术ddr3总线颗粒拼接示意图;

[0022]

图4为本发明背景技术dram颗粒内部架构示意图;

[0023]

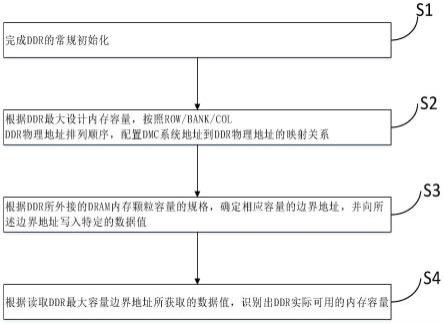

图5为本发明的实现流程示意图;

[0024]

图6为本发明实施例一系统地址到ddr物理地址的映射示意图;

[0025]

图7为本发明实施例一系统分配内存地址卷绕示意图;

[0026]

图8为本发明实施例一ddr容量自动识别方案流程图。

具体实施方式

[0027]

为使本发明实施例的目的、技术方案和优点更加清楚明白,下面结合附图对本发明实施例做进一步详细说明。以下实施用例仅用于更加清楚地说明本发明的系统方法及技术方案,而不能以此来限制本技术的保护范围。

[0028]

根据本发明的实施方式,本发明提出了一种系统ddr内存可使用容量的自动化识别方法,通过多次读写边界,根据卷绕的次数,自动识别ddr类协议内存容量;本发明原理简单,实现方便,在ddr类内存系统中具有普适性,无论ddr/lpddr/gddr/hbm等,可无缝拓展迁移,在初始化配置ddr子系统的过程中,增加了软件自动化程度,减少后续维护成本。

[0029]

下面参考本发明的若干代表性实施方式,详细阐释本发明的原理和精神。

[0030]

图5是一种系统ddr内存可使用容量的自动化识别方法的处理流程示意图。如图5所示,该方法包括如下步骤:

[0031]

s1完成ddr的常规初始化;

[0032]

s2根据ddr最大设计内存容量,按照row/bank/colddr物理地址排列顺序,配置dmc系统地址到ddr物理地址的映射关系;

[0033]

s3根据ddr所外接的dram内存颗粒容量的规格,确定相应容量的边界地址,并向所述边界地址写入相关的特定数据值;

[0034]

具体实施时,首先确定ddr最大容量的边界地址并写入相应的特定数据值,然后逐级向低容量的边界地址写入相应的特定数据值。

[0035]

s4根据读取ddr最大容量边界地址所获取的数据值,自动识别出ddr实际可用的容量。

[0036]

具体实施时,读取ddr最大容量边界地址,获取相应的数据值,将读取到的数据值与所写入相应容量边界地址的特定数据值进行比较,根据卷绕的原理,由所获取到的数据值即可自动确定真正ddr所外接的dram可使用容量,即ddr实际可用的容量。

[0037]

需要说明的是,尽管在上述实施例及附图中以特定顺序描述了本发明方法的操作,但是,这并非要求或者暗示必须按照该特定顺序来执行这些操作,或是必须执行全部所示的操作才能实现期望的结果。附加地或备选地,可以省略某些步骤,将多个步骤合并为一个步骤执行,和/或将一个步骤分解为多个步骤执行。

[0038]

为了对上述一种系统ddr内存可使用容量的自动化识别方法进行更为清楚的解释,下面结合一个具体的实施例来进行说明,然而值得注意的是该实施例仅是为了更好地说明本发明,并不构成对本发明不当的限定。

[0039]

实施例一:

[0040]

本发明所要解决的技术问题是通过软硬件自动识别ddr可使用内存容量。

[0041]

在具体实施过程中,我们假设系统为ddr3内存分配的地址空间为0x4000_0000~0x7fff_ffff,总共8gb,ddr3接口为16bitdq;由背景技术可知,最大8gb容量需要三位ba地址+16位row地址+10位col地址,总共29bit ddr物理地址;这些物理地址需要按照如图6所示,row、bank、col顺序由高到低映射到系统地址空间0x4000_0000~0x7fff_ffff;即系统地址sys_addr[29:14]映射为ddr物理地址row[15:0];sys_addr[13:11]映射为bank[2:0];sys_addr[10:1]映射为col[9:0](系统地址是8bit寻址,ddr物理地址为16bit寻址)。

[0042]

从系统地址到ddr物理地址的映射过程如下:

[0043]

1、当外接8gb容量的dram内存颗粒时,系统地址与ddr接口物理地址都对应匹配的;

[0044]

2、当外接4gb容量的dram内存颗粒时,ddr高位可用物理地址的row地址少了1bit,总共只剩下28bit,系统地址sys_addr[29]对应的ddr物理row地址悬空,那么高4gb系统地址空间发生卷绕(系统地址通过最高1bit地址信号标注为1,想访问高4gb空间,但是dram颗粒接收不到最高1bit地址信号,默认为0,以为还是访问低4gb空间);如图7所示,即系统访问高4gb内存时,其实物理上还是映射到了低4gb内存空间;

[0045]

3、当外接2gb容量的dram内存颗粒时,ddr高位可用物理地址的row少了2bit,只剩下27bit,系统地址sys_addr[29:28]对应的ddr物理row地址悬空,那么高6gb系统地址空间发生卷绕(系统地址通过最高2bit地址信号标注为1,想访问高6gb空间,但是dram颗粒接收不到最高2bit地址信号,默认为0,以为还是访问低2gb空间)。

[0046]

4、当外接1gb容量的dram内存颗粒时,高7gb系统地址空间发生卷绕(系统地址通过最高3bit地址信号标注为1,想访问高7gb空间,但是dram颗粒接收不到最高3bit地址信号,默认为0,以为还是访问低1gb空间)。

[0047]

dmc并不知道ddr接口外接了多少容量的dram颗粒,会误以为外界有全部8gb地址空间可用,假设我们只外接4gb容量dram,当系统访问完0x4000_0000地址后,立刻访问其卷绕地址0x6000_0000(对应到ddr物理地址就是同一个bank,不同行row),那么dmc会误以为是对其他行row的访问请求,那么dmc会首先发出pre命令关闭0x4000_0000对应row行的dram数据,然后再重新发出act命令打开0x6000_0000对应row行的dram数据(其实在dram侧是同一row行数据),进行访问;结合背景技术知识可知,这样卷绕访问虽然可能降低了访问效率,却没有违反ddr协议,不会访问出错。

[0048]

所以我们只要在soc系统上电初始化ddr后,利用软件读写dram,检测系统内存空间卷绕空间容量,就能证明实际可使用内存空间,并且读写卷绕空间只是有可能影响访问效率,不会影响读写正确性;根据该原理可有多种方式实现检测ddr内存使用容量,如图8就是最基本的一种流程(以ddr3为例)。

[0049]

一种系统ddr内存可使用容量的自动化识别方法,具体实施流程如下:

[0050]

注意:图8流程中具体操作是基于系统给ddr3分配的地址空间为0x4000_0000~0x8000_0000。

[0051]

步骤1:完成ddr3的初始化(协议规定,标准上电流程,配置dram颗粒等);

[0052]

ddr初始化是协议标准内容,本实施例不再详细描述。

[0053]

步骤2:根据ddr系统最大设计内存容量,按照row/bank/col顺序,配置dmc系统地址到ddr物理地址的映射关系;

[0054]

步骤3:根据ddr所外接的dram内存颗粒容量的规格,确定边界地址,并向边界地址写入特定的数据值;

[0055]

具体实施时,首先确定最大容量的边界地址写入特定数据值,逐级向低容量的边界地址写入相应的特定数据值;所述特定数据值区别于正常的业务数据值。示例:若最大容量为8g,则依次确定4g,2g,1g,512m容量的地址边界,并写入相关的数值。具体的,8g的边界地址为0x7fff_fffc,写入的数据值为0x7fff_fffc;4g的边界地址为0x5fff_fffc,写入的数据值为0x7fff_fffc;2g的边界地址为0x4fff_fffc,写入的数据值为0x7fff_fffc;1g的边界地址为0x47ff_fffc,写入的数据值为0x7fff_fffc;512m的边界地址为0x43ff_fffc,写入的数据值为0x7fff_fffc。

[0056]

步骤4:根据读取ddr最大容量边界地址所获取的数据值,即可自动识别出ddr实际可用的容量。

[0057]

读取最大容量边界地址,获取相应的数据值,将读取到的数据值与所写入相应地址边界的数据值进行比较,根据卷绕的原理,即可根据所述数据值自动确定ddr内存可使用的容量。以8g容量为例,若从8g的边界地址0x7fff_fffc获取到的数据值为0x7fff_fffc,(根据卷绕的原理,若实际的地址空间小于所认为的地址空间,则先写入的高位地址的内容会被覆盖),说明8g边界地址写入的数据没有被覆盖,可以认为ddr所外接的dram的内存实际容量为8g;若获取的数据值为0x5fff_fffc,说明8g边界地址写入的数据被4g边界地址写入的数据覆盖,且4g边界写入的数据没有被后面覆盖,则ddr所外接的dram内存实际容量为4g,依次类推,从而确定真正ddr所外接的dram可使用容量。

[0058]

本实施例以ddr3为例,具体实施中,本发明对于ddr类内存系统中具有普适性,无论ddr/lpddr/gddr/hbm等,可无缝拓展迁移。

[0059]

本发明的有益效果在于,针对现有的ddr领域中存在的问题,提出了一种系统ddr内存可使用容量的自动化识别方法,通过多次读写边界,根据卷绕的次数,自动识别ddr类协议内存容量;本发明原理简单,实现方便,在ddr类内存系统中具有普适性,无论ddr/lpddr/gddr/hbm等,可无缝拓展迁移,在识别ddr内存系统可使用容量的过程中,增加了软件自动化程度,减少后续维护成本。

[0060]

本发明申请人结合说明书附图对本发明的实施用例做了详细的说明与描述,以上实施用例仅为本发明的优选实施方案,详尽的说明只是为了帮助读者更好地理解本发明精神,而并非对本发明保护范围的限制,相反,任何基于本发明的发明精神所作的任何改进或修饰都应当落在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1