一种素数域椭圆曲线密码协处理器

1.本发明涉及信息安全技术领域,尤其是一种素数域椭圆曲线密码协处理器。

背景技术:

2.移动通信正在从传统的人和人的连接,向人与物以及物与物的连接迈进,万物互联是必然趋势。随着物联网的深度发展,物联网智能终端设备数量呈现爆炸性增长,从而带来了更加复杂的安全问题诸如设备认证、数据保护和无线通信。因此,为物联网系统设计一款安全密码协处理器来确保数据传输的安全性和隐私性非常重要。并且随着5g设备的大规模部署和应用,物联网应用对数据加密的速度要求更高,现有的安全密码协处理器性能已经无法满足5g时代的需求,迫切需要一种高性能高效率的安全密码协处理器。

3.椭圆曲线密码(elliptic curve cryptography,ecc)是实现这一目标的有效解决方案。ecc自从1985年koblit和miller发布以来,凭借其密钥短、时延低、安全性高和运算速度快等优点,迅速成为最受欢迎的新一代公钥密码体制,先后被ansi,ieee,nist和sca等国际标准组织接受和标准化,并广泛应用于物联网与信息安全领域。ecc可以在软件和硬件平台上实现,基于fpga硬件实现的ecc方案具有可重编程性、可配置性和高效密码处理性能特点,使得它非常适合物联网安全应用。

4.然而,现有的椭圆曲线密码协处理器仍然存在结构复杂、功耗高等缺点。且由于ecc密码体系理论复杂、运算量大,现有的技术较难满足计算性能的需求。现有技术中,使用低位宽的乘法器会导致运算器的性能较低;使用较多数量的乘法器会导致较大的功耗;使用高位宽的乘法器,因硬件无法满足要求,运算过程就只能运行在较低的频率上,运算性能较低。

技术实现要素:

5.本发明旨在至少解决现有技术中存在的技术问题之一。为此,本发明提出一种素数域椭圆曲线密码协处理器。

6.本发明所采取的技术方案是:

7.本发明实施例包括一种素数域椭圆曲线密码协处理器,包括寄存器模块、naf编码模块、运算模块和控制器模块;

8.所述寄存器模块用于接收输入的原始数据和存储点乘运算过程中产生的坐标数据和中间数据;

9.所述naf编码模块用于执行naf编码点乘算法,以减少所述点乘运算过程中的点加运算次数和点倍运算次数;

10.所述运算模块包括模乘器单元、模平方器单元、第一模加器单元和第二模加器单元,所述模乘器单元与所述第一模加器单元和所述第二模加器单元连接并构成三级流水线结构,以执行模乘运算;所述模平方器单元与所述第一模加器单元和所述第二模加器单元连接并构成三级流水线结构,以执行模平方运算,所述模乘器单元与所述模平方器单元并

行进行运算;

11.所述控制器模块用于通过流水的方式控制所述点乘运算的数据流向。

12.进一步地,所述寄存器模块包括随机数寄存器和坐标寄存器,所述随机数寄存器与所述naf编码模块连接;

13.所述随机数寄存器用于寄存随机数数据;

14.所述坐标寄存器用于寄存坐标数据。

15.进一步地,所述模乘器单元包括乘法运算组件和模约减运算组件,所述乘法运算组件的输出为所述模约减运算组件的输入,所述模约减运算组件的输出流入所述第一模加器单元和所述第二模加器单元。

16.进一步地,所述模平方器单元的面积为所述模乘器单元面积的0.66倍。

17.进一步地,所述模平方器单元包括平方计算组件和模约减计算组件,所述平方计算组件的输出为所述模约减计算组件的输入,所述模约减计算组件的输出流入所述第一模加器单元和所述第二模加器单元。

18.进一步地,所述第一模加器单元包括第一加法器、第二加法器、多个移位寄存器和多个数据选择器,所述第一加法器与所述第二加法器串联,多个所述数据选择器逐级相连并接入所述第一加法器,以控制输入所述第一加法器的数据,多个所述移位寄存器和多个所述数据选择器连接后接入所述第二加法器的输入端,所述第二加法器的输出端接入一个所述数据选择器后接入2个所述移位寄存器。

19.进一步地,所述第一模加器单元的输出端设计有4套接口,以输出相应的数据。

20.进一步地,所述第二模加器单元的结构与所述第一模加器单元的结构相同

21.本发明的有益效果是:

22.本发明提供一种素数域椭圆曲线密码协处理器,包括寄存器模块、naf编码模块、运算模块和控制器模块;其中,运算模块包括模乘器单元、模平方器单元、第一模加器单元和第二模加器单元,模乘器单元与第一模加器单元和第二模加器单元连接并构成三级流水线结构,以执行模乘运算;模平方器单元与第一模加器单元和第二模加器单元连接并构成三级流水结构,以执行模平方运算,模乘器单元与模平方器单元并行进行运算,能够加快运算速率,实现较高性能,同时能够实现面积和性能的最佳权衡,非常适合高速加密解密应用。

23.本发明的附加方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显或通过本发明的实践了解到。

附图说明

24.本发明的上述和/或附加的方面和优点从结合下面附图对实施例的描述中将变得明显和容易理解,其中:

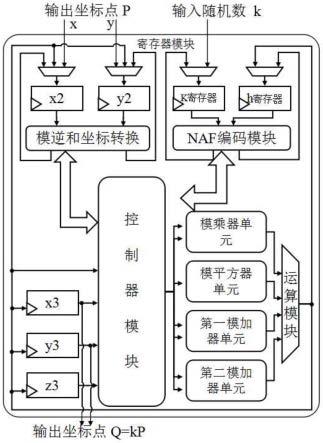

25.图1为本发明实施例所述素数域椭圆曲线密码协处理器的框架图;

26.图2为本发明实施例所述naf编码点乘算法的示意图;

27.图3为本发明实施例所述普通的蒙哥马利算法的示意图;

28.图4为本发明实施例所述改进的蒙哥马利算法的示意图;

29.图5为本发明实施例所述运算模块的结构图;

30.图6为本发明实施例所述模乘运算的流程示意图;

31.图7为本发明实施例所述平方运算化简过程的示意图;

32.图8为本发明实施例所述改进的蒙哥马利模平方算法的示意图;

33.图9为本发明实施例所述模平方运算的流程示意图;

34.图10为本发明实施例所述改进的模逆算法的示意图;

35.图11为本发明实施例所述加法器的结构示意图;

36.图12为本发明实施例所述第一模加器单元的结构示意图。

具体实施方式

37.下面详细描述本发明的实施例,所述实施例的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。下面通过参考附图描述的实施例是示例性的,仅用于解释本发明,而不能理解为对本发明的限制。

38.在本发明的描述中,需要理解的是,涉及到方位描述,例如上、下、前、后、左、右等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。

39.在本发明的描述中,若干的含义是一个或者多个,多个的含义是两个以上,大于、小于、超过等理解为不包括本数。如果有描述到第一、第二、第三等只是用于区分技术特征为目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量或者隐含指明所指示的技术特征的先后关系。

40.本发明的描述中,除非另有明确的限定,设置、安装、连接等词语应做广义理解,所属技术领域技术人员可以结合技术方案的具体内容合理确定上述词语在本发明中的具体含义。

41.椭圆曲线密码(ellipticcurvecryptography,ecc)中核心运算就是基域上的基本运算和椭圆曲线上的点乘运算。定义在二进制域(gf(2m))的椭圆曲线满足以下方程:

42.e:v2+xv=x3+ax2+b(1);

43.该方程称为weierstrass方程,其中a,b∈gf(2m),且b≠0。椭圆曲线中的元素包括方程(1)中所有点(x,y)的集合,以及无穷远点0。椭圆曲线最主要的运算是点加(pointaddition,pa)和点倍(pointdoubling,pd)两种运算。其中对于p≠q,pa的表达式为r(xr,yr)=p+q,对于p=q,pd的表达式为r(xr,yr)=2p。

44.在不同坐标系下,pa和pd的计算公式各不相同,参照表1,表1中列出了曲线y2+xy=x

3-3x+b在各种坐标系下pa和pd的计算复杂度。如表1所示,使用混合雅可比-仿射坐标计算pa,使用雅可比坐标计算pd,可以有效避免耗时最长的求逆运算,减少模乘和模平方运算的计算频率,整体的运算速率最高。

45.表1不同坐标系下计算复杂度的对比

46.coordinatepapdaffine coordinate1ia+2mb+1sc1i+2m+2sprojective coordinate12m+2s7m+3sjacobin coordinate12m+4s4m+4s

chudnovsky coordinate11m+3s5m+4smixed jacobin-affine coordinate8m+3s 47.在不同的坐标之间切换,需要用到坐标转换,其中公式(2)是仿射坐标转换为jacobin坐标的公式。公式(3)是jacobin坐标转换为仿射坐标的公式。

48.(x,y)

→

{(x,y,z)|x=x,y=y,z=1}(2);

49.(x,y,z)

→

{(x,y)|x=x/z2,y=y/z3}(3);

50.在混合雅可比-仿射坐标下,pa的计算公式为:

[0051][0052]

在混合雅可比坐标下,pd的计算公式为:

[0053][0054]

椭圆曲线上点乘运算(pointmultiplication,pm)定义为kp=(k/2)p+(k/2)p,其中k为正整数,可以把pm分解为pa和pd两种运算。为加快椭圆曲线上点乘运算的运算速率,实现面积和性能的最佳权衡,本实施例提出一种素数域椭圆曲线密码协处理器,在130nmcmos标准单元库下,该协处理器面积达到222.37k门,最高工作频率可达390mhz,乘法运算时间为215us。该协处理器电路在性能和延迟方面都有较好的优势,非常适合物联网中高速加密和解密的应用。

[0055]

参照图1,本发明实施例提出一种素数域椭圆曲线密码协处理器包括寄存器模块、naf编码模块、运算模块和控制器模块;其中,

[0056]

寄存器模块用于接收输入的原始数据和存储点乘运算过程中产生的坐标数据和中间数据;

[0057]

naf编码模块用于执行naf编码点乘算法,以减少点乘运算过程中的点加运算次数和点倍运算次数;

[0058]

运算模块包括模乘器单元、模平方器单元、第一模加器单元和第二模加器单元,模乘器单元与第一模加器单元和第二模加器单元连接并构成三级流水线结构,以执行模乘运算;模平方器单元与第一模加器单元和第二模加器单元连接并构成三级流水线结构,以执行模平方运算,模乘器单元与模平方器单元并行进行运算;

[0059]

控制器模块用于通过流水的方式控制点乘运算的数据流向。

[0060]

本实施例中,寄存器模块包括随机数寄存器k和随机数寄存器h、坐标寄存器x2、坐标寄存器y2、坐标寄存器x3、坐标寄存器y3和坐标寄存器z3,用于存储椭圆曲线密码算法点乘运算过程中产生的坐标数据和中间运算数据。

[0061]

本实施例中,考虑到使用naff编码点乘算法可以更有效地计算pm,因此在素数域椭圆曲线密码协处理器中增设一个naf编码模块,用于执行naf编码点乘算法,以减少点乘运算过程中的点加运算次数和点倍运算次数。naf编码点乘算法的原理是通过naf编码减少

正整数k中的非零位数,k的naf编码可以表示为其中ki∈{0,

±

1},k

l-1

≠0,且没有两位连续的ki是非零的。naf编码拥有最少的非零数字,约为位长的1/3,使用naf编码点乘算法可以将pm的计算次数缩减为t次pd和t/3次pa。

[0062]

但是利用naf编码点乘算法计算pm时,需要提前将二进制k转化为naf编码,这将浪费大量的时钟周期,参照图2,图2为naf编码点乘算法的示意图,通过预计算h=3k的方法,可以避免naf编码的转换,而代价只是一个额外的寄存器资源。naf编码点乘算法中,通过从左到右同时扫描hi和ki的值,每扫描一位执行一次pd,当hi=1且ki=0时执行一次pa,当hi=0且ki=1时执行一次ps(point subtraction,ps)。由于q-p=q+(-p),where-p=(x,-y)for p=(x,y),ps可以几乎无成本地转换为pa进行计算。

[0063]

接下来,对运算模块中的模乘器单元、模平方器单元、第一模加器单元和第二模加器单元进行说明。

[0064]

模乘运算是ecc密码系统中最重要也是最关键的运算,模乘算法的选择直接影响整个系统的运行效率。对于a,b∈f

p

的有限域模乘,可以先把a和b作为整数相乘,再将结果对p进行取模,其中取模运算计算较为复杂。使用蒙哥马利算法能有效降低模乘的复杂度,蒙哥马利算法的原理是将乘法和取模同时进行,使用成本较低的加法和移位操作来代替取模运算。蒙哥马利算法在计算前后需要对数据进行预处理和后处理,单次计算模乘的效率并不高,但非常适合ecc算法这种需要大量计算的场合。参照图3,图3为普通的蒙哥马利算法的示意图。由图3所示的普通的蒙哥马利算法将一个k-bit的数据a按w位为一字长划分为s=k/w段,使用w-bit*k-bit的乘法器代替了的k-bit*k-bit的乘法器,只需要执行s/w次循环就可以得到蒙哥马利模乘结果,有效降低了硬件面积和功耗的开销。普通的蒙哥马利算法中,步骤2.2到2.4相当于计算了一次r(x)=x*2-w

modp的模约减。参照图4,本发明实施例提出一种改进的蒙哥马利算法,即蒙哥马利快速部分模约减算法。将普通的蒙哥马利算法和nist素数结合起来,使用一种特殊的模约减结构来避免步骤2.2到2.4中的2次乘法,可以快速得到r(x)=x*2-w

modp

256

的结果。

[0065]

改进的蒙哥马利算法的原理是在计算r(x)=x*2-64

mod p

256

时,由于x mod p

256

≡x*(p

256

+1)mod p

256

,p256+1=2

256-2

224

+2

192

+2

96

的低64位全为0,把x表示为x=c*2

64

+l,那么只需要计算r=l>>64mod p

256

=l*(p

256

+1)>>64mod p

256

=(1<<192)-(l<<160)+(l<<128)+(l<<32),就可以得到r(x)=x*(p

256

+1)>>64mod p

256

=c+r mod p

256

的结果。

[0066]

参照图5,模乘器单元与第一模加器单元和第二模加器单元连接并构成三级流水线结构,以执行模乘运算。模乘单元包括乘法运算组件和模约减运算组件,乘法运算组件的输出为模约减运算组件的输入,模约减运算组件的输出流入第一模加器单元和第二模加器单元。其中第一模加器单元和第二模加器单元是ecc系统的公共资源,与模乘单元连接用于执行如图3所示的普通的蒙哥马利算法中的步骤3。模乘运算使用4个64-bit*64-bit的乘法器实现一次64-bit*256-bit的乘法运算,将4个128-bit的中间结果拼接成2个256-bit的数据,运算结果存放在寄存器c0和寄存器c1,表示为mul(ai,b)=c0+c1*2

64

,数据拼接的过程如表2所示。为了减少系统延时和面积,模约减运算组件利用csa加法器代替部分加法器,其中csa257和csa258用于计算如图3所示的普通的蒙哥马利算法中的步骤2.1中的加法u=u+ai*b。由于csa加法器输出的是两个数据,使用64-bit加法器将两个数据的低64-bit相加得到h*2

64

+l的值。表3中给出r的计算方法,通过将1按照表3所示进行拼接,使用96-bit加法器

计算r的高96位,再与低160位的数据拼接在一起,得到r=l>>64mod p

256

的值。csa256用于计算r(x)=c+r mod p

256

,运算结果保存在寄存器d0和寄存器d1中,参与下次循环的计算。循环4次之后,将csa256的运算结果送往第一模加器单元和第二模加器单元执行最后的模加运算,得到蒙哥马利模乘的运算结果a*b*r-1

mod p

256

。

[0067]

表2模乘单元中乘法运算组件的运算数据拼接的过程

[0068][0069]

表3 r的计算方式

[0070][0071]

模乘运算的流程如图6所示,乘法运算组件、模约减运算组件和第一模加器单元和第二模加器单元呈现一个三级流水线结构,执行单次模乘运算需要6个时钟周期,流水线下计算执行一次模乘运算只需要4个时钟周期,使用改进的蒙哥马利算法实现的模乘器单元在面积和性能上都能达到一个较好的平衡。

[0072]

接下来,对模平方器单元进行说明。

[0073]

模平方器单元的设计思路是建立在模乘器单元的基础上的,平方运算作为一种特殊的乘法运算,可以对乘法的中间结果进行合并,省去大约一半的计算量。模约减部分则是使用与模乘器单元相同的蒙哥马利快速部分模约减算法。

[0074]

为了满足r(x)=x*2-64

mod p

256

的结构式,平方运算的输出结果应该在4个时钟周期内全部计算完毕,并且每经过一个时钟周期,输出结果都应该比上一个时钟周期的结果高64位。通过将模平方器的输入数据a以32-bit为一字长划分成8段,将乘法的中间结果进行合并和调整顺序,得到符合r(x)=x*2-64

mod p

256

结构式的4个结果。本实施例设计使用9个32-bit*32-bit的乘法器来实现平方运算,每个时钟周期并行执行9次乘法运算,乘法器的输入通过数据选择器来进行选择,输出的9个64-bit的中间结果按高位到低位表示为result9-result1。平方运算的化简过程如图7所示,每个时钟周期的运算结果中灰色的部分拼接成1个321-bit的数据c2,白色部分拼接成1个256-bit的数据c3,表示为squ(a)=c2+c3*2

33

。图7中平方运算的化简过程一共存在8个无法合并的乘法结果,分别位于前三个时钟周期c2的最低位和最后一个时钟的周期的c2,这导致c2有两种不同的计算方法,c2和c3计算的方法如表4、表5和表6所示。

[0075]

表4前三个时钟周期c2的计算

[0076][0077]

表5第四个时钟周期c2的计算

[0078]

位数320319-256255-192191-128127-6463-0c20result9result7result5result3result1

[0079]

表6 c3的计算

[0080]

位数279-216215-152151-9897-3433-0c3result8result6result4result2 [0081]

模平方器单元的电路结构如图5所示,模平方器单元包括平方计算组件和模约减计算组件,平方计算组件的输出为模约减计算组件的输入,模约减计算组件的输出流入第一模加器单元和第二模加器单元.本实施例中,模约减计算组件电路结构与模乘器单元中的模约减运算组件的电路结构基本相同,但需要根据不同数据的位宽对csa加法器进行修改,其中csa258和csa289用于计算u=u+squ(a)中的加法,64-bit加法器和96-bit加法器用于计算r=l>>64mod p

256

,csa257用于计算r(x)=c+r mod p

256

,运算结果保存在寄存器d2和寄存器d3中,参与下次循环的计算。循环4次之后,将csa257的运算结果送往第一模加器单元和第二模加器单元执行最后的模加运算,得到蒙哥马利模平方的运算结果a2*r-1

mod p

256

。

[0082]

csa257的运算结果在输出到第一模加器单元和第二模加器单元之前需要对其进行验证。模平方器单元的算法流程如图8所示的算法4所示,当算法4循环进行到步骤5的时候,c2输出的最高位为0,c2高65位的值为a7*a7≤(2

32-1)*(2

32-1)=(2

64-2

33

+1),所以c2<2

320-2

289

+2

256

+2

256-1,数据经过csa258和csa289之后u=u+squ(a)<2

320-2

288-2

287

,再经过64位的移位寄存器c<2

256-2

224-2

223

<p

256

,最后在csa257处由于r=(l<<192)-(l<<160)+(l<<128)+(l<<32)<p

256

,因此c+r<2*p

256

,可以直接对csa257的输出结果进行模加运算。

[0083]

模平方运算的流程如图9所示,平方计算组件、模约减计算组件和第一模加器单元和第二模加器单元呈现一个三级流水线结构,以执行模平方运算。单次模平方需要6个时钟周期,流水线下计算一次模平方需要4个时钟周期。模平方器单元的主要资源开销是9个32-bit*32-bit的乘法器,相比起使用4个64-bit*64-bit乘法器的模乘器单元,面积仅为模乘器单元的0.66倍。

[0084]

由表1可知,计算pa需要8m+3s,计算pd需要4m+6s。在选择naf编码点乘算法之后,如果使用单模乘计算pm,将所有的模平方运算用模乘运算代替,总共需要10m*n+11m*n/3=13.67m*n。而如果使用模乘和模平方并行计算pm则需要5m*n+8m*n/3=7.67m*n,计算量仅为原来的0.56倍,因此设计模平方器单元计算pm是非常有必要的。

[0085]

本实施例中,在进行坐标转换时需要用到模逆运算,模逆运算通常使用扩展欧几里得算法来实现,常见的扩展欧几里得算法有二进制算法和四进制算法两种,其中二进制算法非常适合在硬件上实现,只需要循环地执行减法和移位操作就可以求出模逆的结果。二进制算法计算一次模逆平均需要363个时钟周期。四进制算法与二进制算法相比每次循环扫描的位数从1-bit变成了2-bit,速率理论上可以达到二进制算法的两倍,但需要消耗大量的电路资源,不适合在硬件上实现。因此,参照图10,本实施例在二进制算法和四进制算法的基础上提出一种二进制四进制混合算法作为改进的模逆算法,将四进制算法的部分判断条件集成在二进制算法的流程中,执行一次模逆运算大约需要300个时钟周期,仅为二进制算法的83%。

[0086]

在如图10所示的算法5中,u和v的除以4和除以2操作可以通过简单的右移操作来实现,对于x1和x2的除以4和除以2操作需要先判断x1和x2的最低有效位,再通过+p,+2p和+

3p的操作来调整x1和x2的值的最低有效位为0,最后通过右移操作来实现。模逆单元在电路设计上使用2个加法器来更新寄存器u和v的值,使用2个模加器单元来更新寄存器x1和x2的值,其中,加法器的结构如图11所示。为了尽可能地缩减ecc电路系统的面积,本实施例将寄存器u和v与存放输入仿射坐标数据p=(x

p

,y

p

)的寄存器进行复用,将寄存器x1和x2与模加器单元的输入寄存器进行复用。

[0087]

模加器单元作为ecc点乘处理器的公共算术资源,为了满足模逆、模乘、模平方、点加、点倍以及点乘运算中出现的所有功能需求,在原本串连的两个257-bit加法器基础上,添加若干数据选择器和移位寄存器,以实现(a+b)mod p,(a-b)mod p,a/4mod p,a/2mod p,(a-b)/2mod p和a+b的运算。模加器单元在输出上一共设计了4套接口,可以根据不同的需求给其他模块提供输入数据。

[0088]

具体地,参照图12,第一模加器单元包括第一加法器、第二加法器、多个移位寄存器和多个数据选择器,第一加法器与第二加法器串联,多个数据选择器逐级相连并接入第一加法器,以控制输入第一加法器的数据,多个移位寄存器和多个数据选择器连接后接入第二加法器的输入端,第二加法器的输出端接入一个数据选择器后接入2个移位寄存器。第二模加器单元的结构与第一模加器单元的结构相同。

[0089]

本发明实施例基于模乘、模平方和模加运算可以并行计算的特点,将pa和pd运算展开为一系列的有限域运算步骤,并通过控制器模块对各算术逻辑单元的使用进行重新调度和协调,能够有效提高系统的计算速率和数据吞吐量。由于pa和pd的计算顺序存在一定的数据相关性,在计算的开始阶段,控制器模块控制只执行模平方运算,模乘器单元被空置,而在计算的结束阶段,控制器模块控制只执行模乘运算和模加运算,模平方器单元被空置。通过分析naf点乘算法过程中点加和点倍运算可能出现的相邻计算序列,使用首尾相接的方式填补模乘器单元和模平方器单元的空置,在上一步骤的pa或pd运算还没结束时就可以展开对下一步骤的pa或pd运算的计算。pa和pd运算的步骤如表7和表8所示,优化后计算一次pd需要21个时钟周期,计算一次pa需要32个时钟周期,执行一次完整的pm大约需要21*256+32*256/3+300≈8406个时钟周期。

[0090]

表7 pa的计算流程

[0091][0092]

表8 pd的计算流程

[0093][0094]

本实施例提出的一种素数域椭圆曲线密码协处理器,模乘运算和模平方运算可并行运行,在130nm cmos标准工艺下最高工作频率可达到390mhz,加密时间为0.0215ms,面积为222.4kges,面积与时间的性能为4.78,综合性能非常好,非常适合高速加密解密应用。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1