存储器控制器和包括其的存储器系统的制作方法

存储器控制器和包括其的存储器系统

1.相关申请的交叉引用

2.本技术基于并要求于2021年9月8日在韩国知识产权局提交的编号为10-2021-0119579的韩国专利申请的优先权,其公开通过引用整体并入本文。

技术领域

3.本公开涉及存储器控制器和包括其的存储器系统。

背景技术:

4.存储器件的故障可以是存储器件中错误发生的常见因素之一。有缺陷的存储器件可以包括有缺陷的存储器芯片或在存储器系统内部的存储器件之间提供的有缺陷的数据通路。有缺陷的数据通路可能例如由于有缺陷的引脚、有缺陷的数据迹线或扭曲了的故障线而出现。

5.在开发存储器件时通过初级测试来分析故障,但是难以主动地应对在使用存储器件时发生的故障。

6.因此,有必要基于发生在存储器件内部的数据中的错误来预测将发生在存储器件中的故障。

技术实现要素:

7.根据在本文描述的本发明(多个)构思的方面,一种存储器控制器包括故障预测器、纠错码(ecc)管理器和多个ecc引擎。所述故障预测器预测引起发生在存储器件中的错误的故障。ecc管理器基于预测出的所述故障来对所述故障的类型进行分类。所述多个ecc引擎依据所分类的故障的类型并行地执行ecc。故障预测器包括存储器错误分析器(profiler)和存储器故障预测网络。存储器错误分析器接收与错误有关的原始数据,并且将原始数据处理为错误概况(profile),所述错误概况是可用于机器学习的数据。所述存储器故障预测网络接收所述错误概况作为输入,利用所述错误概况来执行所述机器学习,并且预测引起所述错误的故障。

8.根据在本文描述的本发明(多个)构思的方面,一种存储器件包括存储单元阵列和存储器控制器。所述存储单元阵列包括用于存储数据的多个存储单元。存储器控制器控制对所述存储单元阵列的访问。所述存储器控制器包括故障预测器、存储器故障预测网络和ecc管理器。所述故障预测器包括存储器错误分析器和存储器故障预测网络。所述存储器错误分析器接收与发生在所述数据中的错误有关的原始数据,并且将所述原始数据处理为错误概况,所述错误概况是可用于机器学习的数据。所述存储器故障预测网络接收错误概况作为输入,并且利用所述错误概况执行所述机器学习以预测引起所述错误的故障。所述ecc管理器基于所预测的故障来对所述故障的类型进行分类。

9.根据在本文描述的本发明(多个)构思的方面,一种存储器系统包括存储器件和存储器控制器。所述存储器件包括存储单元阵列,所述存储单元阵列包括用于存储数据的多

个存储单元。所述存储器控制器包括故障预测器、ecc管理器和多个ecc引擎。所述故障预测器预测引起发生在所述存储器件中的错误的故障。所述ecc管理器基于预测出的故障对所述故障的类型进行分类。所述多个ecc引擎根据所分类的故障的类型并行地执行ecc。所述故障预测器包括存储器错误分析器和存储器故障预测网络,所述存储器错误分析器接收与发生在所述数据中的错误有关的原始数据并且将所述原始数据处理为错误概况,所述错误概况是可用于机器学习的数据,所述存储器故障预测网络接收所述错误概况作为输入并且利用所述错误概况执行所述机器学习以预测引起所述错误的故障。

附图说明

10.通过参考附图详细地描述本公开的示例性实施例,本公开的以上及其他方面和特征将变得更明显,在附图中:

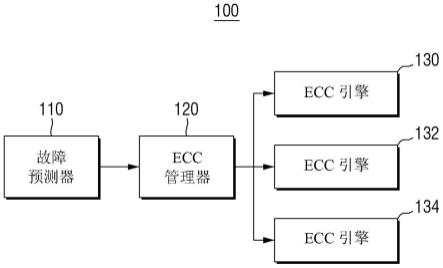

11.图1是根据一些实施例的示出存储器系统的示例框图。

12.图2是根据一些实施例的示出存储器控制器的示例框图。

13.图3是根据一些实施例的示出故障预测器的示例框图。

14.图4是根据一些实施例的示出存储器错误分析器的示例框图。

15.图5、图6和图7是根据一些实施例的用于说明存储器故障预测网络的操作的示例图。

16.图8是用于说明ecc引擎的示例框图。

17.图9是用于说明ecc编码电路的示例性电路图。

18.图10是用于说明ecc解码电路的示例框图。

19.图11是根据一些实施例的用于说明存储器控制器的操作的示例流程图。

20.图12是根据一些实施例的用于说明另一个存储器件的示例框图。

21.图13是根据一些实施例的用于说明另一个存储器系统的示例框图。

22.图14是根据一些实施例的用于说明数据中心的示例框图。

具体实施方式

23.图1是根据一些实施例的示出存储器系统的示例框图。

24.参考图1,根据一些实施例的存储器系统10包括存储器控制器100和存储器件200。

25.存储器控制器100可以总体上控制包括存储器件200的存储器系统10的操作。存储器控制器100可以分析从主机(未示出)提供的命令,并且根据分析结果来控制存储器件200的总体操作。

26.尽管未示出,存储器控制器100可以包括与存储器件200通信的存储器接口。存储器接口可以与许多存储器技术兼容,诸如ddr3(双倍数据速率版本3,由jedec(电子设备工程联合协会)在2007年6月27日最初发布,目前处于版本21)、ddr4(ddr版本4,由jedec在2012年9月公布的初始规范)、lpddr3(由jedec在2013年8月发布的低功率ddr版本3,jesd209-3b)、lpddr4(由jedec在2014年8月最初公布的低功率双数据速率(lpddr)版本4,jesd209-4)、wi02(由jedec在2014年8月最初发布的宽i/o 2(widel02),jesd229-2)、hbm(由jedec在2013年10月最初公布的高带宽存储器dram,jesd235)、ddr5(ddr版本5,由jedec当前讨论)、lpddr5(由jedec当前讨论)、wi03(宽i/o 3,由jedec当前讨论)、hbm2(hbm版本,

由jedec当前讨论)和/或其他,以及基于这些规范的推导或扩展的技术。

27.存储器件200可以包括存储单元阵列210,该存储单元阵列210包括用于存储数据的多个存储单元。

28.用于存储数据的多个存储单元可以是但是不局限于dram、sdram或者sram(静态随机存取存储器)。

29.错误可能发生在存储在存储器件200内部的存储单元阵列210中的数据中。发生在数据中的错误可以是暂时错误或连续错误。

30.例如,暂时错误(或软错误)可以是由随机地影响数据比特的宇宙辐射或环境引起的。这种错误通常可以限制为单个比特或单个列。

31.相比之下,连续错误(或硬错误)可以由存储器件200的故障引起。这种连续错误可以限制为单个比特或单个列。另外,连续错误(或硬错误)可以影响存在于存储单元阵列210中的全部存储单元。

32.在开发存储器件200时通过初级测试等来分析发生在存储器件200中的故障,并且可以在存储器件200中反映测试信息。然而,存储器系统10可能难以主动地应对在用户使用存储器件200或存储器系统10的过程中出现的故障。

33.因此,可以通过存储器控制器100基于发生在从存储单元阵列210接收到的数据中的错误,预测发生在存储器件200中的故障并主动地应对缺陷。

34.将在以下参考图2至图9描述根据一些实施例的存储器控制器100的配置和操作。

35.图2是根据一些实施例的示出存储器控制器的示例框图。

36.在继续之前,应当清楚的是,在本文的包括图2在内的图示出和引用具有诸如“预测器”、“管理器”、“引擎”、“分析器”、“故障预测网络”、“模块”、“预编码器”、“生成器”、“校正器”之类的标签或者与“电路”或“块”类似的相似术语的电路。如在本文描述的本发明构思(多个)的领域中按照惯例,可以按照执行所描述的功能或多个功能的这种标记的元件来描述和示出示例。这些标记的元件等通过诸如逻辑门、集成电路、微处理器、微控制器、存储器电路、无源电子部件、有源电子部件、光学部件、硬连线电路等的模拟和/或数字电路被物理地实现,并且可以可选地被固件和/或软件驱动。电路例如可以被实现在一个或更多个半导体芯片中,或者被实现在诸如印刷电路板等的基板支撑件上。构成这种标记的元件的电路可以通过专用硬件、或者通过处理器(例如,一个或更多个经编程的微处理器和相关联的电路)、或者通过执行标记的元件的一些功能的专用硬件与执行标记的元件的其他功能的处理器的组合来实现。在不背离本公开的范围的情况下,示例的每个标记的元件可以被物理地分成两个或更多个相互作用且分立的电路。同样地,在不背离本公开的范围的情况下,诸如图2的存储器控制器100中的示例的标记的元件可以物理地组合为更复杂的电路。

37.参考图1和图2,存储器控制器100可以包括故障预测器110、ecc管理器120(纠错码管理器)、以及多个ecc引擎130、132和134。

38.故障预测器110可以基于发生在从存储器件200接收的数据中的错误来预测发生在存储器件200中的故障。换句话说,故障预测器110可以基于发生在从外部接收到的(即,从位于存储器控制器100外部的存储器件200的外部接收到的)数据中的错误,预测在存储器件200中正在发生的故障或者将要发生的故障。

39.将通过图3提供对故障预测器110的详细描述。

40.图3是根据一些实施例的示出故障预测器的示例框图。

41.参考图1至图3,存储器控制器100包括存储器错误分析器112和存储器故障预测网络114。

42.存储器错误分析器112可以接收与发生在从存储单元阵列210接收的数据中的错误有关的原始数据。之后,存储器错误分析器112可以将原始数据处理为错误概况,所述错误概况是存储器故障预测网络114执行机器学习的可用数据。

43.将通过图4提供对存储器错误分析器112的详细描述。

44.图4是根据一些实施例的示出存储器错误分析器的示例框图。

45.参考图1至图4,存储器错误分析器112可以包括错误概况预编码器1120、错误信息使用块1122以及错误概况生成器1124。

46.错误概况预编码器1120可以接收与发生在从存储器件200接收的数据中的错误有关的原始数据。

47.原始数据例如可以是与发生在从存储器系统10、存储器件200、存储单元阵列210或存储器控制器100发送的数据中的错误有关的原始数据。

48.错误概况预编码器1120可以对原始数据进行预编码以使原始数据可用于多个错误信息使用模块中的至少一个中,所述多个错误信息使用模块包括错误信息使用块1122中所包括的ttf和tbe计算模块1122a、ecc解码器使用模块1122b、ecc地址计算模块1122c和错误计数使用模块1122d。

49.当与原始数据中所包括的且发生在从存储单元阵列210接收到的数据中的错误有关的错误地址的形式是逻辑地址的形式时,由错误概况预编码器1120执行预编码的操作例如可以包括将错误地址转换为物理地址的操作。

50.例如,错误概况预编码器1120可以对原始数据进行预编码,并将其发送到ttf和tbe计算模块1122a(故障时间(time-to-failure)和时间赌注错误(time bet error)计算模块),使得ttf和tbe计算模块1122a可以计算发生在数据中的错误的ttf值和tbe值。

51.在另一个示例中,错误概况预编码器1120可以对原始数据进行预编码,并将其发送到ecc解码器使用模块1122b,使得ecc解码器使用模块1122b可以使用关于发生在数据中的错误的解码有关信息(例如,错误伴随式(error syndrome)、错误比特的数量等)。

52.作为另一个示例,错误概况预编码器1120可以对原始数据进行预编码,并将其发送到ecc地址计算模块1122c,使得ecc地址计算模块1122c计算关于发生在数据中的错误的地址。

53.作为另一个示例,错误概况预编码器1120可以对原始数据进行预编码,并将其发送到错误计数使用模块1122d,使得错误计数使用模块1122d对发生在数据中的错误的发生次数进行计数。

54.错误信息使用块1122内部包括的错误信息使用模块不局限于该图。

55.错误概况生成器1124可以将从错误信息使用块1122接收的信息处理为错误概况,该错误概况是可用于机器学习的数据。

56.例如,错误概况生成器1124可以生成错误概况,所述错误概况是通过将通过ttf和tbe计算模块1122a计算出的数据中发生的错误的ttf值和tbe值处理为可用于机器学习的数据而获得的。

57.作为另一个示例,错误概况生成器1124可以生成错误概况,所述错误概况是通过将与通过ecc解码器使用模块1122b解码出的数据中发生的错误有关的解码数据处理为可用于机器学习的数据而获得的。

58.作为另一个示例,错误概况生成器1124可以生成错误概况,所述错误概况是通过将与通过ecc地址计算模块1122c计算出的数据中发生的错误有关的地址处理为可用于机器学习的数据而获得的。

59.作为另一个示例,错误概况生成器1124可以生成错误概况,所述错误概况是通过将与通过错误计数使用模块1122d计算出的数据中发生的错误的发生次数处理为可用于机器学习的数据而获得的。

60.错误概况不限于此,并且例如可以是发生在数据中的错误的发生时间、发生在数据中的错误的发生间隔、发生在数据中的错误的发生地址、基于数据中发生的错误生成的伴随式(syndrome)的错误模式,或者已经发生且在数据中累积的错误的发生次数。

61.再次参考图1至图3,存储器故障预测网络114可以使用通过存储器错误分析器112接收的错误概况来执行机器学习。存储器错误分析器112可以通过输入错误概况来预测发生在存储器系统10或存储器件200中的故障以执行机器学习。此时,存储器故障预测网络114可以利用附加信息,该附加信息与可以从存储器件200内部或外部接收到的数据中发生的错误有关。

62.将通过图5至图7描述可用于存储器故障预测网络114以执行机器学习的网络的示例。

63.图5、图6和图7是根据一些实施例的用于说明存储器故障预测网络的操作的示例图。

64.参考图1至图5,存储器故障预测网络114a可以使用人工神经网络执行深度学习。

65.例如,存储器故障预测网络114a可以通过经由在输入层和输出层之间形成的隐藏层输入错误概况,预测发生在存储器系统10或存储器件200中的故障。

66.参考图1至图4和图6,存储器故障预测网络114b可以使用人工神经网络执行深度学习。

67.例如,存储器故障预测网络114b可以使用dnn(深度神经网络)执行深度学习。可以通过经由在输入层和输出层之间形成的多个隐藏层输入错误概况来预测发生在存储器系统10或存储器件200中的故障。

68.参考图1至图4和图7,存储器故障预测网络114c可以使用人工神经网络执行深度学习。

69.例如,存储器故障预测网络114c可以使用cnn(卷积神经网络)执行深度学习。从已经接收了错误概况的第一层1140形成卷积层1141。此时,卷积层1141的数量不局限于该图。在那之后,从卷积层1141形成池化层1142。可以再次从池化层1142形成卷积层1143。另外,可以通过卷积层1143形成池化层1144。在那之后,可以通过池化层1144形成全连接层1145。形成卷积层和形成池化层的重复的数量不限于该图的次数。

70.因此,存储器故障预测网络114c可以得出预测结果1146,所述预测结果1146是通过预测将发生在存储器系统10或存储器件200中的故障而获得的。预测结果1146例如可以是柔性最大值。

71.再次参考图1和图2,ecc管理器120可以基于由故障预测器110预测的故障来划分故障的类型。根据故障的类型,每个故障然后可以被发送到可以纠正故障的ecc引擎130、132或134。用作参考,该图中示出的ecc引擎130、132和/或134的数量不限于此。

72.例如,多个ecc引擎130、132和134之一可以执行按需(demand)存储器清理(scrubbing)操作。可以对单比特错误或多比特错误执行按需存储器清理。在主机操作系统对针对存储器件200的访问进行响应的过程中,可以对单比特错误或多比特错误执行按需存储器清理。

73.作为另一个示例,多个ecc引擎130、132和134之一可以执行巡检(patrol)存储器清理操作。在从主机操作系统到存储器件200的访问请求之前,可以单独地执行巡检存储器清理操作。

74.多个ecc引擎130、132和134之一可以使用擦除编码来纠正故障,但不限于此。或者,多个ecc引擎130、132和134之一可以通过备份(sparing)来修复故障。

75.作为另一个示例,多个ecc引擎130、132和134之一可以使用奇偶校验位纠正故障。将通过图8至图10对这一点进行详细地描述。用作参考,ecc引擎130的描述可以被应用于其他ecc引擎132和ecc引擎134,是不言而喻的。

76.图8是用于说明ecc引擎的示例框图。

77.参考图1至图8,ecc引擎130可以包括ecc编码电路510和ecc解码电路520。用作参考,ecc引擎130的描述也可适用于其他ecc引擎132和/或134,是不言而喻的。

78.ecc编码电路510可以响应于ecc控制信号ecc_con来生成用于要被写入存储单元阵列210的存储单元的写入数据wdata[0:63]的奇偶校验位eccp[0:7]。奇偶校验比特位eccp[0:7]可以被存储在ecc单元阵列223中。根据实施例,ecc编码电路510可以响应于ecc控制信号ecc_con生成用于要被写入存储单元的写入数据wdata[0:63]的奇偶校验位eccp[0:7],所述存储单元包括存储单元阵列210的有缺陷的单元。

[0079]

ecc解码电路520可以响应于ecc控制信号ecc_con,利用从存储单元阵列210的存储单元读取的读取数据rdata[0:63]和从ecc单元阵列223读取的奇偶校验位ecc[0:7],来校正错误比特数据,并且可以输出错误校正后的数据data[0:63]。根据实施例,ecc解码电路520可以响应于ecc控制信号ecc_con,利用从包括了存储单元阵列210的有缺陷的单元的存储单元读取的读取数据[0:63]和从ecc单元阵列223读取的奇偶校验位eccp[0:7],来校正错误比特数据,并且可以输出错误校正后的数据data[0:63]。

[0080]

图9是用于说明ecc编码电路的示例电路图。

[0081]

参考图9,ecc编码电路510可以包括奇偶校验生成器511,所述奇偶校验生成器511响应于ecc控制信号ecc_con来接收64比特写入数据wdata[0:63]和基础比特b[0:7],并且利用xor阵列计算来生成奇偶校验位eccp[0:7]。基础比特b[0:7]是用于生成64比特写入数据wdata[0:63]的奇偶校验位eccp[0:7]的比特,并且可以通过例如b’00000000比特来配置。基础比特b[0:7]可以利用其他特定比特而非b’00000000比特。

[0082]

图10是用于说明ecc解码电路的示例框图。

[0083]

参考图10,ecc解码电路520包括伴随式生成器521、系数计算器522、1比特错误位置检测器523和错误校正器524。伴随式生成器521响应于ecc控制信号ecc_con接收64比特读取数据和8比特奇偶校验位eccp[0:7],并且可以利用xor阵列计算来生成伴随式数据s

[0;7]。系数计算器522可以使用伴随式数据s[0:7]来计算错误位置公式的系数。错误位置公式是基于错误比特的倒数的公式。1比特错误位置检测器523可以利用计算出的错误位置公式来计算1比特错误的位置。错误校正器524可以基于1比特错误位置检测器523的检测结果来确定1比特错误位置。错误校正器524通过根据确定的1比特错误位置信息将在64比特读取数据rdata[0:63]中的其中发生错误的比特的逻辑值反相来校正错误,并且可以输出错误校正后的64比特数据data[0:63]。

[0084]

图11是根据一些实施例的用于说明存储器控制器的操作的示例流程。

[0085]

参考图1至图4和图11,错误可以发生在存储在存储单元阵列210中的数据中(s100)。

[0086]

故障预测器110然后接收与在数据中发生的错误有关的原始数据(s110)。此时,故障预测器110可以通过原始数据预测引起发生在数据中的错误的故障。例如,故障预测器110可以生成预测引起发生在数据中的错误的故障的值作为柔性最大值。

[0087]

此时,可以确定柔性最大值是否具有大于指定的任意值的值(s120)。如果确定柔性最大值不大于指定的任意值(否),则可以等待直到另一个错误发生。然而,如果确定柔性最大值大于指定的任意值(是),则确定在预测的故障中是否存在无法校正的错误(ue)的可能性(s130)。

[0088]

此时,如果确定在预测的故障中存在无法校正的错误(是),则可以向ecc管理器120发送预测的故障。同时,存储器控制器100可以向存储器系统10的用户通知预测的故障具有无法校正的错误。

[0089]

如果确定在预测的故障中不存在无法校正的错误(否),则存储器控制器100可以向存储器系统10的用户发送错误发生事实。

[0090]

图12是根据一些实施例的用于说明另一个存储器件的示例框图。

[0091]

参考图12,根据一些实施例的存储器控制器100可以被放置在存储器件200内部。

[0092]

图13是根据一些实施例的用于说明另一个存储器系统的示例框图。

[0093]

参考图13,存储器系统2000可以基本上是诸如移动式电话、智能电话、平板机个人计算机(pc)、可穿戴装置、保健装置或iot(物联网)装置之类的移动系统。然而,图13的存储器系统2000不一定局限于移动系统,而可以是个人计算机、膝上型计算机、服务器、媒体播放机或诸如导航的汽车装置。

[0094]

参考图13,存储器系统2000可以包括主处理器2100、存储器2200a和2200b以及存储装置2300a和2300b,并且还可以包括图像捕获装置2410、用户输入装置2420、传感器2430、通信装置2440、显示器2450、扬声器2460、电力提供装置2470和连接接口2480中的一个或更多个。

[0095]

存储器2200a和2200b可以是如上所述的存储器件200。

[0096]

主处理器2100可以控制存储器系统2000的总体操作,更具体地,形成存储器系统2000的其他部件的操作。这种主处理器2100可以被实现为通用处理器、专用处理器、应用处理器等等。

[0097]

主处理器2100可以包括一个或更多个cpu核2110,并且还可以包括用于控制存储器2200a和2200b和/或存储装置2300a和2300b的控制器2120。

[0098]

控制器2120可以是如上所述的存储器控制器100。

[0099]

根据实施例,主处理器2100还可以包括加速器2130,所述加速器2130是用于诸如ai(人工智能)数据计算的高速数据计算的专用电路。这种加速器2130可以包括gpa(图形处理单元)、npu(神经处理单元)和/或dpa(数据处理单元),并且也可以被实现为与主处理器2100的其他部件物理无关的单独的芯片。

[0100]

存储器2200a和2200b可以用作存储器系统2000的主存储单元,并且可以包括诸如sram和/或dram之类的易失性存储器,而且也可以包括诸如闪存、pram和/或rram之类的非易失性存储器。存储器2200a和2200b也可以与主处理器2100一样被实现在同一封装内部。

[0101]

存储装置2300a和2300b可以作为用于存储数据的非易失性存储装置而不管电源供应的存在与否,并且相比于存储器2200a和2200b可以具有相对大的存储容量。存储装置2300a和2300b可以包括存储控制器2310a和2310b以及用于在存储控制器2310a和2310b的控制下存储数据的非易失性存储器2320a和2320b(nvm)。非易失性存储器2320a和2320b可以包括2d(二维)结构或3d(三维)v-nand(垂直nand)结构的闪存,但是也可以包括诸如pram和/或rram之类的其他类型的非易失性存储器。

[0102]

存储装置2300a和2300b可以在物理地与主处理器2100分开的状态中被包括在存储器系统2000中,或者可以与主处理器2100一样被实现在同一封装内部。此外,存储装置2300a和2300b具有诸如ssd(固态设备)或存储卡之类的形式,并且因此可以通过诸如稍后描述的连接接口2480的接口与存储器系统2000的其他部件可拆卸地结合。这种存储装置2300a和2300b可以是被应用诸如ufs(通用闪存存储)、emmc(嵌入式多媒体卡)或nvme(高速非易失性存储器)之类的标准协议的装置,但是不是必然限于此。

[0103]

图像捕获装置2410可以捕获静止图像或活动图像,并且可以是相机、录像摄像机和/或网络照相机。

[0104]

用户输入装置2420可以接收从存储器系统2000的用户输入的各种类型的数据,并且可以是触摸板、小键盘、键盘、鼠标、麦克风等。

[0105]

传感器2430可以感测可以从存储器系统2000外部获取的各种类型的物理量,并且将感测的物理量转换为电信号。这种传感器2430可以是温度传感器、压力传感器、照度传感器、位置传感器、加速度传感器、生物传感器和/或陀螺仪传感器等等。

[0106]

通信装置2440可以根据各种通信协议向存储器系统2000外部的其他装置和从存储器系统2000外部的其他装置发送和接收信号。这种通信装置2440可以被实现为包括天线、收发器和/或调制解调器等等。

[0107]

显示器2450和扬声器2460可以用作输出装置,所述输出装置分别向存储器系统2000的用户输出视觉信息和听觉信息。

[0108]

电力提供装置2470可以适当地转换从存储器系统2000中配备的电池(未示出)和/或外部电源提供的电力,并且将电力提供给存储器系统2000的每个组成元件。

[0109]

连接接口2480可以提供存储器系统2000与外部装置之间的连接,所述外部装置可以连接到存储器系统2000以向存储器系统2000发送数据和从存储器系统2000接收数据。连接接口2480可以以各种接口类型被实现,诸如ata(先进技术附件)、sata(串行ata)、e-sata(外部sata)、scsi(小型计算机小接口)、sas(串行连接scsi)、pci(外围组件互联)、pcie(高速pci)、nvme、ieee 1394、usb(通用串行总线)、sd(安全数字)卡、mmc(多媒体卡)、emmc、ufs、eufs(嵌入通用闪存存储)和cf(紧凑式闪存)卡接口。

[0110]

图14是根据一些实施例的用于说明数据中心的示例框图。

[0111]

参考图14,数据中心3000是收集各种类型的数据并提供服务的设施,并且也可以称作数据存储中心。数据中心3000可以是用于搜索引擎和数据库操作的系统,并且可以是由诸如银行或政府机构之类的团体所使用的计算系统。数据中心3000可以包括应用服务器3100至3100n以及存储服务器3200至3200m。可以根据实施例来不同地选择应用服务器3100至3100n的数量和存储服务器3200至3200m的数量,并且应用服务器3100至3100n的数量和存储服务器3200至3200m的数量可以彼此不同。

[0112]

应用服务器3100或存储服务器3200可以包括处理器3110和3210以及存储器3120和3220中的至少一者。以存储服务器3200为示例,处理器3210可以控制存储服务器3200的总体操作,并且访问存储器3220以执行加载到存储器3220中的命令和/或数据。

[0113]

存储器3220可以是ddr sdram(双数据速率同步dram)、hbm(高带宽存储器)、hmc(混合存储立方)、dimm(双列直插存储模块)、optane dimm和/或nvmdimm(非易失性dimm)。

[0114]

存储器3220可以是如上所述的存储器件200。

[0115]

根据实施例,可以不同地选择存储服务器3200中所包括的处理器3210的数量和存储器3220的数量。在实施例中,处理器3210和存储器件3220可以提供处理器-存储器对。在实施例中,处理器3210的数量和存储器3220的数量可以彼此不同。控制器3210可以包括单核处理器或多核处理器。存储服务器3200的前述说明也可以类似地应用于应用服务器3100。根据实施例,应用服务器3100可以不包括存储装置3150。存储服务器3200可以包括至少一个或更多个存储装置3250。可以根据实施例不同地选择存储服务器3200中所包括的存储装置3250的数量。

[0116]

如以上阐述的,基于发生在数据中的错误对于存储器控制器提高了预测发生在存储器中的故障的预测准确度。

[0117]

基于发生在数据中的错误对于存储器件提高了预测发生在存储器中的故障的预测准确度。

[0118]

基于发生在数据中的错误对于存储器系统提高了预测发生在存储器中的故障的预测准确度。

[0119]

尽管已经参考附图在上文描述了本公开的实施例,但本领域技术人员将理解的是,本公开不限于此,并且在不背离其技术思想或基本特征的情况下可以以许多不同的形式来实现。因此,应当理解,在本文阐述的实施例在各方面都仅仅是示例并且不进行限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1