一种基于CNN的可配置目标检测硬件加速优化方法

一种基于cnn的可配置目标检测硬件加速优化方法

技术领域

1.本发明涉及网络硬件优化技术领域,尤其是一种基于cnn的可配置目标检测硬件加速优化方法。

背景技术:

2.在深度学习、人工智能发展下,目标检测应用场景越来越广泛,并且在精度和速度上都取得了良好效果。但是在发展过程中,目标检测模型数据量和计算量的增加使得云端技术不能很好地处理传统边端cpu进行目标检测的实时性要求。同时,随着应用场景逐步下沉,目标检测边端应用普及程度大大增加,这就对实时性和存储提出了更大挑战。而利用数据源中心的边端资源来部署基于深度学习的目标检测模型可以在延迟和能效上表现出较好效果,并逐渐成为一种理想解决方法。

3.基于cnn的目标检测模型推理过程中主要延时在于cnn的计算,因此需要硬件来对cnn进行加速运算,从而满足边端目标检测实时性和功耗需求。在边端对cnn进行加速目前主要有三种平台:图像处理单元(graphics processing unit,gpu)、专用集成电路(application specific integrated circuit,asic)和现场可编程门阵列(field programmable gate array,fpga)。gpu加速在算力和适配性上表现优异,但是其在计算过程会出现高功耗问题,在一些生活化的边端场景就不那么适用。利用asic在边端对神经网络进行加速能获得较高性能和良好能效,但是开发时间大,难度较大,不利于迭代。而fpga中的硬件计算资源dsp并没有很好地进行利用,导致dsp计算效率较低。

技术实现要素:

4.有鉴于此,本发明实施例提供一种计算效率高的,一种基于cnn的可配置目标检测硬件加速优化方法。

5.第一方面,本发明实施例提供了一种基于cnn的可配置目标检测硬件加速优化方法,包括:

6.对目标网络模型的目标层数据进行前处理;

7.接收并传输所述前处理后的目标网络模型的模型数据至目标缓存;

8.将所述目标缓存中的所述模型数据进行编排处理,输出至dsp进行前项推理计算;

9.根据所述前项推理计算后的模型数据存储到输出缓存;

10.基于发送控制信号,将所述输出缓存的数据写到外部存储。

11.可选地,所述对目标网络模型的目标层数据进行前处理,包括:

12.在所述目标网络模型的卷积层和激活层插入histogram observer;

13.通过量化机制,对目标网络模型的卷积层数据和激活层数据进行量化处理。

14.可选地,所述接收并传输所述前处理后的目标网络模型的模型数据至目标缓存,包括:

15.采用axi-stream协议传输所述前处理后的目标网络模型的模型数据,将所述模型

数据定义为axi-stream流数据;

16.通过slave_axis_interface模块接收所述axi-stream流数据;

17.根据所述slave_axis_interface模块的状态信号开始或结束所述axi-stream流数据的传输任务;

18.在所述axi-stream流数据的传输任务中,通过所述slave_axis_interface模块产生缓存写地址将所述axi-stream流数据写入目标缓存。

19.可选地,所述目标缓存包括ifm_buffer和weight_buffer,所述将所述目标缓存中的所述模型数据进行编排处理,输出至dsp进行前项推理计算,包括:

20.根据所述模型数据的特征图尺寸,通过ifm_buffer配置行缓存深度,生成3

×

3矩阵输出到dsp;通过weight_buffer同步输出数据到所述dsp;

21.基于所述ifm_buffer和weight_buffer的输出数据,通过dsp双乘法器封装技术进行两组卷积的前项推理计算。

22.可选地,所述通过dsp双乘法器封装技术进行两组卷积的前项推理计算这一步骤中,包括:

23.对dsp计算过程的int18类型数据进行饱和处理,得到int16类型数据;

24.将int16类型数据与量化系数相乘,得到int32类型数据;

25.通过右移舍入方式将int32类型数据再次变为int16类型数据,并进行饱和处理得到int8类型数据。

26.可选地,所述根据所述前项推理计算后的模型数据存储到输出缓存,包括:

27.将所述前项推理计算后的模型数据经过池化处理和激活处理,输出到ofm_buffer进行存储。

28.可选地,所述基于发送控制信号,将所述输出缓存的数据写到外部存储,包括:

29.通过master_axis_interface模块接收主机的send_enable信号,进行数据读处理;

30.采用axi-stream协议将所述输出缓存的数据写到所述主机的外部存储。

31.第二方面,本发明实施例提供了一种基于cnn的可配置目标检测硬件加速优化装置,包括:

32.第一模块,用于对目标网络模型的目标层数据进行前处理;

33.第二模块,用于接收并传输所述前处理后的目标网络模型的模型数据至目标缓存;

34.第三模块,用于将所述目标缓存中的所述模型数据进行编排处理,输出至dsp进行前项推理计算;

35.第四模块,用于根据所述前项推理计算后的模型数据存储到输出缓存;

36.第五模块,用于基于发送控制信号,将所述输出缓存的数据写到外部存储。

37.第三方面,本发明实施例提供了一种电子设备,包括处理器以及存储器;

38.所述存储器用于存储程序;

39.所述处理器执行所述程序实现如前面所述的方法。

40.第四方面,本发明实施例提供了一种计算机可读存储介质,所述存储介质存储有程序,所述程序被处理器执行实现如前面所述的方法。

41.本发明实施例还公开了一种计算机程序产品或计算机程序,该计算机程序产品或计算机程序包括计算机指令,该计算机指令存储在计算机可读存储介质中。计算机设备的处理器可以从计算机可读存储介质读取该计算机指令,处理器执行该计算机指令,使得该计算机设备执行前面的方法。

42.本发明的实施例首先对目标网络模型的目标层数据进行前处理;接收并传输所述前处理后的目标网络模型的模型数据至目标缓存;将所述目标缓存中的所述模型数据进行编排处理,输出至dsp进行前项推理计算;根据所述前项推理计算后的模型数据存储到输出缓存;基于发送控制信号,将所述输出缓存的数据写到外部存储。本发明通过对目标缓存的数据基于dsp进行了可配置设计的编排处理,能够使模型数据适应硬件计算方式,进而提高dsp的计算效率,实现基于cnn的可配置目标检测硬件加速优化。

附图说明

43.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

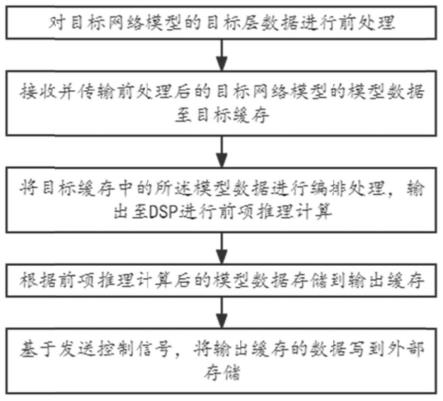

44.图1为本发明实施例提供的整体步骤流程图;

45.图2为本发明实施例提供的基于fpga的可配置cnn目标检测硬件加速ip总体框图;

46.图3为本发明实施例提供的基于符号位扩展的双乘法器封装计算流程示意图;

47.图4为本发明实施例提供的卷积加速器ip整体流水线设计示意图。

具体实施方式

48.为了使本技术的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本技术进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本技术,并不用于限定本技术。

49.针对现有技术存在的问题,第一方面,本发明提供了一种基于cnn的可配置目标检测硬件加速优化方法,如图1所示,方法包括以下步骤:

50.对目标网络模型的目标层数据进行前处理;

51.接收并传输前处理后的目标网络模型的模型数据至目标缓存;

52.将目标缓存中的模型数据进行编排处理,输出至dsp进行前项推理计算;

53.根据前项推理计算后的模型数据存储到输出缓存;

54.基于发送控制信号,将输出缓存的数据写到外部存储。

55.可选地,对目标网络模型的目标层数据进行前处理,包括:

56.在目标网络模型的卷积层和激活层插入histogram observer;

57.通过量化机制,对目标网络模型的卷积层数据和激活层数据进行量化处理。

58.可选地,接收并传输前处理后的目标网络模型的模型数据至目标缓存,包括:

59.采用axi-stream协议传输前处理后的目标网络模型的模型数据,将模型数据定义为axi-stream流数据;

60.通过slave_axis_interface模块接收axi-stream流数据;

61.根据slave_axis_interface模块的状态信号开始或结束axi-stream流数据的传输任务;

62.在axi-stream流数据的传输任务中,通过slave_axis_interface模块产生缓存写地址将axi-stream流数据写入目标缓存。

63.可选地,目标缓存包括ifm_buffer和weight_buffer,将目标缓存中的模型数据进行编排处理,输出至dsp进行前项推理计算,包括:

64.根据模型数据的特征图尺寸,通过ifm_buffer配置行缓存深度,生成3

×

3矩阵输出到dsp;通过weight_buffer同步输出数据到dsp;

65.基于ifm_buffer和weight_buffer的输出数据,通过dsp双乘法器封装技术进行两组卷积的前项推理计算。

66.可选地,通过dsp双乘法器封装技术进行两组卷积的前项推理计算这一步骤中,包括:

67.对dsp计算过程的int18类型数据进行饱和处理,得到int16类型数据;

68.将int16类型数据与量化系数相乘,得到int32类型数据;

69.通过右移舍入方式将int32类型数据再次变为int16类型数据,并进行饱和处理得到int8类型数据。

70.可选地,根据前项推理计算后的模型数据存储到输出缓存,包括:

71.将前项推理计算后的模型数据经过池化处理和激活处理,输出到ofm_buffer进行存储。

72.可选地,基于发送控制信号,将输出缓存的数据写到外部存储,包括:

73.通过master_axis_interface模块接收主机的send_enable信号,进行数据读处理;

74.采用axi-stream协议将输出缓存的数据写到主机的外部存储。

75.第二方面,本发明实施例提供了一种基于cnn的可配置目标检测硬件加速优化装置,包括:

76.第一模块,用于对目标网络模型的目标层数据进行前处理;

77.第二模块,用于接收并传输前处理后的目标网络模型的模型数据至目标缓存;

78.第三模块,用于将目标缓存中的模型数据进行编排处理,输出至dsp进行前项推理计算;

79.第四模块,用于根据前项推理计算后的模型数据存储到输出缓存;

80.第五模块,用于基于发送控制信号,将输出缓存的数据写到外部存储。

81.本发明方法实施例的内容均适用于本装置实施例,本装置实施例所具体实现的功能与上述方法实施例相同,并且达到的有益效果与上述方法达到的有益效果也相同。

82.本发明实施例的另一方面还提供了一种电子设备,包括处理器以及存储器;

83.所述存储器用于存储程序;

84.所述处理器执行所述程序实现如前面所述的方法。

85.本发明方法实施例的内容均适用于本电子设备实施例,本电子设备实施例所具体实现的功能与上述方法实施例相同,并且达到的有益效果与上述方法达到的有益效果也相同。

86.本发明实施例的另一方面还提供了一种计算机可读存储介质,所述存储介质存储有程序,所述程序被处理器执行实现如前面所述的方法。

87.本发明方法实施例的内容均适用于本计算机可读存储介质实施例,本计算机可读存储介质实施例所具体实现的功能与上述方法实施例相同,并且达到的有益效果与上述方法达到的有益效果也相同。

88.本发明实施例还公开了一种计算机程序产品或计算机程序,该计算机程序产品或计算机程序包括计算机指令,该计算机指令存储在计算机可读存储介质中。计算机设备的处理器可以从计算机可读存储介质读取该计算机指令,处理器执行该计算机指令,使得该计算机设备执行前面的方法。

89.下面详细描述本发明的地波雷达流场计算方法的实现原理:

90.首先需要说明的是,在边端部署目标检测模型的本质在于部署神经网络,传统方法是采用以arm为基础的中央处理器(central processing unit,cpu)来进行部署,存在算力不足情况,能效较低,同时受限于边端设备的资源限制,很难存储大容量的数据。

91.为了加速传统边端cnn目标检测计算速度、解决能效低问题,许多学者结合fpga硬件平台在算法、系统、卷积、循环等方面提出了优化设计,能够大大加快卷积计算过程,但是对于fpga中的硬件计算资源dsp并没有很好地进行利用,导致dsp计算效率较低。而且对于边端部署神经网络,网络模型的日益增长使得部署难度也在增加。所以对数据进行压缩也是边端加速主要的一个研究难点之一。同时,当前很多基于目标检测神经网络硬件加速器是为了某一个特定应用进行设计的,在应用场景发生变化时,很难进行适配性修改,不能很好地匹配网络特性。

92.有鉴于此。针对现有技术存在的问题,本发明提出一种基于cnn的可配置目标检测硬件加速优化方法,该设计通过基于符号位扩展的dsp双乘法器封装技术来加速卷积计算过程,提高dsp计算效率。同时对cnn目标检测网络模型进行了可配置设计,使得该设计可以匹配目标检测不同层输入特征图尺寸,最后将该设计进行细粒度流水线设计并封装成ip。该设计总体分为五个部分:数据前处理部分、数据接收部分、数据计算存储部分、数据发送部分和控制及流水线方案部分。

93.本发明的设计总体款图如图2所示,首先,该设计利用pytorch的量化机制对数据进行前处理,针对网络模型中卷积层和激活层数据进行int8量化处理得到量化参数。

94.然后,该设计通过数据接收模块读取输入图片、网络权重、偏置和激活函数值,并在控制模块控制下,通过axi-stream协议读取数据信息到相应的缓存中。

95.接着,该设计将读取到的数据送入数据计算部分进行前向推理计算,该部分需要对读取到的数据进行重新编排使得硬件计算与卷积神经网络计算过程数据排布相适配,同时要充分利用fpga的硬件计算资源dsp和存储资源bram来进行mac计算,并将网络前向推理完成后的结果存储到加速器的输出缓存中。

96.进一步,该设计通过数据发送模块在控制器的控制下将输出缓存中的数据写到外部存储上,数据之间传输还是通过axi-stream协议。

97.最后,对设计全过程进行了细粒度流水线方案设计,并将各个设计模块通过vivado进行封装形成可配置ip。

98.具体步骤说明如下:

99.1、数据前处理

100.数据前处理主要是针对目标检测模型中卷积层和激活函数,通过pytorch进行量化处理,转换精度是int8类型,在量化之前需要在网络每一层插入histogram observer观察器,这两个observer观察器用来记录浮点数的最大值和最小值,然后通过一定数据量的数据样本对网络模型进行前向推理;推理过程中histogram observer观察器会记录下数据的分布情况并计算出量化参数。通过上述步骤得到的量化因子和零点值可以将其转换为定点运算所需要的参数:mult、shift、izp、ozp和azp。然后根据检测模型结构将卷积相关系数同量化参数全部封装到配置文件sg.bin文件,对于量化后的权重数据按照8输出通道进行reshape重塑,并将权重数据、量化后偏置数据以及量化后激活值数据分别输出到相应的bin文件中。

101.2、数据接收部分

102.数据接收部分采用axi-stream协议来进行网络模型数据的传输,通过设计一个slave_axis_interface模块来接收axi-stream流数据。slave_axis_interface模块内部设置了三个状态,在接收到recv_enable信号时表示接受任务开始,状态从空闲态转换到接收状态,当模块slave_axis_interface端口接收到tlast信号表示最后一组传输数据,并在下一周期转换到任务完成状态。同时,模块需要产生缓存写地址和接收主机发送过来的写数据。由于在计算过程中涉及缓存主要有4部分:ifm_buffer、weight_buffer、bias_buffer和leakyrelu_buffer,但是在数据接收过程一次性只能接收一种数据,因此可以通过2bit信号进行数据的发送选择。

103.3、数据计算存储部分

104.在进行数据计算时,其中ifm_buffer会根据本次卷积输入特征图的尺寸来配置行缓存的深度生成3

×

3矩阵便于卷积计算。具体来说,就是ifm_buffer以乒乓操作形式进行数据输送,输送数据根据当前cnn目标检测网络输入特征图尺寸进行选择,中间部分数据的缓存通过移位寄存器进行实现,选择信号控制mux来完成选择过程。最后将输出的3

×

3矩阵送入到dsp进行计算。

105.在ifm_buffer进行输出的同时,weight_buffer也同步输出到dsp进行计算。对于卷积计算中的单个卷积核weight_buffer都配备了一个双端口ram。在写过程中一次性写入n个卷积核单通道的值,然后在输入特征图通道上遍历,完成卷积核n

×

c个值的写入过程,当完成一轮写入过程后,在下一次写入过程中将地址加1来接收下一轮的写数据;读过程中一次性将所有通道的数据读出,即同时读取n

×

c个通道的值。偏置数据和激活函数值一样,其数目取决于当前输出特征图通道数,可以通过配置相对应的bram来匹配运算。

106.由于ifm_buffer和weight_buffer取出的数据都是int8类型的,因此通过在单个dsp实现两组卷积计算来加快卷积计算效率并提高dsp计算效率。计算过程如图3所示。具体来说,对于两个int8的乘法计算a

×

b,d

×

b,可以等效成(a+d)

×

b。对于数据a,需要其符号位进行1bit扩展,然后将扩展后的数据整体左移18比特后输入到dsp端口;对于输入数据d需要将符号位扩展至27位处再输入到dsp端口;对于因子b,将其按照符号位扩展至18比特后输入到dsp端口。经过运算后得到的结果p会从dsp的输出端口输出,其中p[33:18]存放着a

×

b的结果,p[15:0]存放着d

×

b的结果。通过共享输入特征图可以完成单个dsp与两个卷积核的乘法计算,如果采用串行方式,对于一个3

×

3的卷积来说,需要经过9次操作后才能

将乘法计算完成,效率较低,因此可以增大硬件资源来提高计算效率。对于每个卷积采用9个dsp资源来进行计算,计算速度将增加9倍,然后通过三输入加法器树累加九个乘积值得到一个卷积的计算结果,其中加法操作延时只有两个时钟周期。

[0107]

在进行dsp计算过程中,输入特征图和权重值都是int8类型的,但是int8与int8进行乘法操作会得到int16类型数据,再进行累加操作会导致数据位宽增加至int32,但在实际实验当中发现累加值只需int18就能保证绝大多数激励不溢出,因此在考虑fpga资源情况下,可以使用int18做累加运算;接着,对int18数据作饱和截断到int16,再与量化系数scale相乘得到int32;最后,通过向最近的整数右移舍入方式将数据再次变为int16,并作饱和处理将数据重新变为int8类型。经过伸缩变换后的值基本与使用神经网络框架推理结果一致。量化后数据经过池化、激活后输出到ofm_buffer进行存储。

[0108]

4、数据发送部分

[0109]

数据发送部分是将计算结果从ofm_buffer输出到主机的过程,也是数据读过程。读过程信号在模块master_axis_interface产生,当master_axis_interface模块接收到主机send_enable信号命令并且双方axi-stream接口满足握手条件时,模块开始产生输出缓存读地址,其形式由基地址+控制模块输出的偏移地址得到,根据本次卷积参数在状态机控制下完成数据发送,并将输出完成信号重新发回到主机提示数据发送完成。

[0110]

5、控制及流水线方案部分

[0111]

上述计算过程均需在控制模块控制下进行,故根据需求进行了4个寄存器的设计,分别是:硬件加速器控制寄存器、硬件量化参数寄存器、硬件量化零点寄存器和硬件加速器权重和偏置缓存地址寄存器。这4个寄存器都是32位的,其中控制寄存器是对总体任务的调度,其包括了数据收发、卷积开始结束、地址信息等信号;量化参数寄存器包括两个量化参数:量化因子和量化移位值;量化零点寄存器对应的是量化计算中输入值、权重值和输出值的量化零点;加速器权重和偏置缓存地址寄存器对应的是卷积计算过程中加速器读取权重、偏置值的读地址信息。

[0112]

在进行前向推理过程中,加速器首先需要完成主机传入进来的数据接收,接收任务需要根据硬件加速器控制寄存器中recv_enable信号值开始进行数据接收,在完成数据接收后,通过recv_done信号来指示接收数据任务完成。同理,在进行卷积任务时,通过conv_start和conv_done信号来进行卷积运行状态的转移,在卷积任务完成后,输出控制信号conv_shutdown来指示加速器核现在在执行卷积任务还是在执行其他任务。发送任务同接收任务是一致的。对于三个任务来说,每一次使能前都会有一个全局信号task_vaild信号来指示任务开始,每个任务完成后都会将task_done信号拉高表示本次任务完成。

[0113]

对于上述操作希望每个时钟周期都能输出一个值,因此对整个操作进行了细粒度流水线设计,流水线过程如图4所示。数据以流数据形式经过axi-stream接口输入到输入缓存上,然后在硬件加速器控制寄存器的控制下配置行缓存生成3

×

3大小的卷积窗口,接着经过dsp乘法操作和级联的两级三输入加法器完成卷积运算,最后通过accumulate、量化、池化操作后将数据缓存到输出缓存中。整体延时=linebuffer_delay+multiplier_delay+2

×

addertree_delay+accumulate_delay+quantization_delay+pooling_delay。

[0114]

综上所述,相较于现有技术,本发明具有以下突出的优点:

[0115]

本发明根据提出的基于cnn的可配置目标检测硬件加速优化方法完成了目标检测

硬件加速器ip设计。首先对cnn目标检测网络模型进行量化并得到量化参数,然后通过数据接收部分来读取量化后的输入特征图、权重、偏置和激活值,并将其存储到相应的buffer上;紧接着对buffer数据结合卷积计算特点和dsp计算特性进行了可配置设计,并使其适应硬件计算方式,进一步通过基于符号位扩展的双乘法器封装技术来加速卷积计算过程,并实现了cnn硬件量化模块来维持int8计算过程;整个过程在控制模块控制下进行前向推理,最后进行了细粒度流水线方案设计。该设计能够加速在嵌入式领域边端设备目标检测前向推理时间,能够达到峰值144gop/s的峰值性能,实际性能也有77.5gop/s,功耗666mw,该设计ip能效比能达到116.41gop/j,具有一定加速效果。dsp计算效率达到了0.269gop/s/dsp,效果良好。

[0116]

在一些可选择的实施例中,在方框图中提到的功能/操作可以不按照操作示图提到的顺序发生。例如,取决于所涉及的功能/操作,连续示出的两个方框实际上可以被大体上同时地执行或所述方框有时能以相反顺序被执行。此外,在本发明的流程图中所呈现和描述的实施例以示例的方式被提供,目的在于提供对技术更全面的理解。所公开的方法不限于本文所呈现的操作和逻辑流程。可选择的实施例是可预期的,其中各种操作的顺序被改变以及其中被描述为较大操作的一部分的子操作被独立地执行。

[0117]

此外,虽然在功能性模块的背景下描述了本发明,但应当理解的是,除非另有相反说明,所述的功能和/或特征中的一个或多个可以被集成在单个物理装置和/或软件模块中,或者一个或多个功能和/或特征可以在单独的物理装置或软件模块中被实现。还可以理解的是,有关每个模块的实际实现的详细讨论对于理解本发明是不必要的。更确切地说,考虑到在本文中公开的装置中各种功能模块的属性、功能和内部关系的情况下,在工程师的常规技术内将会了解该模块的实际实现。因此,本领域技术人员运用普通技术就能够在无需过度试验的情况下实现在权利要求书中所阐明的本发明。还可以理解的是,所公开的特定概念仅仅是说明性的,并不意在限制本发明的范围,本发明的范围由所附权利要求书及其等同方案的全部范围来决定。

[0118]

所述功能如果以软件功能单元的形式实现并作为独立的产品销售或使用时,可以存储在一个计算机可读取存储介质中。基于这样的理解,本发明的技术方案本质上或者说对现有技术做出贡献的部分或者该技术方案的部分可以以软件产品的形式体现出来,该计算机软件产品存储在一个存储介质中,包括若干指令用以使得一台计算机设备(可以是个人计算机,服务器,或者网络设备等)执行本发明各个实施例所述方法的全部或部分步骤。而前述的存储介质包括:u盘、移动硬盘、只读存储器(rom,read-only memory)、随机存取存储器(ram,random access memory)、磁碟或者光盘等各种可以存储程序代码的介质。

[0119]

在流程图中表示或在此以其他方式描述的逻辑和/或步骤,例如,可以被认为是用于实现逻辑功能的可执行指令的定序列表,可以具体实现在任何计算机可读介质中,以供指令执行系统、装置或设备(如基于计算机的系统、包括处理器的系统或其他可以从指令执行系统、装置或设备取指令并执行指令的系统)使用,或结合这些指令执行系统、装置或设备而使用。就本说明书而言,“计算机可读介质”可以是任何可以包含、存储、通信、传播或传输程序以供指令执行系统、装置或设备或结合这些指令执行系统、装置或设备而使用的装置。

[0120]

计算机可读介质的更具体的示例(非穷尽性列表)包括以下:具有一个或多个布线

的电连接部(电子装置),便携式计算机盘盒(磁装置),随机存取存储器(ram),只读存储器(rom),可擦除可编辑只读存储器(eprom或闪速存储器),光纤装置,以及便携式光盘只读存储器(cdrom)。另外,计算机可读介质甚至可以是可在其上打印所述程序的纸或其他合适的介质,因为可以例如通过对纸或其他介质进行光学扫描,接着进行编辑、解译或必要时以其他合适方式进行处理来以电子方式获得所述程序,然后将其存储在计算机存储器中。

[0121]

应当理解,本发明的各部分可以用硬件、软件、固件或它们的组合来实现。在上述实施方式中,多个步骤或方法可以用存储在存储器中且由合适的指令执行系统执行的软件或固件来实现。例如,如果用硬件来实现,和在另一实施方式中一样,可用本领域公知的下列技术中的任一项或他们的组合来实现:具有用于对数据信号实现逻辑功能的逻辑门电路的离散逻辑电路,具有合适的组合逻辑门电路的专用集成电路,可编程门阵列(pga),现场可编程门阵列(fpga)等。

[0122]

在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不一定指的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施例或示例中以合适的方式结合。

[0123]

尽管已经示出和描述了本发明的实施例,本领域的普通技术人员可以理解:在不脱离本发明的原理和宗旨的情况下可以对这些实施例进行多种变化、修改、替换和变型,本发明的范围由权利要求及其等同物限定。

[0124]

以上是对本发明的较佳实施进行了具体说明,但本发明并不限于所述实施例,熟悉本领域的技术人员在不违背本发明精神的前提下还可做出种种的等同变形或替换,这些等同的变形或替换均包含在本技术权利要求所限定的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1