一种神经网络加速系统、其测试装置和电子设备

本技术涉及机器学习及人工智能领域,尤其涉及一种神经网络加速系统、其测试装置和电子设备。

背景技术:

1、随着消费电子、汽车电子、工业控制等越来越多行业的应用引入人工智能(ai),人工智能面临着前所未有的快速发展,深度学习及神经网络迎来了发展高潮。神经网络越大,需要的计算量就越大,传统的软件实现方案虽然可以完成人工智能运算,但往往是存在高功耗和高延迟的问题。而卷积神经网络(convolutional neutral network,cnn)是一种源自人工神经网络的深度机器学习算法,其对图像的平移、比例缩放、倾斜等形式的变形具有高度的适应性,是提取图形特征灵敏的传感器,其权值共享网络结构使之更类似于生物神经网络结构,降低了网络模型的复杂度,减少了权值的数量。

2、卷积神经网络目前主要基于通用处理器,通过软件方式实现,事实上,卷积神经网络作为一种前馈网络结构,层与层之间具有高度的独立性。其中,各层网络计算独立,层间无数据反馈,因此,卷积神经网络是一种高度并行的网络结构。

3、但是通用处理器为执行逻辑处理和事务处理而优化的特性并不适合用来挖掘卷积神经网络的并行性,基于软件方式的卷积神经网络在实时性和功耗方面都不能满足应用的需求。通常的神经网络加速芯片采用计算单元(pe)阵列设计,控制逻辑复杂、功耗高、应用场景复杂,并且需要大量的内存数据搬运操作,此类设计不适用于低功耗物联网终端设备,因此亟需一种卷积神经网络加速集成方法实现在低功耗物联网终端设备中的应用。

技术实现思路

1、本技术的目的在于提供一种神经网络加速系统、其测试装置和电子设备,以解决神经网络加速芯片采用pe阵列设计,控制逻辑复杂、功耗高、应用场景复杂,并且需要大量的内存数据搬运操作,此类设计不适用于低功耗物联网终端设备的问题

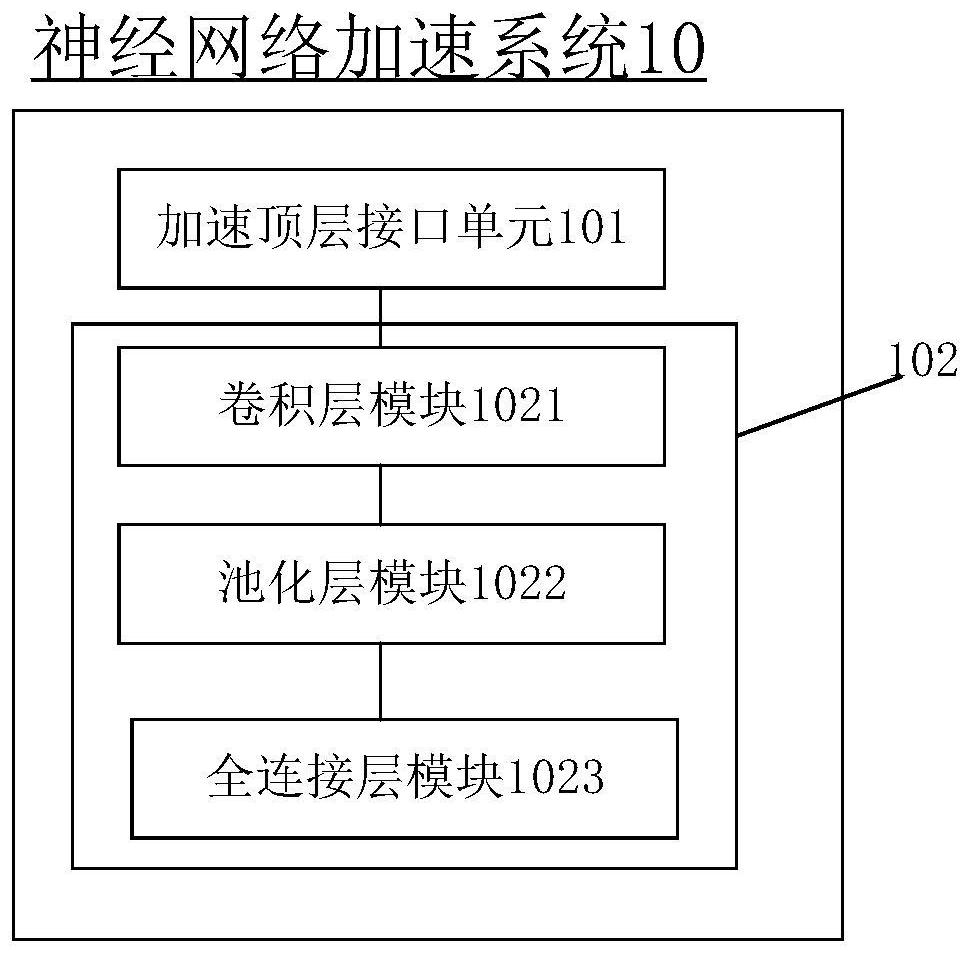

2、第一方面,本技术提供一种神经网络加速系统,所述系统包括加速顶层接口单元和神经网络单元;

3、所述神经网络单元包括依次连接的卷积层模块、池化层模块和全连接层模块;其中,所述卷积层模块、所述池化层模块和所述全连接层模块以数据流级全并行流水线运行方式进行运行;

4、所述加速顶层接口单元用于完成所述卷积层模块、所述池化层模块和所述全连接层模块之间的层间连接。

5、采用上述技术方案的情况下,本技术提供的神经网络加速系统,所述系统包括加速顶层接口单元和神经网络单元;所述神经网络单元包括依次连接的卷积层模块、池化层模块和全连接层模块;其中,所述卷积层模块、所述池化层模块和所述全连接层模块以数据流级全并行流水线运行方式进行运行;所述加速顶层接口单元用于完成所述卷积层模块、所述池化层模块和所述全连接层模块之间的层间连接,可以充分挖掘卷积神经网络固有的并行性,使得可以满足物联网终端推理人工神经网络设备的低功耗低成本,以及满足推理实时性的行业应用需求。

6、在一种可能的实现方式中,所述卷积层模块包括依次连接的卷积层接口设计子模块、卷积层片上存储子模块、输入加载状态机设计子模块、输入缓冲区构建子模块和乘加缓冲区构建子模块;

7、所述卷积层接口设计子模块,用于通过参数化控制卷积层输入数据对应的参数输入,以增加所述卷积层模块的复用性;

8、所述卷积层片上存储子模块,用于按照预设位宽和预设个数分组数存储所述卷积层输入数据中的权重位宽;

9、所述输入加载状态机设计子模块,用于按照预设状态对应关系确定先进先出队列缓冲区状态;

10、所述输入缓冲区构建子模块,用于获取所述先进先出缓冲区状态对应的输入数据,按照预设压入卷积核位置将所述输入数据压入对应的卷积核位置;

11、所述乘加缓冲区构建子模块,用于在所述输入数据压入缓冲区第一列后第一列乘法操作开始进行,当对应的一个卷积核压满后,进行加法操作,得到加法结果,将卷积后的所述加法结果发送至所述池化层模块;

12、其中,所述卷积层输入数据包括输入输出通道数、权重位宽、特征图尺寸、卷积步长和输出数据宽度。

13、在一种可能的实现方式中,所述池化层模块包括依次连接的池化层接口设计子模块、池化层片上存储子模块、比较器设计子模块、上层特征图缓冲区构建子模块和数据位截断子模块;

14、其中,所述池化层接口设计子模块,用于将所述卷积层模块输入的加法结果的前两行加入所述上层特征图缓冲区构建子模块,对所述加法结果进行数据处理,通过所述数据阶段子模块对数据处理后的所述加法结构进行处理,得到输出结果,利用所述比较器设计子模块确定每四个选中块中对应的输出结果的最大值,确定池化层输出结果,将所述池化层输出结果输入至所述全连接层模块。

15、在一种可能的实现方式中,所述全连接层模块用于对池化层模块输入的池化层输出结果进行数据加载,得到全连接层输入数据,对所述全连接层输入数据进行全连接矩阵乘处理,经过三层全连接处理后最后一层确定输出概率值。

16、在一种可能的实现方式中,所述层间连接包括输入数据接口控制、输出数据接口控制和层间连接控制。

17、第二方面,本技术还提供一种神经网络加速系统测试装置,应用于包括第一方面任一所述的神经网络加速系统,还包括所述神经网络加速系统连接的主控模块;

18、所述主控模块被配置为获取待处理图像数据;

19、所述主控模块还被配置为基于所述待处理图像数据确定卷积层输入数据;

20、所述神经网络加速系统被配置为对所述卷积层输入数据进行并行流水线处理,确定输出概率值。

21、在一种可能的实现方式中,所述主控模块包括依次连接的内核控制子模块、设备总线、存储单元和外设互联网协议地址子模块;其中,所述内核控制子模块用于控制数据交互;所述神经网络加速系统挂载在所述设备总线上,用于通过内核控制子模块的控制完成对所述卷积层输入数据进行并行流水线处理,确定所述输出概率值。

22、在一种可能的实现方式中,所述外设互联网协议地址子模块包括图像采集模块、图像显示模块和加速识别结果显示模块;

23、其中,所述图像采集模块被配置为获取所述存储单元中的待处理图像对应的所述待处理图像数据,将所述待处理图像数据转换为二值图像数据;所述主控模块被配置为对所述二值图像数据进行中值滤波处理,对待处理视频流数据进行水平与垂直投影得到数字的定位数据,将数字的所述定位数据确定为所述卷积层输入数据;

24、所述图像显示模块被配置为显示所述待处理图像数据对应的图像;

25、所述加速识别结果显示模块,被配置为显示所述神经网络加速系统输出的概率值对应的识别结果。

26、第二方面提供的神经网络加速系统的有益效果与第一方面或第一方面任一可能的实现方式描述的神经网络加速系统的有益效果相同,此处不做赘述。

27、第三方面,本技术还提供一种电子设备,包括:一个或多个处理器;和其上存储有指令的一个或多个机器可读介质,当由所述一个或多个处理器执行时,使得所述装置执行第一方面任一可能的实现方式描述的神经网络加速系统。

28、第三方面提供的电子设备的有益效果与第一方面或第一方面任一可能的实现方式描述的神经网络加速系统的有益效果相同,此处不做赘述。

- 还没有人留言评论。精彩留言会获得点赞!