一种工程修改的装置和方法与流程

本技术涉及芯片设计领域,并且更具体地,涉及一种工程修改的装置和方法。

背景技术:

1、在芯片设计的过程中,设计工程师为了能够对最终生产出来的实体芯片进行测试筛片,需要在设计好的电气门级综合(synphysize,syn)网表中插入可测试性(design fortest,dft)电路,得到dft网表,基于dft网表进行布局布线操作,得到布局布线(place androute,pr)网表。但是,在芯片设计后期,若发现原有电路设计存在错误或者需要增加新的功能时,需要直接对上述pr网表进行修改,即进行工程修改。现阶段完成工程修改的方式是通过人工编写脚本,将新增的寄存器插入原有网表的扫描链。但是在网表规模较大的情况下,通过人工编写脚本新增寄存器的方式工作量巨大,效率低,脚本通用性差,并且难以实现。

2、因此,如何解决当前工程修改方式的修改效率低,通用性差的问题是现阶段亟需解决的技术问题。

技术实现思路

1、本技术实施例提供一种工程修改的装置和方法,以解决当前工程修改方式的修改效率低,通用性差的问题。

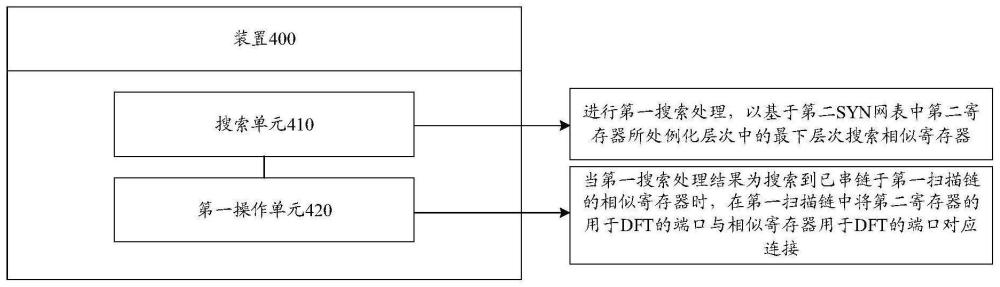

2、第一方面,提供了一种工程修改的装置,该装置包括:搜索单元和第一操作单元。

3、搜索单元进行第一搜索处理,以基于第二syn网表中第二寄存器所处例化层次中的最下层次搜索相似寄存器,其中,第二寄存器是需要新增到第一扫描链中的寄存器,第一扫描链是插入在第一syn网表的可测性设计dft电路包括的扫描链,第二syn网表是修改后的第一syn网表,相似寄存器是与第二寄存器功能逻辑一致的寄存器;当第一搜索处理结果为搜索到已串链于第一扫描链的相似寄存器时,第一操作单元在第一扫描链中将第二寄存器的用于dft的端口与相似寄存器用于dft的端口对应连接。

4、应理解,之所以要在第一扫描链中新增第二寄存器,是因为第一扫描链所在的第一pr网表存在一些错误或者需要新增一些功能。其中,第一pr网表可以是工程修改前的原pr网表,而第一pr网表可以是基于第一dft网表经过布局布线得到的网表;第一dft网表可以是工程修改前的原dft网表,而第一dft网表则是在第一syn网表插入dft电路后得到的网表;而第一syn网表则是基于原寄存器传输级(register transfer level,rtl)代码进行综合处理后得到的网表。

5、示例地,上述第二寄存器的例化层次可以通过第二寄存器的例化层次名来表示。例化层次名由字母和数字构成,由于例化层次名是按照指定的命名规则命名的,两个例化层次名相近的寄存器。

6、示例地,上述第二寄存器的例化层次名可以为如下形式:

7、a1.1.1.1;a1.1.1.2;a1.1.2.1;a1.1.2.2;a1.2.1.1;a1.2.1.2;以此类推。其中的字母以及数字组合能够代表着指定寄存器在dft电路中的具体物理位置,或者可以理解为寄存器所处dft电路中的具体层级中的位置,或者还可以理解为能够在dft电路中追踪到指定寄存器的具体路径。当然,为了区分同一层次名下的不同寄存器,还可以在例化层次名后携带能够唯一标识寄存器的寄存器id,例如:a1.1.1.1-寄存器id(001)、a1.1.2.1-寄存器id(002)等,而对于这两个寄存器例化层次,仅区别于倒数第二层,因此,这两个寄存器的物理位置也应当是相近的。进一步地,数字电路中还包括一个寄存器:a1.1.1.2-寄存器id(003),相较于寄存器002,寄存器003与寄存器001的例化层次仅区别于最后一层,那么由此可知,寄存器003与寄存器001之间的物理位置更为接近。

8、应理解,上述例化层次名仅为一种示例性说明,例化层次名还可以通过其他的命名规则进行命名,但是,其命名规则都需要满足以下条件,即两个物理位置相近的寄存器,它们的例化层次名必然是相似的,反之亦然。

9、示例地,上述第一操作单元或者上述搜索单元可以通过如下方式确定相似寄存器已串链与第一扫描链上:首先判断该相似寄存器是否存在于第一pr网表中的;然后判断该相似寄存器是否已在扫描链上;当这两个判断条件均为“是”,则能够认为该相似寄存器已串链与第一扫描链上。

10、基于上述技术方案,无需通过人工编写代码脚本,即可实现向扫描链插入第二寄存器,并且为第二寄存器选取功能逻辑一致的dft可控信号点,对原有电路的时序冲击较小。并且该方法通用性强,效率高,并且适用于新增寄存器数量巨大的场景,还适用于对不同设计模板下的芯片进行工程修改。

11、结合第一方面,在第一方面的某些实现方式中,上述搜索单元基于第二syn网表中第二寄存器所处例化层次中的最下层次筛选出候选寄存器;在第二syn网表中,在候选寄存器满足以下至少一个条件时,搜索单元确定候选寄存器为相似寄存器:

12、候选寄存器与新增寄存器之间直连,或者,

13、候选寄存器与新增寄存器之间设置有缓冲器,或者,

14、候选寄存器与新增寄存器之间设置有成对的反相器。

15、基于上述技术方案,能够保证搜索到的相似寄存器与第二寄存器功能逻辑一致,以保证新增到第一扫描链的第二寄存器仍然满足dft可控。

16、结合第一方面,在第一方面的某些实现方式中,上述装置还包括第一处理单元,在搜索单元在第二syn网表中搜索到多个相似寄存器时,该第一处理单元将所述多个相似寄存器的例化层次名分别与上述第二寄存器的例化层次名进行匹配,该例化层次名由字母和数字构成;上述第一操作单元将上述第二寄存器的用于dft的端口与已串链于所述第一扫描链的且匹配度最高的相似寄存器的用于dft的端口对应连接。

17、示例地,上述第一处理单元还可以将多个相似寄存器的例化层次名分别与第二寄存器的例化层次名进行匹配,对多个相似寄存器按照匹配度高低进行降序排序;上述第一操作单元从而依次确认排序后的相似寄存器是否已串链于第一扫描链,将第二寄存器的用于dft的端口与第一个被确认为已串链与第一扫描链的相似寄存器的用于dft的端口对应连接。

18、示例地,上述第一处理单元还可以将相似寄存器和第二寄存器的例化层次名按照文本排序,若相似寄存器在队列中越邻近第二寄存器,则二者的匹配度越高。应理解,匹配度越高,相似寄存器与第二寄存器在控制逻辑上越趋于一致,越能够保障插入第二寄存器后的数字电路可测性,即保障第二寄存器的用于dft的端口插入后仍能被原dft电路控制。

19、基于上述技术方案,能够在多个相似寄存器中挑选出最为合适的用于与第二寄存器相连的相似寄存器,保障了第二寄存器用于dft的端口能够被原电路的逻辑功能信号源可控,并且对原电路的改动较小,也不影响原电路的原有功能逻辑。

20、结合第一方面,在第一方面的某些实现方式中,当上述第一搜索处理结果为未搜索到已串链于第一扫描链的相似寄存器时,上述搜索单元扩大第一搜索处理的搜索范围,继续搜索相似寄存器,直到搜索到已串链于第一扫描链的相似寄存器。

21、基于上述技术方案,保障第二寄存器能够查找到dft可控点,以保障第二寄存器能够插入到第一扫描链中,并实现该第二寄存器的逻辑功能端口在数字电路中dft可控。

22、结合第一方面,在第一方面的某些实现方式中,上述搜索单元基于第二syn网表中第二寄存器所处例化层次中的最下层次的上一层次,搜索相似寄存器。

23、示例地,上述第二寄存器所处例化层次中的最下层次的上一层次可以认为是第二寄存器所处例化层次中的倒数第二层次。但是,如在上述操作中,还没有搜索到已串链于第一扫描链的相似寄存器,则还可以基于第二syn网表中第二寄存器所处例化层次中的倒数第三层次,继续搜索相似寄存器,以此类推。

24、基于上述技术方案,通过逐层扩大搜索范围的方式,尽可能精细地搜索与第二寄存器最匹配的相似寄存器,从而保障第二寄存器能够查找到dft可控点,以保障第二寄存器能够插入到第一扫描链中,并实现该第二寄存器的逻辑功能端口在数字电路中dft可控,并尽可能的减小对原电路的冲击。

25、结合第一方面,在第一方面的某些实现方式中,上述用于dft的端口包括:时钟clk端口、扫描使能se端口、复位rst端口。

26、结合第一方面,在第一方面的某些实现方式中,上述装置还包括:第二处理单元和第二操作单元;

27、在上述搜索单元确定第二寄存器的例化层次之前,上述第二处理单元确定至少一个第二寄存器;上述第二处理单元根据第二寄存器所属的clk源信息,对至少一个第二寄存器进行分组,并根据第二寄存器的例化层次,分别对同组的第二寄存器进行排序;上述第二操作单元将经过分组和排序后的第二寄存器依次插入第一扫描链中。

28、示例地,上述clk源信息可以是clk源的标识信息,例如clk1、clk2等,第二寄存器所属的clk源信息表示该第二寄存器的clk控制信号端口用于接收哪种clk源发出的信号。因此,上述对至少一个第二寄存器进行分组的过程可以是将上述至少一个第二寄存器划分为至少一组第二寄存器,每一组中的第二寄存器的clk源信息都相同,例如,都是clk1或者clk2等。

29、基于上述技术方案,在每一组寄存器数量都比较多的情况下,可以基本保证插入第一扫描链的相邻两个第二寄存器具有相同clk源,基本不会出现多对相邻两个第二寄存器所具有的clk源不同的情况,从而能够避免造成插入第二寄存器后电路整体布局布线混乱的问题。

30、结合第一方面,在第一方面的某些实现方式中,上述第二处理单元根据同组的第二寄存器的例化层次名,对同组的第二寄存器进行文本排序,例化层次名由字母和数字构成,文本排序是基于字母表顺序和数字递增或递减顺序进行排序的方式。

31、基于上述技术方案,通过对同组的第二寄存器进行文本排序,使整个第二寄存器队列,保障相邻的两个第二寄存器在物理位置上尽可能相近,这样将排序后的第二寄存器插入第一扫描链,可以有效避免因插入第二寄存器造成的原电路布局布线混乱的情况。

32、结合第一方面,在第一方面的某些实现方式中,上述第二操作单元确定至少一条第一扫描链,并确定每条第一扫描链的第三数量,第三数量为第一扫描链可插入寄存器的数量;上述第二操作单元将经过分组和排序后的第二寄存器最先依次插入当前第三数量最大的第一扫描链中。

33、示例地,在确定上述至少一个第一扫描链的第三数量后,可以根据第三数量,对至少一个第一扫描链进行降序排序,排在首位的则是第三数量最大的第一扫描链,排在次位的则是第三数量第二大的第一扫描链,以此类推。基于此,上述经过分组和排序后的第二寄存器可以按照上述第一扫描链的顺序依次插入到指定的第一扫描链中。

34、示例地,还可以将经过分组和排序后的第二寄存器存储到待串链寄存器列表中,然后按照上述排序方式得到的第一扫描链顺序,依次确定每个第一扫描链的第三数量,然后依次从待串链寄存器列表中截取第三数量的第二寄存器,插入到对应第一扫描链中,直至待串链寄存器列表中的第二寄存器数量为0。

35、基于上述技术方案,可以基本保证插入第一扫描链的相邻两个第二寄存器具有相同clk源,基本不会出现多对相邻两个第二寄存器所具有的clk源不同的情况,从而能够避免造成插入第二寄存器后电路整体布局布线混乱的问题。

36、结合第一方面,在第一方面的某些实现方式中,上述第二操作单元确定每条第一扫描链的第一数量,第一数量为第一扫描链包括的第一寄存器的数量,第一寄存器为第一扫描链中原有的寄存器;上述第二操作单元确定至少一条第一扫描链中最大的第一数量为第二数量;上述第二操作单元根据第二数量与第一数量之差,确定第三数量。

37、结合第一方面,在第一方面的某些实现方式中,上述第二操作单元确定每条第一扫描链的第一数量,第一数量为第一扫描链包括的第一寄存器的数量;上述第二操作单元确定第四数量,第四数量为用户声明的最大扫描链长度;上述第二操作单元根据第四数量与第一数量之差,确定第三数量。

38、示例地,当用户没有预先声明最大扫描链长度,那么可以将上述第一扫描链的第一数量中的最大值当做上述用户声明的最大扫描链长度,例如,第一扫描链的第一数量分别为:100、120、150、180,那么能够确定第二数量为180,然后通过第二数量分别与上述第一数量进行作差操作,分别得出以下第三数量:80、60、30、0。那么,在插入第二寄存器时,首先向第三数量为80的第一扫描链中插入,当这80个的闲余可插链空间已经被插满后,则剩余的第二寄存器需要向第三数量为60的第一扫描链中插入,以此类推。由此可知,第三数量最大的第一扫描链,是在所有第一扫描链中链长最短的扫描链,而第三数量最小的第一扫描链,是在所有第一扫描链中链长最长的扫描链,并且该第一扫描链对应的第三数量为0。

39、结合第一方面,在第一方面的某些实现方式中,第二操作单元从第一扫描链的链尾处依次插入经过分组和排序后的第二寄存器。

40、基于上述技术方案,在第一扫描链的链尾插入第二寄存器,能够有效避免第二寄存器影响第一扫描链原有的测试功能逻辑。

41、第二方面,提供了一种工程修改的方法,该方法包括:进行第一搜索处理,以基于第二综合syn网表中第二寄存器所处例化层次中的最下层次搜索相似寄存器,其中,第二寄存器是需要新增到第一扫描链中的寄存器,第一扫描链是插入在第一syn网表的可测性设计dft电路包括的扫描链,第二syn网表是修改后的第一syn网表,相似寄存器是与第二寄存器功能逻辑一致的寄存器;当第一搜索处理结果为搜索到已串链于第一扫描链的相似寄存器时,在第一扫描链中将第二寄存器的用于dft的端口与相似寄存器用于dft的端口对应连接。

42、基于上述技术方案,能够实现向扫描链插入第二寄存器,并且为第二寄存器选取功能逻辑一致的dft可控信号点,对原有电路的时序冲击较小。并且该方法通用性强,效率高,并且适用于新增寄存器数量巨大的场景,还适用于对不同设计模板下的芯片进行工程修改。

43、结合第二方面,在第二方面的某些实现方式中,基于第二综合syn网表中第二寄存器所处例化层次中的最下层次筛选出候选寄存器;在第二syn网表中,在候选寄存器满足以下至少一个条件时,确定候选寄存器为相似寄存器:

44、候选寄存器与新增寄存器之间直连,或者

45、候选寄存器与新增寄存器之间设置有缓冲器,或者,

46、候选寄存器与新增寄存器之间设置有成对的反相器。

47、基于上述技术方案,能够保证搜索到的相似寄存器与第二寄存器功能逻辑一致,以保证新增到第一扫描链的第二寄存器仍然满足dft可控。

48、结合第二方面,在第二方面的某些实现方式中,在第二syn网表中搜索到多个相似寄存器时,将所述多个相似寄存器的例化层次名分别与上述第二寄存器的例化层次名进行匹配,该例化层次名由字母和数字构成;将上述第二寄存器的用于dft的端口与已串链于所述第一扫描链的且匹配度最高的相似寄存器的用于dft的端口对应连接。

49、示例地,还可以将多个相似寄存器的例化层次名分别与第二寄存器的例化层次名进行匹配,对多个相似寄存器按照匹配度高低进行降序排序;进而依次确认排序后的相似寄存器是否已串链于第一扫描链,将第二寄存器的用于dft的端口与第一个被确认为已串链与第一扫描链的相似寄存器的用于dft的端口对应连接。

50、基于上述技术方案,能够在多个相似寄存器中挑选出最为合适的用于与第二寄存器相连的相似寄存器,保障了第二寄存器用于dft的端口能够被原电路的逻辑功能信号源可控,并且对原电路的改动较小,也不影响原电路的原有功能逻辑。

51、结合第二方面,在第二方面的某些实现方式中,当第一搜索处理结果为未搜索到已串链于第一扫描链的相似寄存器时,扩大第一搜索处理的搜索范围,继续搜索相似寄存器,直到搜索到已串链于第一扫描链的相似寄存器。

52、基于上述技术方案,保障第二寄存器能够查找到dft可控点,以保障第二寄存器能够插入到第一扫描链中,并实现该第二寄存器的逻辑功能端口在数字电路中dft可控。

53、结合第二方面,在第二方面的某些实现方式中,基于第二syn网表中第二寄存器所处例化层次中的最下层次的上一层次,搜索相似寄存器。

54、基于上述技术方案,通过逐层次扩大搜索范围的方式,尽可能精细地搜索与第二寄存器最匹配的相似寄存器,从而保障第二寄存器能够查找到dft可控点,以保障第二寄存器能够插入到第一扫描链中,并实现该第二寄存器的逻辑功能端口在数字电路中dft可控,并尽可能的减小对原电路的冲击。

55、结合第二方面,在第二方面的某些实现方式中,上述用于dft的端口包括:时钟clk端口、扫描使能se端口、复位rst端口

56、结合第二方面,在第二方面的某些实现方式中,在上述确定第二寄存器的例化层次之前,确定至少一个第二寄存器;根据第二寄存器所属的clk源信息,对至少一个第二寄存器进行分组,并根据第二寄存器的例化层次,分别对同组的第二寄存器进行排序;将经过分组和排序后的第二寄存器依次插入第一扫描链中。

57、基于上述技术方案,在每一组寄存器数量都比较多的情况下,可以基本保证插入第一扫描链的相邻两个第二寄存器具有相同clk源,基本不会出现多对相邻两个第二寄存器所具有的clk源不同的情况,从而能够避免造成插入第二寄存器后电路整体布局布线混乱的问题。

58、结合第二方面,在第二方面的某些实现方式中,根据同组的第二寄存器的例化层次名,对同组的第二寄存器进行文本排序,例化层次名由字母和数字构成,该文本排序是基于字母表顺序和数字递增或递减顺序进行排序的方式。

59、基于上述技术方案,通过对同组的第二寄存器进行文本排序,使整个第二寄存器队列,保障相邻的两个第二寄存器在物理位置上尽可能相近,这样将排序后的第二寄存器插入第一扫描链,可以有效避免因插入第二寄存器造成的原电路布局布线混乱的情况。

60、结合第二方面,在第二方面的某些实现方式中,确定至少一条第一扫描链,并确定每条第一扫描链的第三数量,该第三数量为第一扫描链可插入寄存器的数量;将经过分组和排序后的第二寄存器最先依次插入当前第三数量最大的第一扫描链中。

61、基于上述技术方案,可以基本保证插入第一扫描链的相邻两个第二寄存器具有相同clk源,基本不会出现多对相邻两个第二寄存器所具有的clk源不同的情况,从而能够避免造成插入第二寄存器后电路整体布局布线混乱的问题。

62、结合第二方面,在第二方面的某些实现方式中,确定每条第一扫描链的第一数量,第一数量为第一扫描链包括的第一寄存器的数量,第一寄存器为第一扫描链中原有的寄存器;确定至少一条第一扫描链中最大的第一数量为第二数量;根据第二数量与第一数量之差,确定第三数量。

63、结合第二方面,在第二方面的某些实现方式中,确定每条第一扫描链的第一数量,第一数量为第一扫描链包括的第一寄存器的数量;确定第四数量,第四数量为用户声明的最大扫描链长度;根据第四数量与第一数量之差,确定第三数量。

64、结合第二方面,在第二方面的某些实现方式中,从第一扫描链的链尾处依次插入经过分组和排序后的第二寄存器。

65、基于上述技术方案,在第一扫描链的链尾插入第二寄存器,能够有效避免第二寄存器影响第一扫描链原有的测试功能逻辑。

66、第三方面,提供了一种工程修改的装置,包括存储器,用于存储计算机指令;还包括处理器,用于执行存储器中存储的计算机指令,以使得装置执行上述第二方面的方法设计中任意一种可能的实现方式中的方法。

67、第四方面,提供了一种计算机存储介质,计算机存储介质中存储有计算机指令,该指令在计算机上执行时,使得计算机执行上述第二方面的方法设计中任意一种可能的实现方式中的方法。

68、第五方面,提供了一种芯片,包括处理器,该处理器用于执行上述第二方面的方法设计中任意一种可能的实现方式中的方法。

69、第六方面,提供了一种计算机程序产品,该计算机程序代码或指令在计算机上执行时,使得计算机执行上述第二方面的方法设计中任意一种可能的实现方式中的方法。

- 还没有人留言评论。精彩留言会获得点赞!