存储器系统及存储器系统的控制方法与流程

存储器系统及存储器系统的控制方法

1.分案申请的相关信息

2.本案是分案申请。该分案的母案是申请日为2018年8月6日、申请号为201810885153.7、发明名称为“存储器系统”的发明专利申请案。

3.[相关申请案]

[0004]

本技术案享有以日本专利申请案2017-180351号(申请日:2017年9月20日)为基础申请案的优先权。本技术案通过参照该基础申请案而包含基础申请案的所有内容。

技术领域

[0005]

本实施方式涉及一种存储器系统。

背景技术:

[0006]

以往,作为用于计算机系统的外部存储装置,搭载有非易失性存储器的存储器系统受到关注。存储器系统是由存储器控制器及连接于控制器的存储器构成,与外部装置的通信是通过串列接口进行,与存储器的通信是通过存储器接口进行。通常,存储器的通信速度慢,因此通过将存储器并联连接,而谋求大容量化与宽频带化。然而,因并联连接而配线负荷增大,因此利用并联化所实现的宽频带化存在极限。进而,伴随着近年来的串列接口的宽频带化,要求更进一步的存储器的大容量、宽频带化。

技术实现要素:

[0007]

一实施方式提供一种解决串列接口与存储器接口的数据传送速度不匹配,且大容量、宽频带的存储器系统。

[0008]

根据一实施方式,存储器系统具备第1及第2存储器、存储器控制器及桥接电路。存储器控制器发送第1数据,该第1数据是应分别写入给第1及第2存储器的数据,并且是在振幅方向及时间方向中的任一方向以上分配给对应的各存储器的区域中包含各存储器的特定比特数据。桥接电路从自存储器控制器发送的第1数据中分配给第1存储器的区域,取出特定比特数据,控制特定比特数据向第1存储器的写入,并将从第1数据去除所取出的特定比特数据后的第2数据,发送给控制向所述第2存储器的数据写入的第2桥接电路。

附图说明

[0009]

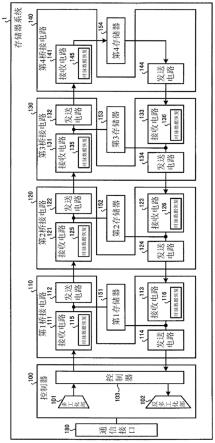

图1是表示第1实施方式的存储器系统的构成例的图。

[0010]

图2是例示通过第1实施方式的多工化部而汇总的写入符号的图。

[0011]

图3是例示第1实施方式的nand(not and,与非)控制器所接收的读取符号的图。

[0012]

图4是例示在第1实施方式的存储器系统内发送的写入符号的转变的图。

[0013]

图5是例示在第1实施方式的存储器系统内传送的读取符号的转变的图。

[0014]

图6是例示第1实施方式的变化例1中的读取符号与时脉的嵌埋时点的关系的图。

[0015]

图7是例示通过第1实施方式的变化例1中的第4桥接电路的发送电路所发送的储

存有第4存储器的读取数据的读取符号的图。

[0016]

图8是例示通过第1实施方式的变化例1中的第3桥接电路的发送电路所发送的储存有第3存储器及第4存储器的读取数据的读取符号的图。

[0017]

图9是例示第1实施方式的变化例1中的写入符号与嵌埋时点的关系的图。

[0018]

图10是例示第1实施方式的变化例2中针对各cdr(clock data recovery,时脉数据恢复)进行相位追随功能的频带的图。

[0019]

图11是表示第2实施方式的存储器系统的构成例的图。

[0020]

图12是表示第2实施方式的第1桥接电路~第4桥接电路的构成例的图。

[0021]

图13是例示在第2实施方式的存储器系统内发送的符号的转变的图。

[0022]

图14是例示变化例的发送侧的桥接电路及接收侧的桥接电路的构成的图。

[0023]

图15是表示使用以往的方法以信号线发送读取符号及同步信号时的数据宽度的图。

[0024]

图16是表示以变化例的信号线发送的读取符号及同步信号的数据宽度的图。

具体实施方式

[0025]

以下,参照随附图式,对实施方式的存储器系统详细地进行说明。此外,本发明不受这些实施方式限定。

[0026]

(第1实施方式)

[0027]

图1是表示第1实施方式的存储器系统1的构成例的图。存储器系统1与(未图示的)主机之间进行数据收发。主机例如相当于个人计算机、便携式信息终端或服务器等。存储器系统1能够从主机受理存取要求(读取要求及写入要求)。作为存储器系统1,例如考虑有ssd(solid state drive,固态硬盘)、sd存储卡(secure digital memory card,数据安全卡)驱动器等,只要为能够对非易失性存储器进行读写的系统即可。

[0028]

存储器系统1具备通信接口180、存储器控制器100、第1桥接电路110、第2桥接电路120、第3桥接电路130、第4桥接电路140、第1存储器151、第2存储器152、第3存储器153及第4存储器154。

[0029]

通信接口180是用来与主机之间进行数据收发的接口。

[0030]

第1存储器151、第2存储器152、第3存储器153及第4存储器154例如是nand型闪速存储器(nand存储器)的封装。在本实施方式中,第1存储器151、第2存储器152、第3存储器153及第4存储器154并不限定于nand存储器的封装,例如也可以是隔着存储器接口而多个并联连接的存储器群、或积层于封装内的存储器芯片群等由多个存储器构成。在本实施方式中,对使用nand存储器作为非易失性存储器的一例的例子进行说明,但也可以使用任意的非易失性存储器。例如,存储器系统1也可以使用nor(not or,与或)型闪速存储器代替nand存储器。另外,本实施方式中,对封装的数量为4个的情况进行说明,但封装的数量并无限制。

[0031]

存储器控制器100具备多工化部101、反多工化部102及控制器103,进行主机与第1存储器151~第4存储器154之间的数据传送。

[0032]

多工化部(mux)101将发送给第1存储器151~第4存储器154各者的以1bit为单位的通信数据汇总。在本实施方式中,将作为要被写入的数据(以下,称为写入数据)而汇总储

存的单位通信数据称为写入符号。

[0033]

图2是例示由本实施方式的多工化部101所汇总的写入符号的图。在图2所示的例子中,储存第1存储器151用写入数据(1bit)201、第2存储器152用写入数据(1bit)202、第3存储器153用写入数据(1bit)203及第4存储器154用写入数据(1bit)204。也就是说,多工化部101将4bit写入数据汇总为写入符号。

[0034]

图2所示的写入符号在振幅方向上设置2bit数据的储存区域,在时间方向上设置2bit数据的储存区域。然后,在所设置的储存区域中预先分配给设置在本实施方式的存储器系统1的各存储器封装(第1存储器151~第4存储器154)的区域,储存要发送给该存储器封装的1bit数据。

[0035]

关于本实施方式中的对每个存储器封装预先分配区域的方法的一例进行说明。当存储器系统1启动时,存储器控制器100对第1桥接电路110~第4桥接电路140发送唯一识别每个桥接电路的id(identification,标识码)。第1桥接电路110~第4桥接电路140可依照所发送的id而识别预先分配给本桥接电路的区域。由此,当进行数据通信时,可以从启动时预先分配的区域取出存储器用写入数据(1bit)。在本实施方式中,表示了分配方法的一例,也可以在制造、出货时设定预先分配给各存储器的区域。

[0036]

此外,对本实施方式的多工化部101使用以1时槽传送2bit信息的pam(pulse amplitude modulation)4(4相脉冲振幅调变)的例子进行说明,但也可以使用其它方法。在本实施方式中,对在振幅方向及时间方向上设置储存数据的区域的例子进行说明,但也可以在振幅方向及时间方向中的任一方向上设置储存数据的区域。此外,在本实施方式中,对在每个存储器的封装储存1bit数据的例子进行说明,但并不限定于1bit,例如也可以储存2bit数据。

[0037]

以往,当从存储器控制器对多个桥接电路发送数据时,必须追加用来特定出数据的发送目标的桥接电路的地址信息。在此情况下,由于对所发送的信息追加了地址信息,所以数据的发送效率降低,传送速度降低。另外,在发送追加有地址信息的数据的情况下,必须在各桥接电路中进行判别是否为向本电路发送的数据的处理等。因此,在将多个桥接电路串联连接且从前段的桥接电路向后段的桥接电路发送数据的情况下,因各桥接电路的处理所产生的延迟成为问题。另一方面,在为了实现高速化而将追加有地址信息的数据发送给所连接的所有桥接电路的情况下,产生消耗电力增大的问题。

[0038]

与此相对,本实施方式的存储器控制器100是在预先分配给每个桥接电路的区域中,储存要向桥接电路发送的数据。由此,桥接电路通过从预先分配给本桥接电路的区域读入1bit数据,而即便不设置地址信息,也可以接收以本桥接电路为发送目标的数据。

[0039]

另外,本实施方式的多工化部101将用以供各桥接电路(第1桥接电路110~第4桥接电路140)特定出储存有本区块电路的数据的储存区域的同步信号(时脉)与写入符号一起嵌埋到要发送的信号。此外,同步信号的嵌埋方法使用周知的方法即可,省略说明。此外,将同步信号与写入符号一起嵌埋到相同信号的方法并无限制,也可以从与写入符号不同的信号线发送。这样一来,同步信号的发送方法可使用无论是否为周知方法的任何方法。

[0040]

图1的控制器103控制与第1桥接电路110之间的数据传送。例如,控制器103将通过多工化部101而多工化后的写入符号发送给第1桥接电路110。

[0041]

控制器103从第1桥接电路110接收读取符号。在本实施方式中,将从第1存储器151

~第4存储器154读出的1bit读取数据汇总储存所得的单位通信数据被称为读取符号。

[0042]

图3是例示控制器103所接收的读取符号的图。在图3所示的例子中,储存从第1存储器151读出的读取数据(以下,称为第1存储器151的读取数据)(1bit)301、第2存储器152的读取数据(1bit)302、第3存储器153的读取数据(1bit)303及第4存储器154的读取数据(1bit)304。也就是说,控制器103接收将从各存储器(第1存储器151~第4存储器154)读出的1bit单位的读取数据汇总所得的4bit读取符号。

[0043]

图3所示的读取符号在振幅方向上设置2bit数据的储存区域,在时间方向上设置2bit数据的储存区域。然后,在所设置的储存区域中的预先分配给设置在本实施方式的存储器系统1的各存储器封装(第1存储器151~第4存储器154)的区域,储存从该存储器封装读出的1bit单位的数据。

[0044]

返回到图1,反多工化部(demux)102针对所接收到的各读取符号,从预先分配给各存储器封装(第1存储器151~第4存储器154)的区域读出1bit单位的数据,产生各存储器封装(第1存储器151~第4存储器154)的数据。然后,将所产生的数据从通信接口180发送给主机。

[0045]

第1桥接电路110是用来控制对第1存储器151进行数据读出及写入的桥接电路,具备接收电路111、发送电路112、接收电路113及发送电路114。此外,在本实施方式中,关于第1桥接电路110控制对第1存储器151进行数据读出及写入的例子进行说明,但也可以仅控制数据的读出及写入中的任一种。

[0046]

第1桥接电路110从预先分配给第1存储器151的区域,读出从存储器控制器100发送而来的写入符号中的1bit写入数据。

[0047]

接收电路111具备cdr115。cdr115根据从存储器控制器100发送的信号,与和写入符号一起发送来的同步信号(时脉)相位同步。

[0048]

图4是例示在本实施方式的存储器系统1内发送的写入符号的转变的图。如图4所示,存储器控制器100发送储存有第1存储器151用写入数据(1bit)411、第2存储器152用写入数据(1bit)412、第3存储器153用写入数据(1bit)413及第4存储器154用写入数据(1bit)414的写入符号401。

[0049]

然后,接收电路111以同步信号为基准,从预先分配给第1存储器151的区域,读出从存储器控制器100发送而来的(图4所示的)写入符号401中的第1存储器151用写入数据(1bit)411。然后,接收电路111基于所读出的第1存储器151用写入数据411,进行将该数据写入到第1存储器151的控制。

[0050]

然后,接收电路111将写入符号401及同步信号交付给发送电路112。

[0051]

然后,发送电路112以同步信号为基准,从分配为第1存储器151用的区域,去除(抹除)写入符号401中的第1存储器151用写入数据(1bit)411,从而产生写入符号402。如图4所示,写入符号402由第2存储器152用写入数据(1bit)412、第3存储器153用写入数据(1bit)413及第4存储器154用写入数据(1bit)414构成。

[0052]

然后,发送电路112将在写入符号402中包含有从cdr115接收的同步信号所得的信号发送给第2桥接电路120。作为在写入符号402中包含同步信号的方法,可使用任何方法,例如考虑在写入符号402产生信号边缘的时点作为振幅信息包含。写入符号402与写入符号401相比,除去(删除)了写入符号后的振幅方向上的数据量得以减少。由此,本实施方式的

存储器系统1可降低用于振幅方向的电压,因此可实现消耗电力的降低。接下来,对第2桥接电路120进行说明。此外,对于第1桥接电路110的接收电路113及发送电路114将在下文叙述。

[0053]

第2桥接电路120是用来控制对第2存储器152进行数据读出及写入的桥接电路,具备接收电路121、发送电路122、接收电路123及发送电路124。此外,在本实施方式中,关于第2桥接电路120控制对第2存储器152进行数据读出及写入的例子进行说明,也可以仅进行数据的读出及写入中的任一种。

[0054]

接收电路121具备cdr125。cdr125根据从第1桥接电路110发送的信号,与和写入符号402一起发送来的同步信号(时脉)相位同步。

[0055]

然后,接收电路121以同步信号为基准,从自第1桥接电路110发送而来的(图4所示的)写入符号402,读出第2存储器152用写入数据(1bit)412。然后,接收电路121基于所读出的第2存储器152用写入数据412,进行将该数据写入到第2存储器152的控制。

[0056]

发送电路122以同步信号为基准,从分配为第2存储器152用的区域,去除写入符号402中的第2存储器152用写入数据(1bit)412,从而产生写入符号403。如图4所示,写入符号403是由第3存储器153用写入数据(1bit)413、及第4存储器154用写入数据(1bit)414构成。

[0057]

然后,发送电路122将在写入符号403中包含有从cdr125接收的同步信号所得的信号发送给第3桥接电路130。写入符号403与写入符号402相比,时间方向上的数据量得以减少。因此,本实施方式的发送电路122将从写入符号403下采样(downsampling)所得的数据作为写入符号402发送给第3桥接电路130。由此,可实现消耗电力的降低。接下来,对第3桥接电路130进行说明。此外,对于第2桥接电路120的接收电路123及发送电路124将在下文叙述。

[0058]

第3桥接电路130是控制对第3存储器153进行数据读出及写入的桥接电路,具备接收电路131、发送电路132、接收电路133及发送电路134。此外,在本实施方式中,关于第3桥接电路130控制对第3存储器153进行数据读出及写入的例子进行说明,也可以仅进行数据的读出及写入中的任一种。

[0059]

接收电路131具备cdr135。cdr135根据从第2桥接电路120发送而来的信号,与和写入符号403一起发送来的同步信号(时脉)相位同步。

[0060]

然后,接收电路131以同步信号为基准,从自第2桥接电路120发送而来的(图4所示的)写入符号403,读出第3存储器153用写入数据(1bit)413。然后,接收电路131基于所读出的第3存储器153用写入数据413,进行将该数据写入到第3存储器153的控制。

[0061]

然后,发送电路132以同步信号为基准,从分配为第3存储器153用的区域,去除写入符号403中的第3存储器153用写入数据(1bit)413,从而产生写入符号404。如图4所示,写入符号404是由第4存储器154用写入数据(1bit)414构成。

[0062]

然后,发送电路132将在写入符号404中包含有从cdr135接收的同步信号所得的信号发送给第4桥接电路140。写入符号404与写入符号403相比,振幅方向上的数据量得以减少。由此,本实施方式的存储器系统1可降低用于振幅方向的电压,因此可实现消耗电力的降低。接下来,对第4桥接电路140进行说明。此外,对第3桥接电路130的接收电路133及发送电路134将在下文叙述。

[0063]

第4桥接电路140是控制对第4存储器154进行数据读出及写入的桥接电路,至少具

备接收电路141及发送电路144。此外,在本实施方式中,关于第4桥接电路140控制对第4存储器154进行数据读出及写入的例子进行说明,也可以仅进行数据的读出及写入中的任一种。

[0064]

接收电路141具备cdr145。cdr145根据从第3桥接电路130发送的信号,与和写入符号404一起发送来的同步信号(时脉)相位同步。

[0065]

然后,接收电路141以同步信号为基准,从自第3桥接电路130发送而来的(图4所示的)写入符号404,读出第4存储器154用写入数据(1bit)414。然后,接收电路141基于所读出的第4存储器154用写入数据414,进行将该数据写入到第4存储器154的控制。

[0066]

接下来,对本实施方式的存储器系统1的桥接电路(第1桥接电路110~第4桥接电路140)将从第1存储器151~第4存储器154读出的数据交付给存储器控制器100之前的处理进行说明。

[0067]

在本实施方式中,桥接电路(第1桥接电路110~第4桥接电路140)与对第1存储器151~第4存储器154交付写入数据时同样地,对存储器控制器100交付将从第1存储器151~第4存储器154读出的1bit数据(以下,称为读取数据)汇总所得的单位通信数据(读取符号)。

[0068]

首先,发送电路144以同步信号为基准,产生储存有从第4存储器154读出的读取数据的读取符号。同步信号可使用从发送电路132发送来的同步信号,也可以产生新的同步信号。

[0069]

图5是例示在本实施方式的存储器系统1内传送的读取符号的转变的图。如图5所示,发送电路144发送储存有第4存储器154的读取数据(1bit)511的读取符号501。

[0070]

然后,发送电路144将读取符号501中包含有用于产生读取符号501的同步信号所得的信号发送给第3桥接电路130。接下来,对第3桥接电路130的接收电路133及发送电路134进行说明。

[0071]

第3桥接电路130的接收电路133具备cdr136。cdr136根据从第4桥接电路140发送的信号,与和读取符号501一起发送来的同步信号(时脉)相位同步。

[0072]

发送电路134以同步信号为基准,对于读取符号501,在分配为第3存储器153用的区域储存从第3存储器153读出的读取数据(1bit)512,从而产生读取符号502。如图5所示,读取符号502由第3存储器153的读取数据(1bit)512及第4存储器154的读取数据(1bit)511构成。

[0073]

发送电路134将在读取符号502中包含有从cdr136接收的同步信号所得的信号发送给第2桥接电路120。接下来,对第2桥接电路120的接收电路123及发送电路124进行说明。

[0074]

第2桥接电路120的接收电路123具备cdr126。cdr126根据从第3桥接电路130发送的信号,与和读取符号502一起发送来的同步信号(时脉)相位同步。

[0075]

发送电路124以同步信号为基准,对于读取符号502,在分配为第2存储器152用的区域储存从第2存储器152读出的读取数据(1bit)513,从而产生读取符号503。如图5所示,读取符号503由第2存储器152的读取数据(1bit)513、第3存储器153的读取数据(1bit)512及第4存储器154的读取数据(1bit)511构成。

[0076]

发送电路124将在读取符号503中包含有从cdr126接收的同步信号所得的信号发送给第1桥接电路110。发送电路124在发送读取符号503时,进行使采样频率翻倍的上采样。

接下来,对第1桥接电路110的接收电路113及发送电路114进行说明。

[0077]

第1桥接电路110的接收电路113具备cdr116。cdr116根据从第2桥接电路120发送的信号,与和读取符号503一起发送来的同步信号(时脉)相位同步。

[0078]

发送电路114以同步信号为基准,对于读取符号503,在分配为第1存储器151用的区域储存从第1存储器151读出的读取数据(1bit)514,从而产生读取符号504。如图5所示,读取符号504由第1存储器151的读取数据(1bit)514、第2存储器152的读取数据(1bit)513、第3存储器153的读取数据(1bit)512及第4存储器154的读取数据(1bit)511构成。

[0079]

然后,发送电路114将在读取符号504中包含有从cdr116接收的同步信号所得的信号发送给存储器控制器100。

[0080]

由此,存储器控制器100接收读取符号504。在本实施方式中,通过进行所述处理,而存储器控制器100可接收从第1存储器151~第4存储器154读出的每1bit的读取数据。

[0081]

在本实施方式中,根据读取符号及写入符号的时间方向的数据量而进行上采样及下采样。由此,设定与数据量相应的必要充分的频率及振幅,因此可在存储器系统1中实现电力节省。

[0082]

在本实施方式中,在以读取符号发送读取数据的情况下、以及以写入符号发送写入数据的情况下,无须储存用来特定出发送目标的桥接电路的地址信息。由此,可削减所要发送的数据量。

[0083]

此外,在本实施方式中,有关写入第1存储器151~第4存储器154的数据的写入目标的信息可通过将作为写入符号储存的1bit写入数据组合而产生,省略说明。

[0084]

本实施方式中,对第1存储器151、第2存储器152、第3存储器153及第4存储器154为nand型闪速存储器(nand存储器)的封装的情况进行说明,但并不限制于nand型闪速存储器(nand存储器)的封装。另外,在本实施方式中,并不限制设置于存储器系统1的封装的数量、隔着存储器接口而多个并联连接的存储器群、及积层于封装内的存储器芯片群等,而是根据实施形态设置适当数量的封装等。

[0085]

(第1实施方式的变化例1)

[0086]

在第1实施方式中,对同步信号未特别进行限制。可是,在以往将多个桥接电路从属连接的情况下,所有桥接电路的cdr均嵌埋与由该桥接电路发送的数据相应的时脉。在所有桥接电路的cdr均嵌埋时脉的情况下,每次经由桥接电路时都要嵌埋时脉,因此产生被发送的信号所包含的数据的比率降低,有效数据比率下降的问题。因此,在本变化例1中,对抑制有效数据比率的降低的时脉的嵌埋时点进行说明。此外,对于本变化例1的构成,设为与第1实施方式相同。

[0087]

首先,对读取符号用时脉(同步信号)的嵌埋时点进行说明。图6是例示本变化例1中的读取符号与时脉的嵌埋时点的关系的图。如图6所示,从第4桥接电路140发送读取符号601。然后,接收到读取符号601的第3桥接电路130发送读取符号602。接收到读取符号602的第2桥接电路120发送读取符号603。接收到读取符号603的第1桥接电路110发送读取符号604。这样一来,每当经由桥接电路时,读取符号在振幅方向及时间方向上发生变化。

[0088]

然而,与读取符号601的振幅变化的时点相对应的信号边缘610被维持在第1桥接电路110所发送的读取符号604。

[0089]

因此,在本变化例中,第4桥接电路140的发送电路144发送储存有从第4存储器154

读出的1bit数据的读取符号601时,在该读取符号601的振幅变化的时点(信号边缘610),将同步信号(时脉)作为振幅信息嵌埋。此外,将同步信号(时脉)作为振幅信息嵌埋的方法可使用无论是否为周知方法的任何方法。

[0090]

另外,本变化例并不限制数据的传送方式,例如考虑使用nrz(non-return-to-zero,不归零)方式。接下来,对第3桥接电路130的发送电路134在读取符号601中储存第3存储器153的读取数据(1bit)而产生读取符号602时也保留同步信号(时脉)的情况进行说明。

[0091]

图7是例示通过第1实施方式的变化例1中的第4桥接电路140的发送电路144所发送的储存有第4存储器154的读取数据的读取符号的图。在图7所示的例子中,发送电路144在读取符号的振幅变化的时点701、702、703、704嵌埋同步信号(时脉)。

[0092]

图8是表示通过第1实施方式的变化例1中的第3桥接电路130的发送电路134所发送的储存有第3存储器153及第4存储器154的读取数据的读取符号的例子的图。在图8(a)所示的例子中,示出了在第4存储器154的读取数据“0110100”中储存有第3存储器153的读取数据“1010101”的例子。可确认到即便在该情况下,图7中嵌埋了同步信号(时脉)的信号边缘在时点801、802、803、804仍保留。

[0093]

在图8(b)所示的例子中,示出了在第4存储器154的读取数据“0110100”中储存有第3存储器153的读取数据“0000000”的例子。可确认到即便在新储存的读取数据均为“0”的情况下,图7中嵌埋了同步信号(时脉)的信号边缘在时点901、902、903、904仍保留。

[0094]

如图8所示,由于无论储存哪种读取数据,信号边缘均保留,所以无须对每个桥接电路嵌埋新的同步信号(时脉)。

[0095]

然后在时间方向上储存第2存储器152及第1存储器151的读取数据,但当在时间方向上进行追加时,振幅不发生变化,因此当然信号边缘保留,省略说明。

[0096]

接下来,对写入符号用同步信号(时脉)的嵌埋时点进行说明。

[0097]

图9是例示第1实施方式的变化例1中的写入符号与嵌埋时点的关系的图。如图9所示,从存储器控制器100发送写入符号1001。接收到写入符号1001的第1桥接电路110将去除了第1存储器151用写入数据后的写入符号1002发送给第2桥接电路120。

[0098]

接收到写入符号1002的第2桥接电路120发送去除了第2存储器152用写入数据后的写入符号1003。接收到写入符号1003的第3桥接电路130将去除了第3存储器153用写入数据后的写入符号1004发送给第4桥接电路140。这样一来,每当经由桥接电路时,写入符号在振幅方向及时间方向上发生变化。

[0099]

然而,储存有保留到最后的第4存储器154用写入数据的写入符号1004的信号边缘1010存在于写入符号1001~1003中的任一个。

[0100]

因此,存储器控制器100的控制器103在发送包含同步信号及写入符号1001的信号时,在写入符号1001所包含的写入数据中最后被删除的第4存储器用写入数据(1bit)的振幅变化的时点(信号边缘1010),将同步信号(时脉)作为振幅信息嵌埋。

[0101]

由此,在第1桥接电路110~第3桥接电路130中,可不嵌埋同步信号(时脉)而通过第1桥接电路110~第4桥接电路140的每一个,基于同步信号接收写入数据(1bit)。在本变化例中,无须对每个桥接电路嵌埋时脉(同步信号),因此可提升数据的传送效率。

[0102]

(第1实施方式的变化例2)

[0103]

在第1实施方式及其变化例1中,在各接收电路接收到写入符号及读取符号的情况

下,以同步信号进行相位同步时的处理并无特别限制。可是,桥接电路所包含的cdr具备相位追随功能。因此,对于在第1实施方式的变化例2的存储器系统中,cdr具备对于嵌埋在写入符号及读取符号中的时脉的相位同步功能的情形进行说明。此外,本变化例2的构成与第1实施方式相同。也就是说,存储器系统1的cdr115、116、125、126、135、136、145具备相位追随功能。

[0104]

通常,在将桥接电路从属连接的情况下,存在随着信号所通过的桥接电路的数量变多,而该信号所包含的杂讯增加的倾向。因此,产生传送的数据的ber(误比特率:bit error rate)上升的问题。因此,在本变化例2中,对抑制ber上升的cdr115、116、125、126、135、136、145进行说明。

[0105]

首先,对存储器控制器100发送写入符号的情况进行说明,也就是说,对在第1桥接电路110、第2桥接电路120、第3桥接电路130及第4桥接电路140之间收发包含写入符号及同步信号的信号的情况进行说明。

[0106]

在这种情况下,存在随着包含写入符号及同步信号的信号所通过的桥接电路(第1桥接电路110、第2桥接电路120、第3桥接电路130及第4桥接电路140)的数量增加,该信号所包含的杂讯增加的倾向。因此,本变化例2中,各桥接电路的cdr115、125、135、145所具有的相位追随功能根据所通过的桥接电路的数量而扩大追随相位的频带。

[0107]

图10是例示第1实施方式的变化例2中的针对各cdr115、125、135、145进行的相位追随功能的频带的图。图10(a)表示进行第1桥接电路110的cdr115的相位追随功能中的同步信号的相位修正的第1频带1101。该第1频带1101可由任何设定方法设定,根据实施形态而设定适当的频带。在图10所示的例子中,纵轴设为增益,横轴设为相位。

[0108]

第1桥接电路110的cdr115具有在接收到包含同步信号的写入符号1001的情况下,使该信号追随第1频带1101所包含的相位的第1相位追随功能。然后,cdr115进行与嵌埋在写入符号1001中的同步信号相位同步的操作。然后,第1桥接电路110的接收电路111从基于所提取的同步信号而特定出的预先分配给第1存储器151的区域,读出1bit数据。

[0109]

图10(b)设为由第2桥接电路120的cdr125进行相位追随功能的第2频带1102。如图10(a)及(b)所示,第2频带1102比第1频带1101宽。

[0110]

第2桥接电路120的cdr125具有在接收到包含同步信号的写入符号1002的情况下,使该信号追随第2频带1102所包含的相位的第2相位追随功能。然后,cdr125进行与嵌埋在写入符号1002中的同步信号相位同步的操作。然后,第2桥接电路120的接收电路121从基于所提取的同步信号而特定出的预先分配给第2存储器152的区域,读出1bit数据。

[0111]

图10(c)设为由第3桥接电路130的cdr135进行相位追随功能的第3频带1103。如图10(a)、(b)及(c)所示,第3频带1103比第1频带1101及第2频带1102宽。

[0112]

第3桥接电路130的cdr135具有在接收到包含同步信号的写入符号1003的情况下,使该信号追随第3频带1103所包含的相位的第3相位追随功能。cdr135的其它功能与所述实施方式相同,省略说明。

[0113]

图10(d)设为由第4桥接电路140的cdr145进行相位追随功能的第4频带1104。如图10(a)、(b)、(c)及(d)所示,第4频带1104比第1频带1101、第2频带1102及第3频带1103宽。

[0114]

第4桥接电路140的cdr145具有在接收到包含同步信号的写入符号1004的情况下,使该信号追随第4频带1104所包含的相位的第4相位追随功能。cdr145的其它功能与所述实

施方式相同,省略说明。

[0115]

在本变化例2中,通过根据所通过的桥接电路的数量,使cdr的相位追随功能的频带逐渐变宽,而使对于混入所要传送的信号的杂讯的耐性变强。另外,在所通过的桥接电路的数量较少的阶段,频带窄,因此可实现消耗电力的削减。

[0116]

另外,在所述例子中,对于每当进行写入符号的交付时,均要根据所通过的桥接电路的数量使进行cdr的相位追随功能的频带不断变宽的例子进行了说明。

[0117]

然而,本变化例所示的使进行cdr的相位追随功能的频带不断变宽的处理并不限定于在交付写入符号时进行。例如,也可以在每当进行读取符号的交付时,根据所通过的桥接电路的数量使进行cdr的相位追随功能的频带变宽。这样,只要是在多个桥接电路间交付将多个数据汇总而成的符号的形态,那么都可以应用。

[0118]

(第2实施方式)

[0119]

图11是表示第2实施方式的存储器系统1200的构成例的图。存储器系统1200具备通信接口180、存储器控制器100、第1桥接电路1210、第2桥接电路1220、第3桥接电路1230、第4桥接电路1240、第1存储器151、第2存储器152、第3存储器153及第4存储器154。此外,对与第1实施方式相同的构成分配相同的符号,省略说明。

[0120]

在第1实施方式中,对分开交付读取符号与写入符号的例子进行了说明。本实施方式的例子是交付将读取数据与写入数据汇总而成的符号。

[0121]

也就是说,第1桥接电路1210~第4桥接电路1240从预先分配给每个桥接电路的区域,读出符号中的写入数据,将该写入数据从符号中删除后,在该预先分配的区域中储存符号的读取数据。

[0122]

本实施方式的存储器控制器100在启动时,对第1桥接电路1210~第4桥接电路1240发送唯一识别每个桥接电路的id。第1桥接电路1210~第4桥接电路1240可依照所发送的id而识别分配给本桥接电路的区域。

[0123]

图12是表示第2实施方式的第1桥接电路1210~第4桥接电路1240中的构成例的图。

[0124]

第1桥接电路1210是用来控制对第1存储器151进行数据读出及写入的桥接电路,具备接收电路1211及发送电路1212。

[0125]

接收电路1211具备cdr1213。cdr1213根据从存储器控制器100发送的信号,与和符号一起发送来的同步信号(时脉)相位同步。

[0126]

图13是例示在本实施方式的存储器系统1200内发送的符号的转变的图。如图13所示,存储器控制器100发送储存有第1存储器151用写入数据(1bit)1411、第2存储器152用写入数据(1bit)1412、第3存储器153用写入数据(1bit)1413及第4存储器154用写入数据(1bit)1414的符号1401。

[0127]

然后,接收电路1211以同步信号为基准,从预先分配给第1存储器151的区域,读出从存储器控制器100发送而来的(图13所示的)符号1401中的第1存储器151用写入数据(1bit)1411。然后,接收电路1211基于所读出的第1存储器151用写入数据1411,进行将该数据写入到第1存储器151的控制。

[0128]

然后,接收电路1211将符号1401及同步信号交付给发送电路1212。

[0129]

发送电路1212从第1存储器151接收所读出的读取数据。

[0130]

然后,发送电路1212产生如下数据作为符号1402,即,以同步信号为基准,从分配为第1存储器151用的区域将符号1401中的第1存储器151用写入数据(1bit)1411去除后,在分配为第1存储器151用的区域中储存第1存储器151的读取数据(1bit)1421所得的数据。

[0131]

如图13所示,符号1402由第1存储器151的读取数据(1bit)1421、第2存储器152用写入数据(1bit)1412、第3存储器153用写入数据(1bit)1413及第4存储器154用写入数据(1bit)1414构成。

[0132]

然后,发送电路1212将在符号1402中包含有从cdr1213接收的同步信号所得的信号发送给第2桥接电路1220。

[0133]

第2桥接电路1220是用来控制对第2存储器152进行数据读出及写入的桥接电路,具备接收电路1221及发送电路1222。

[0134]

接收电路1221具备cdr1223。cdr1223根据从第1桥接电路1210发送的信号,与和符号1402一起发送来的同步信号(时脉)相位同步。

[0135]

然后,接收电路1221以同步信号为基准,从预先分配给第2存储器152的区域,读出从第1桥接电路1210发送而来的(图13所示的)符号1402中的第2存储器152用写入数据(1bit)1412。然后,接收电路1221基于所读出的第2存储器152用写入数据1412,进行将该数据写入到第2存储器152的控制。

[0136]

然后,接收电路1221将符号1402及同步信号交付给发送电路1222。

[0137]

发送电路1222从第2存储器152接收所读出的读取数据。

[0138]

然后,发送电路1222以同步信号为基准,从分配为第2存储器152用的区域,将符号1402中的第2存储器152用写入数据(1bit)1412去除后,在分配为第2存储器152用的区域中储存第2存储器152的读取数据(1bit)1422,从而产生符号1403。

[0139]

如图13所示,符号1403由第1存储器151的读取数据(1bit)1421、第2存储器152的读取数据(1bit)1422、第3存储器153用写入数据(1bit)1413及第4存储器154用写入数据(1bit)1414构成。

[0140]

然后,发送电路1222将在符号1403中包含有从cdr1223接收的同步信号所得的信号发送给第3桥接电路1230。

[0141]

第3桥接电路1230是用来控制对第3存储器153进行数据读出及写入的桥接电路,具备接收电路1231及发送电路1232。

[0142]

接收电路1231具备cdr1233。cdr1233根据从第2桥接电路1220发送的信号,与和符号1403一起发送来的同步信号(时脉)相位同步。

[0143]

然后,接收电路1231以同步信号为基准,从预先分配给第3存储器153的区域,读出从第2桥接电路1220发送而来的(图13所示的)符号1403中的第3存储器153用写入数据(1bit)1413。然后,接收电路1231基于所读出的第3存储器153用写入数据(1bit)1413,进行将该数据写入到第3存储器153的控制。

[0144]

然后,接收电路1231将符号1403及同步信号交付给发送电路1232。

[0145]

发送电路1232从第3存储器153接收所读出的读取数据。

[0146]

然后,发送电路1232以同步信号为基准,从分配为第3存储器153用的区域,去除符号1403中的第3存储器153用写入数据(1bit)1413后,在分配为第3存储器153用的区域中储存第3存储器153的读取数据(1bit)1423,从而产生符号1404。

[0147]

如图13所示,符号1404由第1存储器151的读取数据1421、第2存储器152的读取数据1422、第3存储器153的读取数据1423及第4存储器154用写入数据(1bit)1414构成。

[0148]

然后,发送电路1232将在符号1404中包含有从cdr1233接收的同步信号所得的信号发送给第4桥接电路1240。

[0149]

第4桥接电路1240是用来控制对第4存储器154进行数据读出及写入的桥接电路,具备接收电路1241及发送电路1242。

[0150]

接收电路1241具备cdr1243。cdr1243根据从第3桥接电路1230发送的信号,与和符号1404一起发送来的同步信号(时脉)相位同步。

[0151]

然后,接收电路1241以同步信号为基准,从预先分配给第4存储器154的区域,读出从第3桥接电路1230发送而来的(图13所示的)符号1404中的第4存储器154用写入数据1414(1bit)。然后,接收电路1241基于所读出的第4存储器154用写入数据(1bit)1414,进行将该数据写入到第4存储器154的控制。

[0152]

然后,接收电路1241将符号1404及同步信号交付给发送电路1242。

[0153]

发送电路1242从第4存储器154接收所读出的读取数据。

[0154]

然后,发送电路1242以同步信号为基准,从分配为第4存储器154用的区域,去除符号1404中的第4存储器154用写入数据(1bit)1414后,在分配为第4存储器154用的区域中储存第4存储器154的读取数据1424,从而产生符号1405。

[0155]

如图13所示,符号1405由第1存储器151的读取数据1421、第2存储器152的读取数据1422、第3存储器153的读取数据1423及第4存储器154的读取数据(1bit)1424构成。

[0156]

然后,发送电路1242将在符号1405中包含有从cdr1243接收的同步信号所得的信号发送给存储器控制器100。

[0157]

在本实施方式中,通过具备所述构成,而可通过在形成为环状的桥接电路1210~1240之间进行符号收发来实现桥接电路1210~1240与存储器控制器100之间的数据收发。此时,无须将地址信息等储存在符号中,因此可提升数据的发送效率。另外,在所述构成的情况下,与以往相比,零件的件数更少,因此可实现消耗电力与成本的削减。

[0158]

(变化例)

[0159]

图14是例示变化例的发送侧的桥接电路及接收侧的桥接电路的构成的图。如图14所示,发送侧的桥接电路1510具备接收电路1511及发送电路1512。本变化例是发送侧的桥接电路1510对读取符号的振幅追加从发送侧的存储器1519读出的读取数据的例子。发送侧的桥接电路1510只要为对振幅追加数据的桥接电路,那么可以是所述实施方式的第1桥接电路~第4桥接电路的任一构成。

[0160]

接收电路1511具备cdr1513,发送电路1512具备选择器1514、异或(exclusive or)电路1516、以及具有第1发送机(tx)及第2发送机(tx)的发送部1517。

[0161]

第1发送机(tx)从第1信号线发送信号。第2发送机(tx)从第2信号线发送信号。由此,发送部1517分别以不同的信号线(第1信号线及第2信号线)发送读取符号与同步信号。

[0162]

接收侧的桥接电路1520至少具备接收电路1521。接收电路1521包含具备第1接收机(rx)及第2接收机(rx)的接收部1524、以及具备异或电路1525的cdr1523。

[0163]

第1接收机(rx)从第1信号线接收信号。第2接收机(rx)从第2信号线接收信号。由此,接收部1524分别以不同的信号线(第1信号线及第2信号线)接收读取符号与同步信号。

[0164]

此外,在使用以往的方法对读取符号的振幅追加读取数据时,当所追加的数据为

‘0’

且保持不变的情况下,储存在读取符号中的数据会产生偏差,因此存在dc(directcurrent,直流)平衡崩溃的可能性。储存在读取符号中的数据产生偏差是指如下状态:因所追加的数据为

‘0’

且保持不变,所以在4个振幅值(信号的电压值)中,仅端侧的2个振幅(电压)间发生变化。利用图15对端侧的2个振幅间进行说明。

[0165]

图15是表示使用以往的方法,以信号线发送读取符号及同步信号的情况下的数据的宽度的图。在图15(a)所示的例子中,在粗线1601及粗线1602之间,读取数据的振幅变化。在图15(b)所示的例子中,在粗线1701及粗线1702之间,同步信号的振幅变化。这样,如果利用以往的方法发送,那么存在数据产生偏差的情况。在这种情况下,存在dc平衡崩溃的可能性。

[0166]

因此,变化例的发送电路1512具备切换所读出的读取数据与所接收的读取符号的选择器1514、以及异或电路1516。此外,变化例对使用读取符号的处理进行说明,但并不限定于使用读取符号的处理,也可以应用于使用写入符号的处理。

[0167]

选择器1514构成为接收从cdr1513发送的读取符号与从发送侧的存储器1519发送的读取数据中的任一个并进行切换,根据是否不在时间方向上储存数据而使数据通过来使用。也就是说,根据桥接电路不同,在追加读取数据时,切换是在时间方向上储存数据还是在振幅方向上追加数据。因此,为了适应该切换而设置选择器1514。

[0168]

异或电路1516在包含从选择器1514输出的读取符号的信号(从存储器1519读取的读取符号、或从设置在比发送侧的桥接电路1510更靠前的桥接电路传送而来的读取符号)与从cdr1513输出的同步信号之间进行异或运算。

[0169]

图16是表示以本变化例的信号线发送的读取符号及同步信号的数据的宽度的图。在图16(a)所示的例子中,在粗线1801及粗线1802之间,读取数据的振幅变化。在图16(b)所示的例子中,在粗线1901及粗线1902之间,同步信号的振幅变化。

[0170]

这样,在本变化例中,通过具备所述构成,可将对从前一桥接电路接收的读取符号进行振幅调变后的数据设为读取符号。也就是说,读取符号是以在4个振幅值(信号的电压值)中的以偏压电压为中心的低电压侧与高电压侧的2个振幅(电压)间变化的方式被调变,因此可维持dc平衡。

[0171]

接收侧的桥接电路1520基于从发送侧的桥接电路1510接收的读取符号及同步信号进行处理。省略处理方法。

[0172]

在所述实施方式及变化例中,通过具备所述构成,可不储存发送目标的桥接电路的地址而实现数据向各桥接电路的发送。由此,可提升数据的发送效率。因此,在实施方式及变化例中,可实现数据的传送速度的提升。

[0173]

对本发明的若干实施方式进行了说明,但这些实施方式是作为示例而提出的,并不意图限定发明的范围。这些新颖的实施方式能以其它各种方式加以实施,可在不脱离发明的主旨的范围内进行各种省略、置换、变更。这些实施方式及其变化包含在发明的范围或主旨中,且包含在权利要求书所记载的发明及其均等的范围内。

[0174]

[符号的说明]

[0175]

1、1200存储器系统

[0176]

100存储器控制器

[0177]

101多工化部

[0178]

102反多工化部

[0179]

103控制器

[0180]

110、1210第1桥接电路

[0181]

111、113、121、123、131、133、141、1211、1221、1231、1241、1511、1521接收电路

[0182]

112、114、122、124、132、134、144、1212、1222、1232、1242、1512发送电路

[0183]

115、116、125、126、135、136、145、1213、1223、1233、1243、1513、1523 cdr

[0184][0185]

120、1220第2桥接电路

[0186]

130、1230第3桥接电路

[0187]

140、1240第4桥接电路

[0188]

151第1存储器

[0189]

152第2存储器

[0190]

153第3存储器

[0191]

154第4存储器

[0192]

180通信接口

[0193]

1510发送侧的桥接电路

[0194]

1514选择器

[0195]

1516、1525异或电路

[0196]

1517发送部

[0197]

1519发送侧的存储器

[0198]

1520接收侧的桥接电路

[0199]

1524接收部

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1