芯片测试方法、装置、设备及存储介质与流程

1.本公开涉及芯片测试技术领域,具体而言,涉及一种芯片测试方法、装置、电子设备及可读存储介质。

背景技术:

2.在芯片制造完成后,测试是用于检测存储器故障的重要环节。系统级测试(system level test,slt)是在系统环境中测试片上系统(system on chip,soc)的测试,可在最终产品组装之前发现一些设计问题。整个slt测试阶段可以包括多个测试项目(test pattern,也称为测试模式),每个测试模式可能会由于诸如主板插双列直插内存模块(dual in-line memory module,dimm)的数量、是否测试得到失效芯片等因素的影响,导致不同测试模式的测试时长不同。slt测试阶段中一些测试模式的测试时间较长,导致slt测试的总时间较长,而在不影响测试效果的前提下,缩短slt测试时间不仅可以减少测试成本,还有助于提高产能。

3.如上所述,如何在不影响测试效果的前提下缩短slt测试时间成为亟待解决的问题。

4.在所述背景技术部分公开的上述信息仅用于加强对本公开的背景的理解,因此它可以包括不构成对本领域普通技术人员已知的现有技术的信息。

技术实现要素:

5.本公开的目的在于提供一种芯片测试方法、装置、电子设备及可读存储介质,可在不影响测试效果的前提下缩短芯片系统级测试的时间。

6.本公开的其他特性和优点将通过下面的详细描述变得显然,或部分地通过本公开的实践而习得。

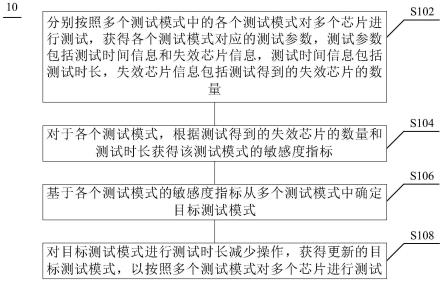

7.根据本公开的一方面,提供一种芯片测试方法,包括:分别按照多个测试模式中的各个测试模式对多个芯片进行测试,获得各个测试模式对应的测试参数,所述测试参数包括测试时间信息和失效芯片信息,所述测试时间信息包括测试时长,所述失效芯片信息包括测试得到的失效芯片的数量;对于各个测试模式,根据测试得到的失效芯片的数量和测试时长获得该测试模式的敏感度指标;基于各个测试模式的敏感度指标从所述多个测试模式中确定目标测试模式;对所述目标测试模式进行测试时长减少操作,获得更新的目标测试模式,以按照多个测试模式对所述多个芯片进行测试。

8.根据本公开的一实施例,对于各个测试模式,根据测试得到的失效芯片的数量和测试时长获得该测试模式的敏感度指标,包括:对于各个测试模式,将测试得到的失效芯片的数量除以测试时长,获得该测试模式的敏感度指标;基于各个测试模式的敏感度指标从所述多个测试模式中确定目标测试模式,包括:获得所述多个测试模式中敏感度指标最低的测试模式,作为所述目标测试模式。

9.根据本公开的一实施例,基于各个测试模式的敏感度指标所述多个测试模式中确

定目标测试模式,还包括:将各个测试模式按照敏感度从高到低的顺序排序,获得测试模式序列;获得所述测试模式序列中除排在首位之外的各个测试模式的特有失效芯片的数量,其中,各个测试模式的特有失效芯片为该测试模式测试得到而在所述测试模式序列中排在该测试模式前的测试模式没有测试得到的失效芯片;获得所述多个测试模式中敏感度指标最低的测试模式,作为所述目标测试模式,包括:若所述多个测试模式中敏感度指标最低的测试模式的特有失效芯片的数量符合第一预设条件,则将所述多个测试模式中敏感度指标最低的测试模式作为所述目标测试模式。

10.根据本公开的一实施例,若所述多个测试模式中敏感度指标最低的测试模式的特有失效芯片的数量符合第一预设条件,则将所述多个测试模式中敏感度指标最低的测试模式作为所述目标测试模式,包括:若所述多个测试模式中敏感度指标最低的测试模式的特有失效芯片的数量符合第一预设条件,并且所述多个测试模式中敏感度指标最低的测试模式的测试时长与特有失效芯片的数量的比值符合第二预设条件,则将所述多个测试模式中敏感度指标最低的测试模式作为所述目标测试模式。

11.根据本公开的一实施例,基于各个测试模式的敏感度指标所述多个测试模式中确定目标测试模式,还包括:将各个测试模式的测试时长相加,获得多个测试模式的总测试时长;根据所述各个测试模式的测试时长、所述多个测试模式的总测试时长、以及各个测试模式的特有失效芯片的数量获得各个测试模式的模式时间减少增益指标;若所述多个测试模式中敏感度指标最低的测试模式的特有失效芯片的数量符合第一预设条件,则将所述多个测试模式中敏感度指标最低的测试模式作为所述目标测试模式,包括:若所述多个测试模式中敏感度指标最低的测试模式的特有失效芯片的数量符合第一预设条件,并且所述多个测试模式中敏感度指标最低的测试模式的模式时间减少增益指标符合第三预设条件,则将所述多个测试模式中敏感度指标最低的测试模式作为所述目标测试模式。

12.根据本公开的一实施例,所述方法还包括:获得所述多个芯片的总芯片数量;基于各个测试模式的敏感度指标所述多个测试模式中确定目标测试模式,包括:将各个测试模式按照敏感度从高到低的顺序排序,获得测试模式序列;根据所述测试模式序列中除排在首位之外的各个测试模式的特有失效芯片的数量和所述总芯片数量获得所述测试模式序列中除排在首位之外的各个测试模式的模式时间减少风险指标;若所述多个测试模式中敏感度指标最低的测试模式的模式时间减少风险指标符合第四预设条件,则将所述多个测试模式中敏感度指标最低的测试模式作为所述目标测试模式。

13.根据本公开的一实施例,若所述多个测试模式中敏感度指标最低的测试模式的模式时间减少风险指标符合第四预设条件,则将所述多个测试模式中敏感度指标最低的测试模式作为所述目标测试模式,包括:若所述多个测试模式中敏感度指标最低的测试模式的模式时间减少风险指标符合第四预设条件,并且所述多个测试模式中敏感度指标最低的测试模式的测试时长与特有失效芯片的数量的比值符合第二预设条件,则将所述多个测试模式中敏感度指标最低的测试模式作为所述目标测试模式。

14.根据本公开的一实施例,基于各个测试模式的敏感度指标所述多个测试模式中确定目标测试模式,还包括:将各个测试模式的测试时长相加,获得多个测试模式的总测试时长;根据所述各个测试模式的测试时长、所述多个测试模式的总测试时长、以及各个测试模式的特有失效芯片的数量获得各个测试模式的模式时间减少增益指标;若所述多个测试模

式中敏感度指标最低的测试模式的模式时间减少风险指标符合第四预设条件,则将所述多个测试模式中敏感度指标最低的测试模式作为所述目标测试模式,包括:若所述多个测试模式中敏感度指标最低的测试模式的模式时间减少风险指标符合第四预设条件,并且所述多个测试模式中敏感度指标最低的测试模式的模式时间减少增益指标符合第三预设条件,则将所述多个测试模式中敏感度指标最低的测试模式作为所述目标测试模式。

15.根据本公开的一实施例,对于各个测试模式,根据测试得到的失效芯片的数量和测试时长获得该测试模式的敏感度指标,包括:对于各个测试模式,将测试得到的失效芯片的数量除以测试时长,获得该测试模式的敏感度指标;将各个测试模式按照敏感度从高到低的顺序排序,获得测试模式序列;获得所述测试模式序列中除排在首位之外的各个测试模式的特有失效芯片的数量,其中,各个测试模式的特有失效芯片为该测试模式测试得到而在所述测试模式序列中排在该测试模式前的测试模式没有测试得到的失效芯片;基于各个测试模式的敏感度指标从所述多个测试模式中确定目标测试模式,包括:根据各个测试模式的敏感度指标以及所述测试模式序列中除排在首位之外的各个测试模式的特有失效芯片的数量从所述多个测试模式中确定目标测试模式。

16.根据本公开的一实施例,所述测试时间信息还包括测试时间点,所述失效芯片信息还包括测试得到失效位元的时间点;对所述目标测试模式进行测试时长减少操作,获得更新的目标测试模式,包括:基于目标测试模式的测试时间点和测试得到失效位元的时间点,确定目标测试模式中的无效数据拓扑,其中,在按照所述目标测试模式对所述多个芯片进行测试的过程中,按照所述无效数据拓扑进行测试的时间点没有得到失效位元;将所述目标测试模式中的无效数据拓扑删除,获得所述更新的目标测试模式。

17.根据本公开的一实施例,基于目标测试模式的测试时间点和测试得到失效位元的时间点,确定目标测试模式中的无效数据拓扑,包括:对于各个测试模式,将测试得到失效位元的时间点按照测试时间点进行归一化,获得失效位元时间比率;将目标测试模式的失效位元时间比率与多个测试模式中除目标测试模式之外的测试模式的失效位元时间比率进行比较,获得目标测试模式中的无效数据拓扑。

18.根据本公开的一实施例,对于各个测试模式,根据测试得到的失效芯片的数量和测试时长获得该测试模式的敏感度指标,包括:对于各个测试模式,将测试得到的失效芯片的数量除以测试时长,获得该测试模式的敏感度指标;基于各个测试模式的敏感度指标从所述多个测试模式中确定目标测试模式,包括:将各个测试模式按照敏感度从高到低的顺序排序,获得测试模式序列;获得所述多个测试模式中敏感度指标最低的测试模式,作为所述目标测试模式;对所述目标测试模式进行测试时长减少操作,获得更新的目标测试模式,以按照多个测试模式对所述多个芯片进行测试,包括:对所述目标测试模式进行测试时长减少操作,获得更新的目标测试模式,以将所述测试模式序列中的所述目标测试模式替换为更新的目标测试模式,获得更新的测试模式序列,并按照所述更新的测试模式序列对所述多个芯片进行测试。

19.根据本公开的再一方面,提供一种芯片测试装置,包括:测试模块,用于分别按照多个测试模式中的各个测试模式对多个芯片进行测试,获得各个测试模式对应的测试参数,所述测试参数包括测试时间信息和失效芯片信息,所述测试时间信息包括测试时长,所述失效芯片信息包括测试得到的失效芯片的数量;获得模块,用于对于各个测试模式,根据

测试得到的失效芯片的数量和测试时长获得该测试模式的敏感度指标;判断模块,用于基于各个测试模式的敏感度指标从所述多个测试模式中确定目标测试模式;处理模块,用于对所述目标测试模式进行测试时长减少操作,获得更新的目标测试模式,以按照多个测试模式对所述多个芯片进行测试。

20.根据本公开的一实施例,所述获得模块,还用于对于各个测试模式,将测试得到的失效芯片的数量除以测试时长,获得该测试模式的敏感度指标;所述判断模块,还用于获得所述多个测试模式中敏感度指标最低的测试模式,作为所述目标测试模式。

21.根据本公开的一实施例,所述获得模块,还用于:将各个测试模式按照敏感度从高到低的顺序排序,获得测试模式序列;获得所述测试模式序列中除排在首位之外的各个测试模式的特有失效芯片的数量,其中,各个测试模式的特有失效芯片为该测试模式测试得到而在所述测试模式序列中排在该测试模式前的测试模式没有测试得到的失效芯片;所述判断模块,还用于:若所述多个测试模式中敏感度指标最低的测试模式的特有失效芯片的数量符合第一预设条件,则将所述多个测试模式中敏感度指标最低的测试模式作为所述目标测试模式。

22.根据本公开的一实施例,所述判断模块,还用于:若所述多个测试模式中敏感度指标最低的测试模式的特有失效芯片的数量符合第一预设条件,并且所述多个测试模式中敏感度指标最低的测试模式的测试时长与特有失效芯片的数量的比值符合第二预设条件,则将所述多个测试模式中敏感度指标最低的测试模式作为所述目标测试模式。

23.根据本公开的一实施例,所述获得模块,还用于:将各个测试模式的测试时长相加,获得多个测试模式的总测试时长;根据所述各个测试模式的测试时长、所述多个测试模式的总测试时长、以及各个测试模式的特有失效芯片的数量获得各个测试模式的模式时间减少增益指标;所述判断模块,还用于:若所述多个测试模式中敏感度指标最低的测试模式的特有失效芯片的数量符合第一预设条件,并且所述多个测试模式中敏感度指标最低的测试模式的模式时间减少增益指标符合第三预设条件,则将所述多个测试模式中敏感度指标最低的测试模式作为所述目标测试模式。

24.根据本公开的一实施例,所述获得模块,还用于获得所述多个芯片的总芯片数量;将各个测试模式按照敏感度从高到低的顺序排序,获得测试模式序列;根据所述测试模式序列中除排在首位之外的各个测试模式的特有失效芯片的数量和所述总芯片数量获得所述测试模式序列中除排在首位之外的各个测试模式的模式时间减少风险指标;所述判断模块,还用于:若所述多个测试模式中敏感度指标最低的测试模式的模式时间减少风险指标符合第四预设条件,则将所述多个测试模式中敏感度指标最低的测试模式作为所述目标测试模式。

25.根据本公开的一实施例,所述判断模块,还用于:若所述多个测试模式中敏感度指标最低的测试模式的模式时间减少风险指标符合第四预设条件,并且所述多个测试模式中敏感度指标最低的测试模式的测试时长与特有失效芯片的数量的比值符合第二预设条件,则将所述多个测试模式中敏感度指标最低的测试模式作为所述目标测试模式。

26.根据本公开的一实施例,所述获得模块,还用于:将各个测试模式的测试时长相加,获得多个测试模式的总测试时长;根据所述各个测试模式的测试时长、所述多个测试模式的总测试时长、以及各个测试模式的特有失效芯片的数量获得各个测试模式的模式时间

减少增益指标;所述判断模块,还用于:若所述多个测试模式中敏感度指标最低的测试模式的模式时间减少风险指标符合第四预设条件,并且所述多个测试模式中敏感度指标最低的测试模式的模式时间减少增益指标符合第三预设条件,则将所述多个测试模式中敏感度指标最低的测试模式作为所述目标测试模式。

27.根据本公开的一实施例,所述获得模块,还用于:对于各个测试模式,将测试得到的失效芯片的数量除以测试时长,获得该测试模式的敏感度指标;将各个测试模式按照敏感度从高到低的顺序排序,获得测试模式序列;获得所述测试模式序列中除排在首位之外的各个测试模式的特有失效芯片的数量,其中,各个测试模式的特有失效芯片为该测试模式测试得到而在所述测试模式序列中排在该测试模式前的测试模式没有测试得到的失效芯片;所述判断模块,还用于:根据各个测试模式的敏感度指标以及所述测试模式序列中除排在首位之外的各个测试模式的特有失效芯片的数量从所述多个测试模式中确定目标测试模式。

28.根据本公开的一实施例,所述测试时间信息还包括测试时间点,所述失效芯片信息还包括测试得到失效位元的时间点;所述处理模块,还用于:基于目标测试模式的测试时间点和测试得到失效位元的时间点,确定目标测试模式中的无效数据拓扑,其中,在按照所述目标测试模式对所述多个芯片进行测试的过程中,按照所述无效数据拓扑进行测试的时间点没有得到失效位元;将所述目标测试模式中的无效数据拓扑删除,获得所述更新的目标测试模式。

29.根据本公开的一实施例,所述处理模块,还用于:对于各个测试模式,将测试得到失效位元的时间点按照测试时间点进行归一化,获得失效位元时间比率;将目标测试模式的失效位元时间比率与多个测试模式中除目标测试模式之外的测试模式的失效位元时间比率进行比较,获得目标测试模式中的无效数据拓扑。

30.根据本公开的一实施例,所述获得模块,还用于:对于各个测试模式,将测试得到的失效芯片的数量除以测试时长,获得该测试模式的敏感度指标;将各个测试模式按照敏感度从高到低的顺序排序,获得测试模式序列;获得所述多个测试模式中敏感度指标最低的测试模式,作为所述目标测试模式;所述处理模块,还用于:对所述目标测试模式进行测试时长减少操作,获得更新的目标测试模式,以将所述测试模式序列中的所述目标测试模式替换为更新的目标测试模式,获得更新的测试模式序列,并按照所述更新的测试模式序列对所述多个芯片进行测试。

31.根据本公开的再一方面,提供一种电子设备,包括:存储器、处理器及存储在所述存储器中并可在所述处理器中运行的可执行指令,所述处理器执行所述可执行指令时实现如上述任一种方法。

32.根据本公开的再一方面,提供一种计算机可读存储介质,其上存储有计算机可执行指令,所述可执行指令被处理器执行时实现如上述任一种方法。

33.本公开的实施例提供的芯片测试方法,首先分别按照多个测试模式中的各个测试模式对多个芯片进行测试,获得各个测试模式对应的测试时长、失效芯片的数量等测试参数,并根据各个测试模式测试得到的失效芯片的数量和测试时长获得该测试模式的敏感度指标,然后基于各个测试模式的敏感度指标从多个测试模式中确定目标测试模式,并对目标测试模式进行测试时长减少操作,获得更新的目标测试模式,以按照多个测试模式对多

个芯片进行测试。本公开的实施例提供的芯片测试方法通过统计多个测试模式的综合了失效芯片的数量和测试时长因素的敏感度指标,并根据该敏感度指标从多个测试模式中确定进行测试时长减少操作目标测试模式,用大数据统计的方法量化不同测试模式捕捉失效芯片的敏感度,可实现选择敏感度较低的测试模式进行测试时长减少操作,从而在不影响测试效果的前提下缩短芯片系统级测试的时间。

34.应当理解的是,以上的一般描述和后文的细节描述仅是示例性的,并不能限制本公开。

附图说明

35.通过参照附图详细描述其示例实施例,本公开的上述和其它目标、特征及优点将变得更加显而易见。

36.图1示出本公开实施例中一种芯片测试方法的流程图。

37.图2示出了图1中所示的步骤s106在一实施例中的处理过程示意图。

38.图3示出了图1中所示的步骤s106在另一实施例中的处理过程示意图。

39.图4示出了图1中所示的步骤s106在再一实施例中的处理过程示意图。

40.图5示出了图1中所示的步骤s106在又一实施例中的处理过程示意图。

41.图6示出了图1中所示的步骤s106在又一实施例中的处理过程示意图。

42.图7示出了图1中所示的步骤s106在又一实施例中的处理过程示意图。

43.图8是根据图1至图7示出的一种目标测试模式的确定方法的流程图。

44.图9示出了图1中所示的步骤s108在一实施例中的处理过程示意图。

45.图10是根据图1至图9示出的一种ttr分析流程示意图。

46.图11是根据表1示出的获得的失效位元时间比率分布图。

47.图12示出本公开实施例中一种芯片测试装置的框图。

48.图13示出本公开实施例中一种电子设备的结构示意图。

具体实施方式

49.现在将参考附图更全面地描述示例实施例。然而,示例实施例能够以多种形式实施,且不应被理解为限于在此阐述的范例;相反,提供这些实施例使得本公开将更加全面和完整,并将示例实施例的构思全面地传达给本领域的技术人员。附图仅为本公开的示意性图解,并非一定是按比例绘制。图中相同的附图标记表示相同或类似的部分,因而将省略对它们的重复描述。

50.此外,所描述的特征、结构或特性可以以任何合适的方式结合在一个或更多实施例中。在下面的描述中,提供许多具体细节从而给出对本公开的实施例的充分理解。然而,本领域技术人员将意识到,可以实践本公开的技术方案而省略所述特定细节中的一个或更多,或者可以采用其它的方法、装置、步骤等。在其它情况下,不详细示出或描述公知结构、方法、装置、实现或者操作以避免喧宾夺主而使得本公开的各方面变得模糊。

51.此外,术语“第一”、“第二”等仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本公开的描述中,“多个”的含义是至少两个,例如

两个,三个等,除非另有明确具体的限定。符号“/”一般表示前后关联对象是一种“或”的关系。

52.在本公开中,除非另有明确的规定和限定,“连接”等术语应做广义理解,例如,可以是电连接或可以互相通讯;可以是直接相连,也可以通过中间媒介间接相连。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本公开中的具体含义。

53.如上所述,系统级测试阶段进行减少测试时间(test time reduction,ttr)操作不仅可以减少测试成本,还可以提高产能,因此ttr的重要性是不言而喻的。

54.本公开提供了一种芯片测试方法,通过统计多个测试模式的综合了失效芯片的数量和测试时长因素的敏感度指标,并根据该敏感度指标从多个测试模式中确定进行测试时长减少操作目标测试模式,用大数据统计的方法量化不同测试模式捕捉失效芯片的敏感度,可实现选择敏感度较低的测试模式进行测试时长减少操作,从而在不影响测试效果的前提下缩短芯片系统级测试的时间。

55.图1是根据一示例性实施例示出的一种芯片测试方法的流程图。如图1所示的方法例如可以应用于可以实现接收数据、按照配置处理数据、发送或导出数据处理结果等功能的电子设备。

56.参考图1,本公开实施例提供的方法10可以包括以下步骤。

57.在步骤s102中,分别按照多个测试模式中的各个测试模式对多个芯片进行测试,获得各个测试模式对应的测试参数,测试参数包括测试时间信息和失效芯片信息,测试时间信息包括测试时长,失效芯片信息包括测试得到的失效芯片的数量。

58.在一些实施例中,在slt阶段可将不同的测试模式按照一定顺序进行测试,不同的测试模式例如可以为行进(march)模式,比特均衡(bit equalize)模式、棋盘(checkerboard)模式、耦合(coupling)模式等等。

59.在一些实施例中,对于双列直插式内存模块(dual in-line memory module,dimm)进行的slt,例如带寄存器的双列直插内存模块(registered dimm,rdimm)、无缓冲双列直插内存模块(unbuffered dimm,udimm)和小型双列直插式内存模块(small dimm,sodimm)等等,可以得到测试时长、测试得到的失效芯片的数量等测试参数,各自测试模式下还均可得到对应的失效位元(failure bit)、失效发生的时间、测试温度和失效模型等信息。

60.以上列出的进行测试的芯片的类型仅作示例,本公开并不以此为限。

61.上述的测试参数也不限于在某测试条件下得到,数据源的资料大小或类型也不作限制。

62.本公开实施例提供的方法对于不同的测试平台、不同代的产品如ddr3,ddr4,ddr5,ddr6等均适用。

63.在步骤s104中,对于各个测试模式,根据测试得到的失效芯片的数量和测试时长获得该测试模式的敏感度指标。

64.在一些实施例中,可将测试得到的失效芯片的数量除以测试时长,获得该测试模式的敏感度指标。例如,可将测试得到的失效芯片的数量表示为fcc(fail chip counts),将测试时长表示为tt(test time),则敏感度指标sensitivity可以表示为:sensitivity=fcc/tt。

65.在另一些实施例中,也可用其他方式定义sensitivity,例如sensitivity=a*fcc/(b*tt),其中a、b为可配置的系数。定义sensitivity的宗旨是fcc与tt对sensitivity的大小影响是相反的,具体形式本公开不作限制。

66.可根据不同测试对象选择合适的敏感度指标的定义方式,本公开对此不作限制。

67.在步骤s106中,基于各个测试模式的敏感度指标从多个测试模式中确定目标测试模式。

68.在一些实施例中,以上述定义敏感度指标sensitivity的方法为例,若将sensitivity定义为fcc越大、tt越小,sensitivity越大,则可获得多个测试模式中敏感度指标最低的测试模式作为目标测试模式。

69.在另一些实施例中,若将sensitivity定义为fcc越小、tt越大,sensitivity越大,则可获得多个测试模式中敏感度指标最高的测试模式作为目标测试模式。

70.在另一些实施例中,除了在确定待进行ttr的目标测试模式时考虑敏感度指标因素之外,还可以综合考虑特有失效芯片的数量因素,具体实施方式可参照图2和图8。

71.在另一些实施例中,除了在确定待进行ttr的目标测试模式时考虑敏感度指标因素之外,还可以综合考虑特有失效芯片的数量因素、以及测试时长与特有失效芯片的数量的比值因素,具体实施方式可参照图3。

72.在另一些实施例中,除了在确定待进行ttr的目标测试模式时考虑敏感度指标因素之外,还可以综合考虑特有失效芯片的数量因素、以及模式时间减少增益指标因素,具体实施方式可参照图4。

73.在另一些实施例中,除了在确定待进行ttr的目标测试模式时考虑敏感度指标因素之外,还可以综合考虑模式时间减少风险指标因素,具体实施方式可参照图5。

74.在另一些实施例中,除了在确定待进行ttr的目标测试模式时考虑敏感度指标因素之外,还可以综合考虑模式时间减少风险指标因素、以及测试时长与特有失效芯片的数量的比值因素,具体实施方式可参照图6。

75.在另一些实施例中,除了在确定待进行ttr的目标测试模式时考虑敏感度指标因素之外,还可以综合考虑模式时间减少风险指标因素、以及模式时间减少增益指标因素,具体实施方式可参照图7。

76.在步骤s108中,对目标测试模式进行测试时长减少操作,获得更新的目标测试模式,以按照多个测试模式对多个芯片进行测试。

77.在一些实施例中,在确定目标测试模式之后,可确定目标测试模式中的无效数据拓扑,并将目标测试模式中的无效数据拓扑删除,以获得更新的目标测试模式,具体实施方式可参照图9。

78.在一些实施例中,对目标测试模式进行测试时长减少操作,获得更新的目标测试模式后,可将测试模式序列中的目标测试模式替换为更新的目标测试模式,获得更新的测试模式序列,并按照更新的测试模式序列对多个芯片进行测试。

79.在一些实施例中,若无法确定目标测试模式中的无效数据拓扑,也可以直接将目标测试模式删除作为ttr操作,将剩余的测试模式按照确定目标测试模式中的无效数据拓扑的顺序进行slt。

80.根据本公开实施例提供的芯片测试方法,通过统计多个测试模式的综合了失效芯

片的数量和测试时长因素的敏感度指标,并根据该敏感度指标从多个测试模式中确定进行测试时长减少操作目标测试模式,用大数据统计的方法量化不同测试模式捕捉失效芯片的敏感度,可实现选择敏感度较低的测试模式进行测试时长减少操作,从而在不影响测试效果的前提下缩短芯片系统级测试的时间。

81.图2示出了图1中所示的步骤s106在一实施例中的处理过程示意图。如图2所示,本公开实施例中,上述步骤s106可以进一步包括以下步骤。

82.步骤s202,将各个测试模式按照敏感度从高到低的顺序排序,获得测试模式序列。

83.在一些实施例中,以将sensitivity定义为fcc越大、tt越小,sensitivity越大为例,将各个测试模式按照敏感度从高到低的顺序排序,即初步按照sensitivity调整测试顺序,以将测试收益更高的测试模式放在前面进行。

84.步骤s204,获得测试模式序列中除排在首位之外的各个测试模式的特有失效芯片的数量,其中,各个测试模式的特有失效芯片为该测试模式测试得到而在测试模式序列中排在该测试模式前的测试模式没有测试得到的失效芯片。

85.在一些实施例中,不同的测试模式可以测试得到同一颗芯片失效(failure)的结果,也可以得到不同的失效芯片,这样对于同一颗芯片可能在不同的测试模式上有不同的失效位元的情况,就可以在不同的测试模式上进行记录。获得的各个测试模式的失效芯片信息包括测试得到的失效芯片的标识,可按照测试得到的失效芯片的标识将一个测试模式覆盖范围(可以为测试得到的失效芯片)与排在其前面的测试模式的覆盖范围做比较,获得测试模式序列中各个测试模式的特有失效芯片的数量(unique fail chip counts),特有失效芯片的数量可表示为u_fcc。对于一个测试模式来说,其u_fcc越小,将其确定为待进行ttr的目标测试模式,对slt整体效果可能产生的影响越小。

86.在另一些实施例中,测试模式覆盖范围还可以为测试得到的失效芯片的位元,即将失效信息具体到某个失效芯片的某个位元,以此获得特有失效芯片,例如在对一个测试模式的u_fcc进行计数时,测试得到失效芯片1的失效位元为11、22,排在该测试模式前面的测试模式也测试得到失效芯片1,但失效位元为33,则仍将失效芯片1记为该测试模式的一个u_fcc。从而可以测试得到多样的失效模式(fail mode),例如单一位元失效(single bit fail)、列失效(column fail)等等,采用此种定义方式的u_fcc计算下方相关指标也更为精确。

87.在一些实施例中,排在首位的测试模式的特有失效芯片的数量u_fcc可为该测试模式的测试得到的失效芯片的数量fcc。

88.步骤s206,若多个测试模式中敏感度指标最低的测试模式的特有失效芯片的数量符合第一预设条件,则将多个测试模式中敏感度指标最低的测试模式作为目标测试模式。

89.在一些实施例中,第一预设条件可以是在多个测试模式中该测试模式的特有失效芯片的数量最少,这样可使将其确定为待进行ttr的目标测试模式可能对slt整体效果产生的影响降到最低。

90.在另一些实施例中,第一预设条件也可以是该测试模式的特有失效芯片的数量低于预设阈值,该预设阈值例如可以是10、或8、或5等等,这样可使将其确定为待进行ttr的目标测试模式可能对slt整体效果产生的影响降到可控范围内。

91.根据本公开实施例提供的目标测试模式确定方法,可在多个测试模式中敏感度指

标最低的测试模式的特有失效芯片的数量也相对较少的情况下,将该测试模式确定为待进行ttr的目标测试模式,可将ttr操作可能对slt整体效果产生的影响降到最低或至少降到可控范围内。

92.图3示出了图1中所示的步骤s106在另一实施例中的处理过程示意图。如图3所示,本公开实施例中,上述步骤s106可以进一步包括以下步骤。

93.步骤s302,将各个测试模式按照敏感度从高到低的顺序排序,获得测试模式序列。

94.步骤s302在一些实施例中的具体实施方式可参照步骤s202。

95.步骤s304,获得测试模式序列中除排在首位之外的各个测试模式的特有失效芯片的数量。

96.步骤s304在一些实施例中的具体实施方式可参照步骤s204。

97.步骤s306,若多个测试模式中敏感度指标最低的测试模式的特有失效芯片的数量符合第一预设条件,并且多个测试模式中敏感度指标最低的测试模式的测试时长与特有失效芯片的数量的比值符合第二预设条件,则将多个测试模式中敏感度指标最低的测试模式作为目标测试模式。

98.在一些实施例中,可以用一个测试模式的测试时长tt与特有失效芯片的数量u_fcc的比值来衡量将该测试模式确定为待进行ttr的目标测试模式的预期收益,tt越大、u_fcc越小,将该测试模式确定为待进行ttr的目标测试模式的预期收益就越大。

99.在一些实施例中,第二预设条件可以为在多个测试模式中该测试模式的tt/u_fcc最大,这样可使将其确定为待进行ttr的目标测试模式的预期收益最大。

100.在另一些实施例中,第二预设条件可以为该测试模式的tt/u_fcc大于预设阈值,这样可使将其确定为待进行ttr的目标测试模式的预期收益不小于可接受的最低收益。

101.根据本公开实施例提供的目标测试模式确定方法,可在多个测试模式中敏感度指标最低的测试模式的测试时长与特有失效芯片的数量的比值也相对较大的情况下,将该测试模式确定为待进行ttr的目标测试模式,可使该ttr操作的预期收益最大或至少不小于可接受的最低收益。

102.图4示出了图1中所示的步骤s106在再一实施例中的处理过程示意图。如图4所示,本公开实施例中,上述步骤s106可以进一步包括以下步骤。

103.步骤s402,将各个测试模式按照敏感度从高到低的顺序排序,获得测试模式序列。

104.步骤s402在一些实施例中的具体实施方式可参照步骤s202。

105.步骤s404,获得测试模式序列中除排在首位之外的各个测试模式的特有失效芯片的数量。

106.步骤s404在一些实施例中的具体实施方式可参照步骤s204。

107.步骤s406,将各个测试模式的测试时长相加,获得多个测试模式的总测试时长。

108.在一些实施例中,可以将多个测试模式的总测试时长(total test time)表示为ttt。

109.步骤s408,根据各个测试模式的测试时长、多个测试模式的总测试时长、以及各个测试模式的特有失效芯片的数量获得各个测试模式的模式时间减少增益指标。

110.在一些实施例中,可以定义,然后据此定义模式时间减少增益(pattern reduce gain)指标prg=(tt/ttt)/u_fcc,对于各个测试模式来说ttt是相同的,因此tt越大、u_fcc

越小,prg越大,将该测试模式确定为待进行ttr的目标测试模式的预期收益就越大。

111.步骤s410,若多个测试模式中敏感度指标最低的测试模式的特有失效芯片的数量符合第一预设条件,并且多个测试模式中敏感度指标最低的测试模式的模式时间减少增益指标符合第三预设条件,则将多个测试模式中敏感度指标最低的测试模式作为目标测试模式。

112.在一些实施例中,第三预设条件可以为在多个测试模式中该测试模式的prg最大,这样可使将其确定为待进行ttr的目标测试模式的预期收益最大。

113.在另一些实施例中,第三预设条件可以为该测试模式的prg大于预设阈值,这样可使将其确定为待进行ttr的目标测试模式的预期收益不小于可接受的最低收益。

114.根据本公开实施例提供的目标测试模式确定方法,可在多个测试模式中敏感度指标最低的测试模式的特有失效芯片的数量相对较少、模式时间减少增益指标也相对较大的情况下,将该测试模式确定为待进行ttr的目标测试模式,可在将ttr操作可能对slt整体效果产生的影响降到最低或至少降到可控范围内的同时,使该ttr操作的预期收益最大或至少不小于可接受的最低收益。

115.图5示出了图1中所示的步骤s106在又一实施例中的处理过程示意图。如图5所示,本公开实施例中,上述步骤s106可以进一步包括以下步骤。

116.步骤s502,获得多个芯片的总芯片数量。

117.在一些实施例中,可以将进行slt测试的多个芯片的总芯片数量(total chip count)表示为tcc。

118.步骤s504,将各个测试模式按照敏感度从高到低的顺序排序,获得测试模式序列。

119.步骤s504在一些实施例中的具体实施方式可参照步骤s202。

120.步骤s506,获得测试模式序列中除排在首位之外的各个测试模式的特有失效芯片的数量。

121.步骤s506在一些实施例中的具体实施方式可参照步骤s204。

122.步骤s508,根据测试模式序列中除排在首位之外的各个测试模式的特有失效芯片的数量和总芯片数量获得测试模式序列中除排在首位之外的各个测试模式的模式时间减少风险指标。

123.在一些实施例中,可以用一个测试模式的特有失效芯片的数量u_fcc与总芯片数量tcc的比值来衡量将该测试模式确定为待进行ttr的目标测试模式的风险,即作为模式时间减少风险指标,可将模式时间减少风险(pattern reduce risk))指标表示为prr,例如prr=u_fcc/tcc,总芯片数量tcc对于各个测试模式来说是相同的,u_fcc越大,将该测试模式确定为待进行ttr的目标测试模式的风险就越大。根据大数定律,当数据量很大的时候prr就是风险发生的概率。

124.步骤s510,若多个测试模式中敏感度指标最低的测试模式的模式时间减少风险指标符合第四预设条件,则将多个测试模式中敏感度指标最低的测试模式作为目标测试模式。

125.在一些实施例中,第四预设条件可以为在多个测试模式中该测试模式的prr最小,这样可使将其确定为待进行ttr的目标测试模式的风险发生的概率最小。

126.在另一些实施例中,第四预设条件可以为该测试模式的prr小于预设阈值,这样可

使将其确定为待进行ttr的目标测试模式的风险发生的概率限制在可控范围内。

127.根据本公开实施例提供的目标测试模式确定方法,可在多个测试模式中敏感度指标最低的测试模式的模式时间减少风险指标也相对较低的情况下,将该测试模式确定为待进行ttr的目标测试模式,可使该ttr操作带来的风险发生的概率降到最低或限制在可控范围内。

128.图6示出了图1中所示的步骤s106在又一实施例中的处理过程示意图。图6与图5的区别在于,在确定目标测试模式时,还考虑了测试时长与特有失效芯片的数量的比值因素。如图6所示,本公开实施例中,上述步骤s106可以进一步包括以下步骤。

129.步骤s602,获得多个芯片的总芯片数量。

130.步骤s602在一些实施例中的具体实施方式可参照步骤s502。

131.步骤s604,将各个测试模式按照敏感度从高到低的顺序排序,获得测试模式序列。

132.步骤s604在一些实施例中的具体实施方式可参照步骤s202。

133.步骤s606,获得测试模式序列中除排在首位之外的各个测试模式的特有失效芯片的数量。

134.步骤s606在一些实施例中的具体实施方式可参照步骤s204。

135.步骤s608,根据测试模式序列中除排在首位之外的各个测试模式的特有失效芯片的数量和总芯片数量获得测试模式序列中除排在首位之外的各个测试模式的模式时间减少风险指标。

136.步骤s608在一些实施例中的具体实施方式可参照步骤s508。

137.步骤s610,若多个测试模式中敏感度指标最低的测试模式的模式时间减少风险指标符合第四预设条件,并且多个测试模式中敏感度指标最低的测试模式的测试时长与特有失效芯片的数量的比值符合第二预设条件,则将多个测试模式中敏感度指标最低的测试模式作为目标测试模式。

138.第四预设条件的具体实施方式可以参照步骤s510,第二预设条件的具体实施方式可以参照步骤s306。

139.根据本公开实施例提供的目标测试模式确定方法,可在多个测试模式中敏感度指标最低的测试模式的模式时间减少风险指标也相对较低、测试时长与特有失效芯片的数量的比值也相对较大的情况下,将该测试模式确定为待进行ttr的目标测试模式,可使该ttr操作带来的风险发生的概率降到最低或限制在可控范围内的同时,使该ttr操作的预期收益最大或至少不小于可接受的最低收益。

140.图7示出了图1中所示的步骤s106在又一实施例中的处理过程示意图。图7与图5的区别在于,在确定目标测试模式时,还考虑了模式时间减少增益因素。如图7所示,本公开实施例中,上述步骤s106可以进一步包括以下步骤。

141.步骤s702,获得多个芯片的总芯片数量。

142.步骤s702在一些实施例中的具体实施方式可参照步骤s502。

143.步骤s704,将各个测试模式按照敏感度从高到低的顺序排序,获得测试模式序列。

144.步骤s704在一些实施例中的具体实施方式可参照步骤s202。

145.步骤s706,获得测试模式序列中除排在首位之外的各个测试模式的特有失效芯片的数量。

146.步骤s706在一些实施例中的具体实施方式可参照步骤s204。

147.步骤s708,根据测试模式序列中除排在首位之外的各个测试模式的特有失效芯片的数量和总芯片数量获得测试模式序列中除排在首位之外的各个测试模式的模式时间减少风险指标。

148.步骤s708在一些实施例中的具体实施方式可参照步骤s508。

149.步骤s710,将各个测试模式的测试时长相加,获得多个测试模式的总测试时长。

150.步骤s710在一些实施例中的具体实施方式可参照步骤s406。

151.步骤s712,根据各个测试模式的测试时长、多个测试模式的总测试时长、以及各个测试模式的特有失效芯片的数量获得各个测试模式的模式时间减少增益指标。

152.步骤s712在一些实施例中的具体实施方式可参照步骤s408。

153.步骤s714,若多个测试模式中敏感度指标最低的测试模式的模式时间减少风险指标符合第四预设条件,并且多个测试模式中敏感度指标最低的测试模式的模式时间减少增益指标符合第三预设条件,则将多个测试模式中敏感度指标最低的测试模式作为目标测试模式。

154.第四预设条件的具体实施方式可以参照步骤s510,第三预设条件的具体实施方式可以参照步骤s410。

155.根据本公开实施例提供的目标测试模式确定方法,可在多个测试模式中敏感度指标最低的测试模式的模式时间减少风险指标也相对较低、模式时间减少增益指标也相对较大的情况下,将该测试模式确定为待进行ttr的目标测试模式,可使该ttr操作带来的风险发生的概率降到最低或限制在可控范围内的同时,使该ttr操作的预期收益最大或至少不小于可接受的最低收益。

156.图8是根据图1至图7示出的一种目标测试模式的确定方法的流程图。参考图8,本公开实施例提供的方法80可以包括以下步骤。

157.在步骤s802中,分别按照多个测试模式中的各个测试模式对多个芯片进行测试,获得各个测试模式对应的测试参数。

158.步骤s802在一些实施例中的具体实施方式可参照步骤s102。

159.在步骤s804中,对于各个测试模式,将测试得到的失效芯片的数量除以测试时长,获得该测试模式的敏感度指标。

160.步骤s804在一些实施例中的具体实施方式可参照步骤s104。

161.在步骤s806中,将各个测试模式按照敏感度从高到低的顺序排序,获得测试模式序列。

162.步骤s806在一些实施例中的具体实施方式可参照步骤s202。

163.在步骤s808中,获得测试模式序列中除排在首位之外的各个测试模式的特有失效芯片的数量。

164.步骤s808在一些实施例中的具体实施方式可参照步骤s204。

165.在步骤s810中,根据各个测试模式的敏感度指标以及测试模式序列中除排在首位之外的各个测试模式的特有失效芯片的数量从多个测试模式中确定目标测试模式。

166.在一些实施例中,在确定目标测试模式时,可综合各个测试模式的敏感度指标sensitivity和特有失效芯片的数量u_fcc,例如,可将各个测试模式的sensitivity和u_

fcc加权相加获得各个测试模式的ttr参考指标,以使对于一个测试模式,其sensitivity越小、u_fcc越小,ttr参考指标越小(或者越大,在权重为均为负数时ttr),然后从多个测试模式中确定ttr参考指标最小的测试模式为目标测试模式。

167.在另一些实施例中,还可将sensitivity、prr与prg的倒数等加权相加获得各个测试模式的ttr参考指标,再从多个测试模式中确定ttr参考指标最小的测试模式为目标测试模式,可综合将其确定为待进行ttr的目标测试模式的预期收益因素来确定目标测试模式。

168.根据本公开实施例提供的目标测试模式确定方法,将sensitivity和u_fcc均最小的测试模式确定为待进行ttr的目标测试模式,可实现综合对slt整体效果可能产生的影响来选择敏感度较低的测试模式进行测试时长减少操作。

169.图9示出了图1中所示的步骤s108在一实施例中的处理过程示意图。参照图1,步骤s102中获得的测试时间信息还可以包括测试时间点,获得的失效芯片信息还可以包括测试得到失效位元的时间点。如图9所示,本公开实施例中,上述步骤s108可以进一步包括以下步骤。

170.步骤s902,基于目标测试模式的测试时间点和测试得到失效位元的时间点,确定目标测试模式中的无效数据拓扑,其中,在按照目标测试模式对多个芯片进行测试的过程中,按照无效数据拓扑进行测试的时间点没有得到失效位元。

171.在一些实施例中,在一个测试模式的不同时间阶段可采用不同的数据拓扑(data topo),不同的数据拓扑的测试效果可能不同,例如某个数据拓扑测不到失效位元,即为该测试模式的无效数据拓扑。

172.可将各个测试模式的数据拓扑进行比较,以获得目标测试模式中的无效数据拓扑用于ttr。对于slt,一个测试模式的测试时间tt受很多因素影响,例如与是否发生failure有关、与所插dimm数量有关等等,导致不同的测试模式的测试时间不同。可以将各个测试模式的data topo按照tt进行归一化进行比较,可参照以下步骤s9022和步骤s9024。

173.步骤s9022,对于各个测试模式,将测试得到失效位元的时间点按照测试时间点进行归一化,获得失效位元时间比率。

174.步骤s9024,将目标测试模式的失效位元时间比率与多个测试模式中除目标测试模式之外的测试模式的失效位元时间比率进行比较,获得目标测试模式中的无效数据拓扑。

175.在一些实施例中,对于无需进行ttr的测试模式,测试得到失效位元的时间点接近均匀分布,即失效位元时间比率在归一化的时间轴上均匀分布,因此将目标测试模式的失效位元时间比率与其他测试模式比较,可以获得目标测试模式的无效数据拓扑。

176.步骤s904,将目标测试模式中的无效数据拓扑删除,获得更新的目标测试模式。

177.根据本公开实施例提供的方法,对不同测试模式的出现失效位元的data topo按照测试时间归一化处理,得到了在归一的测试时间中出现失效位元的位置,从而对应出能抓到失效位元的data topo,这样可以对目标测试模式进行拆解找到无效数据拓扑,并将目标测试模式中的无效数据拓扑删除从而达到ttr的目的。

178.相关技术中从芯片级寻找被覆盖的测试模式,即若一个测试模式测试得到的失效芯片全部被其它测试模式覆盖,则将该测试模式删除以节省测试时间。虽然不同的测试模式之间捕捉失效信息可能会有重叠,但是整个slt测试阶段的测试模式会有各自捕捉失效

信息的侧重点,因此直接删除失效芯片被覆盖的测试模式可能漏掉一些没有覆盖到的失效位元信息,导致测试结果不精确,

179.本公开提供的方法从位元级出发,用大数据统计方法确定目标测试模式后,统计各测试模式不同目标测试模式的失效位元在测试过程中的情况,挖掘了目标测试模式的无效数据拓扑信息,提供可以ttr的更为准确的方向。

180.图10是根据图1至图9示出的一种ttr分析流程示意图。如图10所示,ttr分析流程可以包括以下步骤s1002至步骤s1008。

181.s1002.获取slt测试资料,并用大数据统计方法去除异常数据。

182.在一些实施例中,可以获得一个测试机台在一段时间内的slt测试数据,首先用大数据统计方法进行异常数据排除,例如可以对于各个测试模式,将每次的实际测试时间tt进行统计并计算平均值,将实际测试时间tt与平均值的偏差超过3倍标准差的值作为异常值,认为该次测试无效并进行剔除。异常值的具体判断方法可以根据实际情况进行调整,上述方法仅为示例,本公开并不以此为限。

183.例如,去除异常数据后,可以获得2022/1/28~2022/4/28共3个月某测试机台所测(约30万颗颗粒)rdimm的slt测试资料,其中包括模式1至模式14共14个测试模式,得到的各个模式的tt和fcc可参照表1。

184.表1

185.模式名称tt/秒fcc/个1525513725734731466144459667533921146600577269319388436915346410473111552621256388137708191422248

186.s1004.根据测试资料中不同类型的数据计算多个参考指标。

187.在一些实施例中,参照图1,可先根据tt和fcc计算出敏感度指标sensitivity,例如,以表1中的某测试机台所测rdimm的slt测试数据为例,计算得到各模式的sensitivity如下表2。

188.表2

189.模式名称tt/秒fcc/个sensitivity152551370.02607

2573470.082024314661440.0982264596670.112416533921140.0336086600570.095726931930.071667884360.42857191534640.0417211047310.65957411552620.11231912563880.156306137708190.00246514222480.216216

190.然后参照图2,可将各模式按照sensitivity从大到小进行排列,获得测试模式序列后,据此计算各个测试模式的u_fcc。再参照图3至图9,可分别获得各个测试模式的prr和prg,例如,仍以表1中的某测试机台所测rdimm的slt测试数据为例,按照测试模式序列列出各模式的sensitivity、u_fcc、prr和prg如下表3。

191.表3

192.模式名称tt/秒sensitivityu_fccprrprg10470.659574319.740e-050.0028188840.428571237.226e-050.007752142220.216216299.112e-050.040607125630.156306521.634e-040.14245345960.112416288.797e-050.209679115520.112319195.970e-050.194367314660.098226772.419e-040.59025966000.095123.770e-050.24978425730.082024123.770e-050.276279726930.071667862.702e-041.486115915340.041721185.655e-051.454145533920.033608361.131e-043.991571152550.02607642.011e-047.9719011377080.00246541.257e-05123.6707

193.s1006.按照评价标准根据多个参考指标获取ttr的方向和测试模式顺序,并分析不同测试模式中数据拓扑的效果,获得无效的数据拓扑。

194.在一些实施例中,参照表3,首先根据sensitivity将多个模式进行排序,然后按照新顺序计算u_fcc,再计算prr、prg的值。从表1中可以得到sensitivity较小的模式有模式13、1和5,而且这些模式的tt都比较长。然后参照表3,模式13、1和5中,只有模式13的u_fcc相对其他模式较小、prr相对其他模式较小、prg相对其他模式较大,模式1和5的u_fcc相对

其他模式并不小,prr相对其他模式也不小。从而可以确定出,可以ttr的测试模式即为模式13。

195.在一些实施例中,参照图9,可按照测试时间对将测试得到失效位元的时间点进行归一化,仍以表1中的某测试机台所测rdimm的slt测试数据为例,图11是根据表1示出的获得的失效位元时间比率分布图。如图11所示,除模式13之外的其他模式的测试得到失效位元的时间点绝大部分均匀地分布在测试时间全称中,而模式13除了0.0-0.1以及0.3-0.4的时间比率内出现有失效位元的点之外,其他时间没有失效位元,因此可以只选取出现失效位元的0.0-0.1以及0.3-0.4对应的两段时间的数据拓扑,删掉其他的无效数据拓扑,从而节省测试时间。

196.s1008.将分析结果反馈给用户。

197.在一些实施例中,用户还可以按照表3中的排序进行测试模式顺序的优化,可将sensitivity较大的模式先进行测试,尽快获得较多的fcc。对于一个测试而言,测试时间本身即为成本,而且测试时间太长也会影响产量,进而影响收益,因此本公开实施例提供的方法可以节约测试成本,提高测试收益。

198.在一些实施例中,用户可以根据上述分析将模式13的无效数据拓扑删除后进行测试。相关技术中只按照某个测试模式的失效芯片的数量进行ttr,参照表2,模式7捕捉到的失效芯片的数量最多,但是它的sensitivity只有0.071667并不是太高,也就是说这个模式耗时长,它单位时间抓到的失效芯片并不多,并不是很有效率,所以可以按照表3的顺序,将其排到后面,提高测试收益。

199.在一些实施例中,sensitivity可以仅作为测试重新排序使用的参考指标,真正是否要删除或者分解这个模式可以参照计算的prr、prg的值,以及各个模式的数据拓扑失效位元时间比率的分布情况,从而形成ttr后的更新测试顺序。

200.在一些实施例中,对于dimm而言,e-fuse是目前应对出现失效位元的最节省成本的方法,即把原来失效的地方用别的冗余部分修补。由于系统级测试通常不会测到冗余部分,所以将冗余部分修补后,需要重新进行slt,此时可采用更新测试顺序进行测试。

201.图12是根据一示例性实施例示出的一种芯片测试装置的框图。如图12所示的装置例如可以应用于可以实现接收数据、按照配置处理数据、发送或导出数据处理结果等功能的电子设备。

202.参考图12,本公开实施例提供的装置120可以包括测试模块1202、获得模块1204、判断模块1206和处理模块1208。

203.测试模块1202可用于分别按照多个测试模式中的各个测试模式对多个芯片进行测试,获得各个测试模式对应的测试参数。

204.测试参数可以包括测试时间信息和失效芯片信息,测试时间信息可以包括测试时长,失效芯片信息可以包括测试得到的失效芯片的数量。

205.测试时间信息还可以包括测试时间点,失效芯片信息还可以包括测试得到失效位元的时间点。

206.获得模块1204可用于对于各个测试模式,根据测试得到的失效芯片的数量和测试时长获得该测试模式的敏感度指标。

207.获得模块1204还可用于对于各个测试模式,将测试得到的失效芯片的数量除以测

试时长,获得该测试模式的敏感度指标。

208.获得模块1204还可用于将各个测试模式按照敏感度从高到低的顺序排序,获得测试模式序列;获得测试模式序列中除排在首位之外的各个测试模式的特有失效芯片的数量,其中,各个测试模式的特有失效芯片为该测试模式测试得到而在测试模式序列中排在该测试模式前的测试模式没有测试得到的失效芯片。

209.获得模块1204还可用于:将各个测试模式的测试时长相加,获得多个测试模式的总测试时长;根据各个测试模式的测试时长、多个测试模式的总测试时长、以及各个测试模式的特有失效芯片的数量获得各个测试模式的模式时间减少增益指标。

210.获得模块1206还可用于获得多个芯片的总芯片数量;将各个测试模式按照敏感度从高到低的顺序排序,获得测试模式序列;根据测试模式序列中除排在首位之外的各个测试模式的特有失效芯片的数量和总芯片数量获得测试模式序列中除排在首位之外的各个测试模式的模式时间减少风险指标。

211.获得模块1206还可用于:将各个测试模式的测试时长相加,获得多个测试模式的总测试时长;根据各个测试模式的测试时长、多个测试模式的总测试时长、以及各个测试模式的特有失效芯片的数量获得各个测试模式的模式时间减少增益指标。

212.获得模块1206还可用于:对于各个测试模式,将测试得到的失效芯片的数量除以测试时长,获得该测试模式的敏感度指标;将各个测试模式按照敏感度从高到低的顺序排序,获得测试模式序列;获得测试模式序列中除排在首位之外的各个测试模式的特有失效芯片的数量,其中,各个测试模式的特有失效芯片为该测试模式测试得到而在测试模式序列中排在该测试模式前的测试模式没有测试得到的失效芯片。

213.获得模块1206还可用于:对于各个测试模式,将测试得到的失效芯片的数量除以测试时长,获得该测试模式的敏感度指标;将各个测试模式按照敏感度从高到低的顺序排序,获得测试模式序列;获得多个测试模式中敏感度指标最低的测试模式,作为目标测试模式

214.判断模块1206可用于基于各个测试模式的敏感度指标从多个测试模式中确定目标测试模式。

215.判断模块1206还可用于获得多个测试模式中敏感度指标最低的测试模式,作为目标测试模式。

216.判断模块1206还可用于若多个测试模式中敏感度指标最低的测试模式的特有失效芯片的数量符合第一预设条件,则将多个测试模式中敏感度指标最低的测试模式作为目标测试模式。

217.判断模块1206还可用于若多个测试模式中敏感度指标最低的测试模式的特有失效芯片的数量符合第一预设条件,并且多个测试模式中敏感度指标最低的测试模式的测试时长与特有失效芯片的数量的比值符合第二预设条件,则将多个测试模式中敏感度指标最低的测试模式作为目标测试模式。

218.判断模块1206还可用于若多个测试模式中敏感度指标最低的测试模式的特有失效芯片的数量符合第一预设条件,并且多个测试模式中敏感度指标最低的测试模式的模式时间减少增益指标符合第三预设条件,则将多个测试模式中敏感度指标最低的测试模式作为目标测试模式。

219.判断模块1206还可用于若多个测试模式中敏感度指标最低的测试模式的模式时间减少风险指标符合第四预设条件,则将多个测试模式中敏感度指标最低的测试模式作为目标测试模式。

220.判断模块1206还可用于若多个测试模式中敏感度指标最低的测试模式的模式时间减少风险指标符合第四预设条件,并且多个测试模式中敏感度指标最低的测试模式的测试时长与特有失效芯片的数量的比值符合第二预设条件,则将多个测试模式中敏感度指标最低的测试模式作为目标测试模式。

221.判断模块1206还可用于若多个测试模式中敏感度指标最低的测试模式的模式时间减少风险指标符合第四预设条件,并且多个测试模式中敏感度指标最低的测试模式的模式时间减少增益指标符合第三预设条件,则将多个测试模式中敏感度指标最低的测试模式作为目标测试模式。

222.判断模块1206还可用于根据各个测试模式的敏感度指标以及测试模式序列中除排在首位之外的各个测试模式的特有失效芯片的数量从多个测试模式中确定目标测试模式。

223.处理模块1208可用于对目标测试模式进行测试时长减少操作,获得更新的目标测试模式,以按照多个测试模式对多个芯片进行测试。

224.处理模块1208还可用于:基于目标测试模式的测试时间点和测试得到失效位元的时间点,确定目标测试模式中的无效数据拓扑,其中,在按照目标测试模式对多个芯片进行测试的过程中,按照无效数据拓扑进行测试的时间点没有得到失效位元;将目标测试模式中的无效数据拓扑删除,获得更新的目标测试模式。

225.处理模块1208还可用于:对于各个测试模式,将测试得到失效位元的时间点按照测试时间点进行归一化,获得失效位元时间比率;将目标测试模式的失效位元时间比率与多个测试模式中除目标测试模式之外的测试模式的失效位元时间比率进行比较,获得目标测试模式中的无效数据拓扑。

226.处理模块1208还可用于对目标测试模式进行测试时长减少操作,获得更新的目标测试模式,以将测试模式序列中的目标测试模式替换为更新的目标测试模式,获得更新的测试模式序列,并按照更新的测试模式序列对多个芯片进行测试。

227.本公开实施例提供的装置中的各个模块的具体实现可以参照上述方法中的内容,此处不再赘述。

228.图13示出本公开实施例中一种电子设备的结构示意图。需要说明的是,图13示出的设备仅以计算机系统为示例,不应对本公开实施例的功能和使用范围带来任何限制。

229.如图13所示,设备1300包括中央处理单元(cpu)1301,其可以根据存储在只读存储器(rom)1302中的程序或者从存储部分1106加载到随机访问存储器(ram)1303中的程序而执行各种适当的动作和处理。在ram 1303中,还存储有设备1300操作所需的各种程序和数据。cpu1301、rom 1302以及ram 1303通过总线1304彼此相连。输入/输出(i/o)接口1305也连接至总线1304。

230.以下部件连接至i/o接口1305:包括键盘、鼠标等的输入部分1306;包括诸如阴极射线管(crt)、液晶显示器(lcd)等以及扬声器等的输出部分1307;包括硬盘等的存储部分1106;以及包括诸如lan卡、调制解调器等的网络接口卡的通信部分1309。通信部分1309经

由诸如因特网的网络执行通信处理。驱动器1310也根据需要连接至i/o接口1305。可拆卸介质1311,诸如磁盘、光盘、磁光盘、半导体存储器等等,根据需要安装在驱动器1310上,以便于从其上读出的计算机程序根据需要被安装入存储部分1106。

231.特别地,根据本公开的实施例,上文参考流程图描述的过程可以被实现为计算机软件程序。例如,本公开的实施例包括一种计算机程序产品,其包括承载在计算机可读介质上的计算机程序,该计算机程序包含用于执行流程图所示的方法的程序代码。在这样的实施例中,该计算机程序可以通过通信部分1309从网络上被下载和安装,和/或从可拆卸介质1311被安装。在该计算机程序被中央处理单元(cpu)1301执行时,执行本公开的系统中限定的上述功能。

232.需要说明的是,本公开所示的计算机可读介质可以是计算机可读信号介质或者计算机可读存储介质或者是上述两者的任意组合。计算机可读存储介质例如可以是——但不限于——电、磁、光、电磁、红外线、或半导体的系统、装置或器件,或者任意以上的组合。计算机可读存储介质的更具体的例子可以包括但不限于:具有一个或多个导线的电连接、便携式计算机磁盘、硬盘、随机访问存储器(ram)、只读存储器(rom)、可擦式可编程只读存储器(eprom或闪存)、光纤、便携式紧凑磁盘只读存储器(cd-rom)、光存储器件、磁存储器件、或者上述的任意合适的组合。在本公开中,计算机可读存储介质可以是任何包含或存储程序的有形介质,该程序可以被指令执行系统、装置或者器件使用或者与其结合使用。而在本公开中,计算机可读的信号介质可以包括在基带中或者作为载波一部分传播的数据信号,其中承载了计算机可读的程序代码。这种传播的数据信号可以采用多种形式,包括但不限于电磁信号、光信号或上述的任意合适的组合。计算机可读的信号介质还可以是计算机可读存储介质以外的任何计算机可读介质,该计算机可读介质可以发送、传播或者传输用于由指令执行系统、装置或者器件使用或者与其结合使用的程序。计算机可读介质上包含的程序代码可以用任何适当的介质传输,包括但不限于:无线、电线、光缆、rf等等,或者上述的任意合适的组合。

233.附图中的流程图和框图,图示了按照本公开各种实施例的系统、方法和计算机程序产品的可能实现的体系架构、功能和操作。在这点上,流程图或框图中的每个方框可以代表一个模块、程序段、或代码的一部分,上述模块、程序段、或代码的一部分包含一个或多个用于实现规定的逻辑功能的可执行指令。也应当注意,在有些作为替换的实现中,方框中所标注的功能也可以以不同于附图中所标注的顺序发生。例如,两个接连地表示的方框实际上可以基本并行地执行,它们有时也可以按相反的顺序执行,这依所涉及的功能而定。也要注意的是,框图或流程图中的每个方框、以及框图或流程图中的方框的组合,可以用执行规定的功能或操作的专用的基于硬件的系统来实现,或者可以用专用硬件与计算机指令的组合来实现。

234.描述于本公开实施例中所涉及到的模块可以通过软件的方式实现,也可以通过硬件的方式来实现。所描述的模块也可以设置在处理器中,例如,可以描述为:一种处理器包括测试模块、获得模块、判断模块、处理模块、数据整合模块和状态分类模块。其中,这些模块的名称在某种情况下并不构成对该模块本身的限定,例如,判断模块还可以被描述为“基于各个测试模式的敏感度指标从多个测试模式中确定目标测试模式的模块”。

235.作为另一方面,本公开还提供了一种计算机可读介质,该计算机可读介质可以是

上述实施例中描述的设备中所包含的;也可以是单独存在,而未装配入该设备中。上述计算机可读介质承载有一个或者多个程序,当上述一个或者多个程序被一个该设备执行时,使得该设备包括:

236.分别按照多个测试模式中的各个测试模式对多个芯片进行测试,获得各个测试模式对应的测试参数,测试参数包括测试时间信息和失效芯片信息,测试时间信息包括测试时长,失效芯片信息包括测试得到的失效芯片的数量;对于各个测试模式,根据测试得到的失效芯片的数量和测试时长获得该测试模式的敏感度指标;基于各个测试模式的敏感度指标从多个测试模式中确定目标测试模式;对目标测试模式进行测试时长减少操作,获得更新的目标测试模式,以按照多个测试模式对多个芯片进行测试。

237.以上具体地示出和描述了本公开的示例性实施例。应可理解的是,本公开不限于这里描述的详细结构、设置方式或实现方法;相反,本公开意图涵盖包含在所附权利要求的精神和范围内的各种修改和等效设置。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1