处理器、获取信息的方法、单板及网络设备与流程

本技术涉及计算机,尤其涉及一种处理器、获取信息的方法、单板及网络设备。

背景技术:

1、处理器作为计算机系统中用于执行运算和控制的模块,其是否正常运行是影响计算机系统能否正常执行运算和控制的重要因素。因此,在处理器运行异常时,需要获取处理器的相关信息,以便分析处理器运行异常的原因。

技术实现思路

1、本技术提出一种处理器、获取信息的方法、单板及网络设备,用于获取处理器的相关信息,以便分析处理器运行异常的原因。

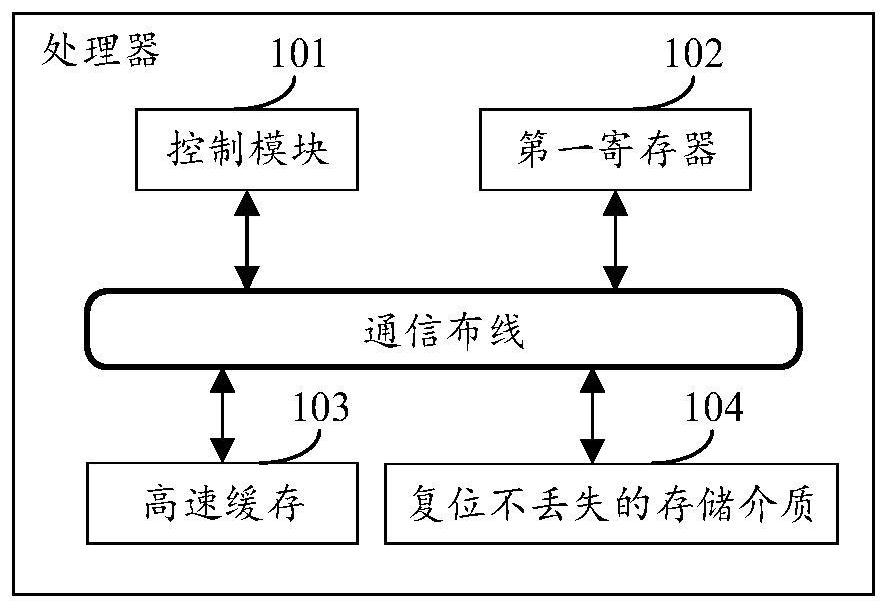

2、第一方面,提供了一种处理器,该处理器包括控制模块、第一寄存器和高速缓存,处理器与复位不丢失的存储介质通信连接。控制模块用于获取处理器运行异常生成的复位指示,基于复位指示,获取处理器的相关信息,该相关信息包括第一寄存器的寄存器信息或高速缓存存储的数据中的至少一种;将相关信息存储至复位不丢失的存储介质中。

3、在处理器运行异常时,处理器内部的控制模块能够基于复位指示获取处理器的相关信息。处理器无需依赖外部模块获取处理器的相关信息,也无需依赖于操作系统(operating system,os)响应中断信号执行中断响应程序,处理器获取相关信息的方式的可靠性较高。并且,在控制模块获取第一寄存器的寄存器信息以及高速缓存存储的数据的情况下,获取到的相关信息较为全面。从而在基于该相关信息分析处理器运行异常的原因的情况下,分析得到的原因的准确性较高。再有,由于控制模块可以为硬件模块,控制模块获取到复位指示后,能够快速获取处理器的相关信息,从而获取相关信息的效率较高。

4、在一种可能的实现方式中,处理器还包括第二寄存器。第二寄存器为处理器运行时使用的寄存器,第一寄存器用于记录第二寄存器的寄存器信息,第一寄存器为复位不丢失寄存器,复位指示用于指示处理器复位。控制模块用于基于复位指示,指示第一寄存器停止记录第二寄存器的寄存器信息,在处理器基于复位指示复位后获取第一寄存器的寄存器信息。通过使用复位不丢失的第一寄存器记录第二寄存器的寄存器信息,在处理器复位后,第二寄存器的寄存器信息可以被保留在第一寄存器中,从而能够基于获取到的第一寄存器的寄存器信息分析处理器运行异常的原因。通过使用第一寄存器保留第二寄存器的寄存器信息,保留第二寄存器的寄存器信息的方式的可靠性较高。

5、在一种可能的实现方式中,第二寄存器包括程序计数器(program counter,pc)、栈指针(stack pointer,sp)、帧指针(frame pointer,fp)、控制寄存器(controlregister,cr)或连接寄存器(link register,lr)中的至少一种。第二寄存器的类型较为丰富灵活,处理器能够保留多种类型的寄存器的寄存器信息。

6、在一种可能的实现方式中,处理器具有复位管脚,复位管脚用于生成复位指示,向控制模块传输复位指示。通过设置用于生成复位指示的复位管脚,处理器生成复位指示的方式较为简便。

7、在一种可能的实现方式中,控制模块与复位模块通信连接,复位模块用于向控制模块发送复位指示。控制模块还可以通过接收复位模块发送的复位指示实现获取复位指示,处理器获取复位指示的方式较为灵活。

8、在一种可能的实现方式中,复位不丢失的存储介质包括处理器内部的复位不丢失的内存、处理器内部的非易失存储介质、处理器外部的复位不丢失的内存或者处理器外部的非易失存储介质中的至少一种。复位不丢失的存储介质的类型较为灵活,从而,处理器的架构可以较为灵活多样,控制模块能够将处理器的相关信息存储值复位不丢失的存储介质中即可。

9、在一种可能的实现方式中,控制模块,还用于在处理器复位后,从复位不丢失的存储介质中获取该相关信息,基于该相关信息生成运行异常记录。通过生成运行异常记录,能够得到处理器运行异常的原因。并且,在该相关信息包括第一寄存器的寄存器信息和高速缓存存储的数据的情况下,分析得到的原因的准确性较高。

10、第二方面,提供了一种获取信息的方法,该方法应用于处理器,处理器包括控制模块、第一寄存器和高速缓存,处理器与复位不丢失的存储介质通信连接,该方法包括:控制模块获取处理器运行异常生成的复位指示,基于复位指示,获取处理器的相关信息,该相关信息包括第一寄存器的寄存器信息或高速缓存存储的数据中的至少一种;将该相关信息存储至复位不丢失的存储介质中。

11、在一种可能的实现方式中,处理器还包括第二寄存器,第二寄存器为处理器运行时使用的寄存器,第一寄存器用于记录第二寄存器的寄存器信息,第一寄存器为复位不丢失寄存器,复位指示用于指示处理器复位;基于复位指示,获取处理器的相关信息,包括:基于复位指示,指示第一寄存器停止记录第二寄存器的寄存器信息;在处理器基于复位指示复位后,获取第一寄存器的寄存器信息。

12、在一种可能的实现方式中,第二寄存器包括pc、sp、fp、cr或lr中的至少一种。

13、在一种可能的实现方式中,处理器具有复位管脚,该方法还包括:处理器通过复位管脚生成复位指示,复位管脚向控制模块传输复位指示;获取复位指示,包括:接收复位指示。

14、在一种可能的实现方式中,控制模块与复位模块通信连接,复位模块用于向控制模块发送复位指示;获取复位指示,包括:接收复位模块发送的复位指示。

15、在一种可能的实现方式中,复位不丢失的存储介质包括处理器内部的复位不丢失的内存、处理器内部的非易失存储介质、处理器外部的复位不丢失的内存或者处理器外部的非易失存储介质中的至少一种。

16、在一种可能的实现方式中,该方法还包括:在处理器复位后,控制模块从复位不丢失的存储介质中获取该相关信息,基于该相关信息生成运行异常记录。

17、第三方面,提供了一种单板,该单板包括上述第一方面中任一的处理器,以及与处理器通信连接的复位不丢失的存储介质。

18、在一种可能的实现方式中,该单板还包括复位模块,复位模块与处理器中的控制模块通信连接,复位模块用于向控制模块发送复位指示。

19、第四方面,提供了一种网络设备,该网络设备包括至少一个上述第一方面中任一的处理器,以及与处理器通信连接的复位不丢失的存储介质。

20、在一种可能的实现方式中,该网络设备还包括复位模块,复位模块与处理器中的控制模块通信连接,复位模块用于向控制模块发送复位指示。

21、第五方面,提供了一种网络设备,该网络设备包括至少一个上述第三方面中任一的单板。

22、第六方面,提供了一种芯片,该芯片包括至少一个上述第一方面中任一的处理器,以及与处理器通信连接的复位不丢失的存储介质。

23、在一种可能的实现方式中,该芯片还包括复位模块,复位模块与处理器中的控制模块通信连接,复位模块用于向控制模块发送复位指示。

24、在一种可能的实现方式中,该芯片还包括:输入接口、输出接口和存储器,该存储器包括上述复位不丢失的存储介质,输入接口、输出接口、处理器以及存储器之间通过内部连接通路相连。

25、应当理解的是,本技术的第二方面至第六方面的技术方案及对应的可能的实现方式所取得的有益效果可以参见上述第一方面及其对应的可能的实现方式的技术效果,此处不再赘述。

- 还没有人留言评论。精彩留言会获得点赞!