一种面向存内计算系统的加密方法

1.本发明涉及基于存内计算架构的神经网络加速器,具体涉及一种面向存内计算系统的加密方法。

背景技术:

2.随着信息技术的蓬勃发展,人类社会已经步入“数据爆炸”的时代,每年指数式增长的数据量为数据的处理和计算带来了空前的压力。传统冯诺依曼计算架构由于其存算分离的架构特点,数据在存储单元和计算单元之间的传输将引起大量的功耗和能耗的浪费,在如今信息社会乃至智能社会伴随庞大数据量的背景下,这一问题将变得越来越严重。

3.研究者们受人脑运算模式启发,提出了神经网络(neural network)计算架构,以神经元-突触-神经元的连接方式为基础,构建存算一体、高度并行的分布式计算网络,在提高了对复杂数据的处理效率的同时可避免传统冯诺依曼计算架构中“内存墙”引起的功耗和能耗问题。经典的人工神经网络(artificial neural network)中,输入特性向量和权重矩阵进行向量矩阵点乘产生输出向量,再通过激活函数得到输出的激活值向量,其中的主导运算操作时是乘累加操作。目前,人工神经网络在图像识别、自然语言处理、自动驾驶等应用中已表现出超越传统通用计算单元的计算效率。

4.人工神经网络架构最终要实现网络整体的硬件化,才能完全摆脱“内存墙”瓶颈的限制。基于非易失存储器件(non-volatile memory,nvm)如阻变存储器件、相变存储器件等,构建的存内计算架构(computing-in-memory,cim)能够加速人工神经网络中主导的乘累加运算,提升计算的能效。然而存储在非易失器件中的神经网络权重参数信息容易被直接读出并复制,面临潜在的安全问题,比如知识产权(ip)泄露问题和对抗性攻击问题。使用特定用户的授权密钥来加密存内计算系统对于边缘端机器学习的安全性至关重要。为了在用于存内矩阵乘加运算的非易失存储器阵列中加入加密功能,往往需要先将存储在阵列中的已加密的权重参数读出,随后通过阵列外围的解密电路解密来获得原始权重参数,再在外围数字电路中进行矩阵乘加运算,牺牲了基于非易失器件的存内计算的并行度优势,且要引入额外的硬件开销。

技术实现要素:

5.针对以上现有技术中存在的问题,本发明提出了一种面向存内计算系统的加密方法;与现有的具备加密功能的存内计算系统相比,本发明在实现原位的密文权重解密和乘加运算的前提下,可以显著降低硬件开销。

6.本发明提供的技术内容如下:

7.一种面向存内计算系统的加密方法,其特征在于,以带有栅存储层的具备双极输运特性的场效应晶体管器件(简称:栅存储双极场效应晶体管)作为密文权重存储单元构成加密存内计算阵列,在计算阶段,神经网络的输入与密钥进行xor操作得到中间信号,当中间信号与栅存储双极场效应晶体管存储的密文权重相同时,栅存储双极场效应晶体管输出

高电流ih,实现xnor加密运算。

8.所述加密存内计算阵列中,每行栅存储双极场效应晶体管的栅端连接在字线wl上,每列栅存储双极场效应晶体管的源端连接在位线bl上,在计算阶段,每列栅存储双极场效应晶体管漏端连接工作电压,横向的字线wl、纵向的位线bl、神经网络的输入xi和每一行共用的密钥位keyi作用于xor逻辑门,输出的中间信号x

wl_i

连接在阵列的字线wl上。

9.所述神经网络的输入数值xi的“+1”映射为逻辑电平高,

“‑

1”映射为逻辑电平低;在编程阶段,原始权重w

i,j

与用户授权密钥keyi做xor加密运算得到的密文权重w

e_i,j

被写入到栅存储双极场效应晶体管阵列中;密文权重

“‑

1”映射为栅存储双极场效应晶体管编程到高阈值态,“+1”映射为栅存储双极场效应晶体管编程到低阈值态。

10.本发明利用带有栅存储层的具备双极输运特性的场效应晶体管器件(栅存储双极场效应晶体管)作为密文权重存储单元,在单个晶体管单元上能实现xnor操作;栅存储双极场效应晶体管的结构为在具有双极沟道输运特性的场效应晶体管的栅叠层中增加栅存储层,或替换其栅介质层为栅存储层,器件具有栅端,源端,和漏端。在做存内计算时,栅端作为输入端,接收代表中间输入信号x

wl_i

的电压信号,源端和漏端置为固定电压,沟道电流代表输入和权重的乘法结果。本发明的栅存储双极场效应晶体管具有以下特性:在栅端施加编程电压脉冲,可以调节栅存储双极场效应晶体管器件的阈值电压;在栅端施加较低幅度的非破坏性读出电压时,能作为栅控沟道器件;该器件的沟道输运具备双极特性,在非破坏读出时,器件的转移特性曲线表现出非单调性,存在使得电流最低时对应的栅压(v

off

),且转移曲线关于v

off

表现出一定对称性;栅叠层非易失的栅存储机制通过调节器件的阈值电压,从而调节v

off

,存储不同的密文权重状态。当存储的密文权重状态(w

e_i,j

)和栅端的输入信号状态(x

wl_i

)匹配时,沟道才处于低电导状态,在单个晶体管上实现线性不可分的xnor操作。

11.本发明双极场效应晶体管器件的栅存储层可以采用浮栅(floating-gate)存储机制、电荷陷阱型(charge trapping)浮栅存储机制、铁电栅存储机制;本发明双极场效应晶体管器件的栅控双极沟道输运特性可以采用隧穿场效应晶体管(tunnel fet,tfet)的栅控反偏p-i-n结构的带带隧穿机制、具有肖特基源漏的栅控肖特基势垒源漏场效应晶体管(schottky barrier mosfet,sb-mosfet)机制、具有双极输运特性的二维材料沟道如石墨烯和碳纳米管沟道、和具有双极输运特性的氧化物沟道材料如sno。

12.本发明的面向存内计算系统的加密方法的有益效果及相应原理:

13.1、本发明的面向存内计算系统的加密方法在算法层将经典的xor运算加密方式用于加密神经网络权重参数,利用xor/xnor算子本征的结合律将密文权重解密过程融入到基于xnor的乘加运算中,将存内计算的乘加运算操作简化为直接在密文权重上进行xnor操作,从而避免显式的密文权重显式解密的过程。

14.2、本发明的面向存内计算系统的加密方法在器件层结合带有栅存储层的具备双极输运特性的场效应晶体管(栅存储双极场效应晶体管),利用非易失的栅存储机制实现密文权重的存储,利用三端结构的可控双极输运特性实现输入和密文权重的xnor操作,仅需一个器件即可实现在密文权重上的原位解密乘法,所构成的阵列能实现带有加密功能的存内计算系统。相比于基于传统cmos的方案或rram的方案显著降低硬件代价。

附图说明

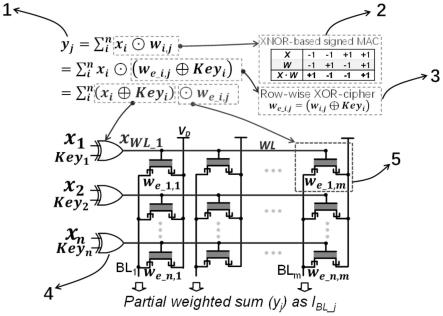

15.图1为本发明面向存内计算系统的加密方法的阵列示意图;

16.图2为本发明带有栅存储层的具备双极输运特性的场效应晶体管器件(栅存储双极场效应晶体管)的实施例的示意图;

17.图中:

18.1——面向存内计算系统的加密方法的算法层的示意图;

19.2——基于xnor的有符号乘法;

20.3——基于xor加密方法的逐行权重加密;

21.4——xor逻辑门;

22.5——带有栅存储层的具备双极输运特性的场效应晶体管器件(栅存储双极场效应晶体管);

23.6——带有栅存储机制的栅叠层,如浮栅(floating-gate)存储栅叠层、电荷陷阱型(charge trapping)浮栅存储栅叠层、铁电栅存储层;

24.7——具备双极输运特性的场效应晶体管,如隧穿场效应晶体管(tunnel fet,tfet),肖特基势垒源漏场效应晶体管(schottky barrier mosfet,sb-mosfet),石墨烯沟道场效应晶体管、碳纳米管沟道场效应晶体管、氧化锡(sno)沟道薄膜场效应晶体管等;

25.8——带有栅存储层的具备双极输运特性的场效应晶体管器件(栅存储双极场效应晶体管);

26.9——栅存储层调制的带有双极效应的转移曲线(i

d-vg)示意图。将栅存储层编程到不同状态,栅存储双极场效应晶体管具有不同的阈值电压,体现为非破坏读出的转移曲线沿栅压(vg)方向平移;双极效应体现为转移曲线为非单调的,且表现出一定的对称性。

具体实施方式

27.下面结合附图,通过具体实施例,进一步阐述本发明。

28.本实施例采用hf

0.5

zr

0.5

o2铁电层材料作为带有栅存储层的具备双极输运特性的场效应晶体管器件的栅存储层,采用栅控反偏p-i-n结构的隧穿场效应晶体管实现双极电流输运机制,所构成的栅存储双极场效应晶体管称为铁电隧穿场效应晶体管(ferroelectric tunnel fet,fetfet)。

29.如图1所示,本实例是基于fetfet的面向存内计算的加密方法的阵列电路实现,包括fefet器件构成的阵列,横向的字线(word-line,wl),纵向的位线(bit-line,bl),两输入xor逻辑门;神经网络的输入(xi)和每一行共用的密钥位(keyi)作用于xor逻辑门,

[0030][0031][0032]

公式(1)为基于xor逻辑的权重加密方法中原始权重和密文权重的关系表达式

[0033]

公式(2)为带有隐式解密过程的基于xnor的乘加运算,公式中:

[0034]

——异或运算,xor

[0035]

⊙

——同或运算,xnor

[0036]wi,j

——神经网络的原始权重参数

[0037]we_i,j

——原始权重经过加密得到的密文权重参数

[0038]

keyi——权重矩阵每一行共用的授权密钥位

[0039]

xi——神经网络的输入向量的各个位

[0040]

n——神经网络输入向量的维度

[0041]

x

wl_i

——神经网络输入与授权进行xor操作后作用在字线上的信号

[0042]

yj——输入向量与权重矩阵中一列的乘加运算部分和

[0043]

输出的中间信号(x

wl_i

)连接在阵列wl上;每行fetfet器件的栅端连接在wl上,每列fetfet的源端连接在bl上,计算时每列fetfet器件漏端连接工作电压;神经网络的输入数值(xi)的“+1”映射为逻辑电平高,

“‑

1”映射为逻辑电平低;在编程阶段,原始权重(w

i,j

)与用户授权密钥(keyi)做xor加密运算得到的密文权重(w

e_i,j

)被写入到fetfet阵列中;如图2所示,密文权重

“‑

1”映射为fetfet编程到高阈值态,“+1”映射为fetfet编程到低阈值态;在做加密神经网络运算时,仅当wl上的中间信号x

wl_i

与密文权重w

e_i,j

相同时,对应fetfet输出高电流ih,实现了xnor运算;电流在bl上自然地加和得到部分和;当运算时采用的密钥位不是授权密钥,则计算结果出错,从而导致神经网络的推断结果错误,实现了用户授权密钥加密的存内计算。

[0044]

以本实施例说明本发明的有益效果:

[0045]

1、对于基于fetfet的面向存内计算的加密方法的阵列电路,将经典的xor运算加密方式用于加密神经网络权重参数,利用xor/xnor算子本征的结合律将密文权重解密过程融入到基于xnor的乘加运算中,将存内计算的乘加运算操作简化为直接在密文权重上进行xnor操作,从而避免了显式的密文权重显式解密的过程。相比于传统实现方式,显著降低了硬件开销和计算复杂度,无需显式的解密过程,省去阵列外围的解密电路和乘加运算电路。

[0046]

2、对于基于fetfet的密文权重单元,在编程阶段,给fetfet栅端施加较高幅值的编程电压脉冲,使得铁电层分压大于其矫顽电压,铁电极化翻转,实现密文权重的存储;在运算阶段,fetfet栅端输入是与xi和keyi相关的非破坏性读出电压v

wl_i

,v

wl_i

与密文权重实现局部的基于xnor的有符号乘法结果,体现为沟道电流的高低。仅需要一个晶体管即可实现原位解密的局域xnor操作。相比于传统cmos实现方案,显著降低硬件开销,无需互补的密文权重存储和互补的输入。

[0047]

最后需要注意的是,公布实施例的目的在于帮助进一步理解本发明,但是本领域的技术人员可以理解:在不脱离本发明及所附的权利要求的精神和范围内,各种替换和修改都是可能的。因此,本发明不应局限于实施例所公开的内容,本发明要求保护的范围以权利要求书界定的范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1