一种计算机架构及控制方法与流程

1.本发明属于计算机架构技术领域,具体涉及一种计算机架构及控制方法。

背景技术:

2.目前在一些设备的控制计算机的应用环境下,对计算机本身的型号和扩展性都提出了相应的要求,而目前对于计算机的各类芯片的生产资源相对有限,技术和规模都无法满足装备的发展需求型号提及庞大和扩展性差使得在每次的更新中,会造成设备的资源浪费或者给设备的更新提出挑战。因此,如何缩减计算机中的半导体规格需求,加速设备更新周期和增强可扩展性是目前亟待解决的问题。

技术实现要素:

3.本发明涉及一种计算机架构以及控制方法,具体地指一种基于ip软核设计的计算机结构和控制方法,具有多种总线接口,实现数据通信及信号控制的设备。

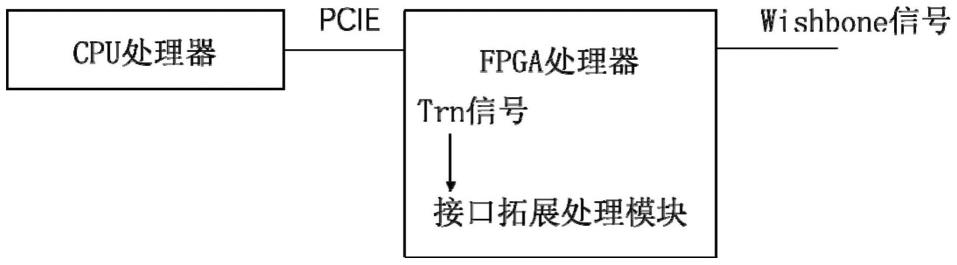

4.本发明公开了一种计算机架构,其特征在于,所述计算机架构包括:cpu处理器、fpga处理器,所述cpu处理器及fpga处理器所述通过pcie x1总线进行互联通信;

5.所述fpga处理器中包括有基于wishbone总线的接口扩展处理模块;

6.所述fpga处理器将所述cpu处理器发送的pcie信号转换成数据链路层的trn信号;

7.所述接口扩展处理模块将所述trn信号转换成wishbone信号,通过所述接口扩展处理模块中的wishbone总线连接到所述fpga处理器内部扩展的外设接口总线,以此方式,通过fpga处理器实现端口的拓展。

8.进一步地,所述接口扩展处理模块包括wishbone总线接口模块、数据发送模块、数据接收模块,所述wishbone总线接口模块和数据发送模块之间,所述wishbone总线接口模块和数据接收模块之间都设置有fifo队列模块。

9.进一步地,所述端口包括同步rs422接口、异步rs422接口和rs485接口。

10.进一步地,所述cpu处理器型号为ls3a3000,所述fpga处理器型号为jfm7k325t;

11.进一步地,所述fpga处理器与所述外设接口之间的协议为ttl协议。

12.本发明还公开了一种计算机架构的控制方法,其特征在于,包括如下步骤:

13.fpga处理器接收所述cpu处理器的pcie信号;

14.所述fpga处理器将所述pcie信号转换成数据链路层的trn信号;

15.所述fpga处理器将所述trn信号转换成wishbone信号;

16.所述fpga处理器内部扩展的外设接口总线接收所述wishbone信号与端口进行交互。

17.进一步地,所述wishbone信号通过数据发送模块和数据接收模块与所述端口交互,之间设置有fifo队列模块。

18.进一步地,所述端口包括同步rs422接口、异步rs422接口和rs485接口。

19.进一步地,所述cpu处理器型号为ls3a3000,所述fpga处理器型号为jfm7k325t。

20.进一步地,所述fpga处理器与所述端口之间的协议为ttl协议。

21.总体而言,通过本发明构思的以上技术方案与现有技术相比,能够取得下列有益效果:

22.在fpga内部设计实现基于wishbone总线的uart ip核设计,替代串口控制器的硬件功能,能够显著减小计算机的体积,提高接口的可扩展性。

附图说明

23.图1为按照本发明实现的计算机架构的基本组成结构示意图;

24.图2为按照本发明实现的计算机架构中的ip软核组成结构示意图;

25.图3为按照本发明实现的计算机架构的其中一种具体实施方式的组成结构示意图;

26.图4为按照本发明实现的计算机架构的控制方法的具体流程示意图。

具体实施方式

27.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。此外,下面所描述的本发明各个实施方式中所涉及到的技术特征只要彼此之间未构成冲突就可以相互组合。

28.为实现上述目的,按照本发明的一个方面,如本发明的目的是提供一种基于ip软核设计、具有多种总线接口的计算机架构,从根本上减小计算机的体积,提高计算机系统的可拓展性。

29.如图1中所示,本发明首先提出了一种计算机架构,包括cpu处理器、fpga处理器,两者通过pcie x1总线进行互联通信,其中fpga处理器中包括有基于wishbone总线的uart ip核处理模块(接口扩展模块的其中一种实施方式),其中uart ip核处理模块包括wishbone总线接口模块、数据发送模块、数据接收模块,之间设置有fifo队列模块。

30.其中fpga处理器将cpu处理器发送的pcie的信号直接转换成数据链路层的trn信号;

31.其中基于wishbone总线的uart ip核处理模块将trn信号转换成常用的内部信号wishbone总线,通过wishbone总线连接到内部扩展的外设接口总线,以此方式,通过fpga处理器实现接口的拓展。

32.其中,在上述的计算机架构的硬件组成系统中,还包括有桥片、内存、接口电路、存储单元、时钟、复位电路和电源电路组成。其中在本发明的其中一种实施方式中关键硬件cpu芯片、桥片芯片、内存芯片、fpga处理器、存储单元等均采用自主可控的国产化芯片设计实现。总之,cpu与fpga两者通过pcie x1总线进行互联通信,其中外设接口,包括同步rs422接口、异步rs422接口和rs485接口均通过fpga进行扩展实现。在fpga内部设计实现基于wishbone总线的uart ip核设计,替代串口控制器的硬件功能。

33.图3为按照本发明的其中一种实施方式中实现的计算机架构的组成示意图,cpu处理器采用国产cpu龙芯ls3a3000,桥片搭配龙芯ls7a1000,fpga处理器选用国产复旦微的jfm7k325t,cpu与fpga两者通过pcie x1总线进行互联通信,其中外设接口,包括同步rs422

总线接口、异步rs422总线接口和rs485总线接口均通过fpga进行扩展。

34.其中cpu处理器采用国产cpu龙芯ls3a3000,桥片搭配龙芯ls7a1000,fpga处理器选用国产复旦微的jfm7k325t,cpu处理器和fpga处理器之间传输pcie信号,其中fpga处理器通过spi协议连接闪存jfm25f128,fpga处理器通过ttl协议扩展各类接口,其中包括有同步rs422、异步rs422以及rs485,处理器和接口之间还设置有隔离收发器,其中桥片ls7a1000还通过网络变压器接多个lan网络,通过msata接ssd盘,通过数字模拟转换器gm7123c接vga的接口,桥片ls7a1000通过spi协议连接闪存gd25q32;cpu处理器通过spi协议连接闪存gd25q32,通过sm3232闪存器提供rs232的接口,cpu处理器还连接动态缓存存储器ddr3,软件调试接口ejtag。

35.其中作为本发明uart ip核内部的ip软核流程设计:通过fpga厂家的代码生成器的工具,生成endpoint block plus for pci express的相关设计,这样就使得fpga处理器能够将cpu发送的pcie的信号直接转换成数据链路层的trn信号,再解析trn信号就能完成pcie的转换,考虑计算机架构的通用性,将trn信号转换成常用的内部信号wishbone总线,通过wishbone总线连接到内部扩展的外设接口总线,以此方式,完成接口的扩展,减少外围串口控制器和外围接口的使用,从而使得计算机设备能够小型化,并且显著提高设备的可拓展性。

36.而上述的fpga处理器所包含的uart ip核内部包括数据发送模块、数据接收模块和wishbone总线接口模块。总之,其中除了能够实现wishbone总线协议,uart ip核集成了uart的基本功能,具体包括:a)支持rs422协议和wishbone总线规范;b)全双工独立收发功能;c)接收通道进行奇偶校验,溢出,产生可选中断;d)内置支持接收和发送的16byte fifo;e)发送“空”产生可选中断,接收“满”产生可选中断。

37.如图4中所示,本发明还公开了一种计算机架构的控制方法,其特征在于,包括如下步骤:

38.fpga处理器接收cpu处理器的pcie信号;

39.fpga处理器将pcie信号转换成数据链路层的trn信号;

40.fpga处理器将trn信号转换成wishbone信号;

41.fpga处理器内部扩展的外设接口总线接收wishbone信号与端口进行交互。

42.对于前述的各方法实施例,为了简单描述,故将其都表述为一系列的动作组合,但是本领域技术人员应该知悉,本技术并不受所描述的动作顺序的限制,因为依据本技术,某些步骤可以采用其他顺序或者同时进行。其次,本领域技术人员也应该知悉,说明书中所描述的实施例均属于优选实施例,所涉及的动作和模块并不一定是本技术所必须的。

43.在上述实施例中,对各个实施例的描述都各有侧重,某个实施例中没有详述的部分,可以参见其他实施例的相关描述。

44.在本技术所提供的几个实施例中,应该理解到,所揭露的装置,可通过其它的方式实现。例如,以上所描述的装置实施例仅仅是示意性的,例如所述单元的划分,仅仅为一种逻辑功能划分,实际实现时可以有另外的划分方式,例如多个单元或组件可以结合或者可以集成到另一个系统,或一些特征可以忽略,或不执行。另一点,所显示或讨论的相互之间的耦合或直接耦合或通信连接可以是通过一些服务接口,装置或单元的间接耦合或通信连接,可以是电性或其它的形式。

45.所述作为分离部件说明的单元可以是或者也可以不是物理上分开的,作为单元显示的部件可以是或者也可以不是物理单元,即可以位于一个地方,或者也可以分布到多个网络单元上。可以根据实际的需要选择其中的部分或者全部单元来实现本实施例方案的目的。

46.另外,在本技术各个实施例中的各功能单元可以集成在一个处理单元中,也可以是各个单元单独物理存在,也可以两个或两个以上单元集成在一个单元中。上述集成的单元既可以采用硬件的形式实现,也可以采用软件功能单元的形式实现。

47.所述集成的单元如果以软件功能单元的形式实现并作为独立的产品销售或使用时,可以存储在一个计算机可读取存储器中。基于这样的理解,本技术的技术方案本质上或者说对现有技术做出贡献的部分或者该技术方案的全部或部分可以以软件产品的形式体现出来,该计算机软件产品存储在一个存储器中,包括若干指令用以使得一台计算机设备(可为个人计算机、服务器或者网络设备等)执行本技术各个实施例所述方法的全部或部分步骤。而前述的存储器包括:u盘、只读存储器(read-only memory,rom)、随机存取存储器(random access memory,ram)、移动硬盘、磁碟或者光盘等各种可以存储程序代码的介质。

48.本领域普通技术人员可以理解上述实施例的各种方法中的全部或部分步骤是可以通进程序来指令相关的硬件来完成,该程序可以存储于一计算机可读存储器中,存储器可以包括:闪存盘、只读存储器(read-only memory,rom)、随机存取器(random access memory,ram)、磁盘或光盘等。

49.以上所述者,仅为本公开的示例性实施例,不能以此限定本公开的范围。即但凡依本公开教导所作的等效变化与修饰,皆仍属本公开涵盖的范围内。本领域技术人员在考虑说明书及实践这里的公开后,将容易想到本公开的其实施方案。本技术旨在涵盖本公开的任何变型、用途或者适应性变化,这些变型、用途或者适应性变化遵循本公开的一般性原理并包括本公开未记载的本技术领域中的公知常识或惯用技术手段。说明书和实施例仅被视为示例性的,本公开的范围和精神由权利要求限定。

50.本说明书中所描述的内容仅仅是对本发明所作的举例说明,本发明所属技术领域的技术人员可以对所描述的具体实施例做各种各样的修改或补充或采用类似的方式替代,只要不偏离本发明说明书的内容或者超越本权利要求书所定义的范围,均应属于本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1