高带宽内存测试方法、高带宽内存、电子设备和存储介质与流程

本发明涉及通讯,具体涉及高带宽内存测试方法、高带宽内存、电子设备和存储介质。

背景技术:

1、hbm(high bandwidth memory,高带宽内存)设备在较高的工作频率下,数据的传输如果受到数据通信链路上的噪声或者数据线之间的串扰等因素的干扰,很容易出现数据读写的错误。因此,需要在hbm设备刚出厂时或者在hbm设备所工作的温度、电压等环境因素发生改变时,对hbm的读写数据通路进行校验,保证hbm在高速读写数据的过程中数据的正确性。

2、目前,由于hbm dram在刚上电时内部为空没有数据,无法通过读数据完成对读数据通路的校验,因此,在对hbm的读写数据通路进行校验时,一般采用的方案是先向hbmdram写入数据后,通过读取该数据进行比对,完成对读数据通路的校验。但是,由于写数据通路没有经过校验,当最终读取出来的数据与写入的数据出现不匹配时,错误可能存在于写数据通路和/或读数据通路。因此,采用这种方案无法定位问题发生的位置,不能准确的对读数据通路进行检测和校验。

技术实现思路

1、本发明实施例提供高带宽内存测试方法、高带宽内存、电子设备和存储介质,可以对高带宽dram的读数据通道进行实时的检测,及时的发现读数据通道的错误并进行上报,保证整个系统运行的正确性和可靠性。

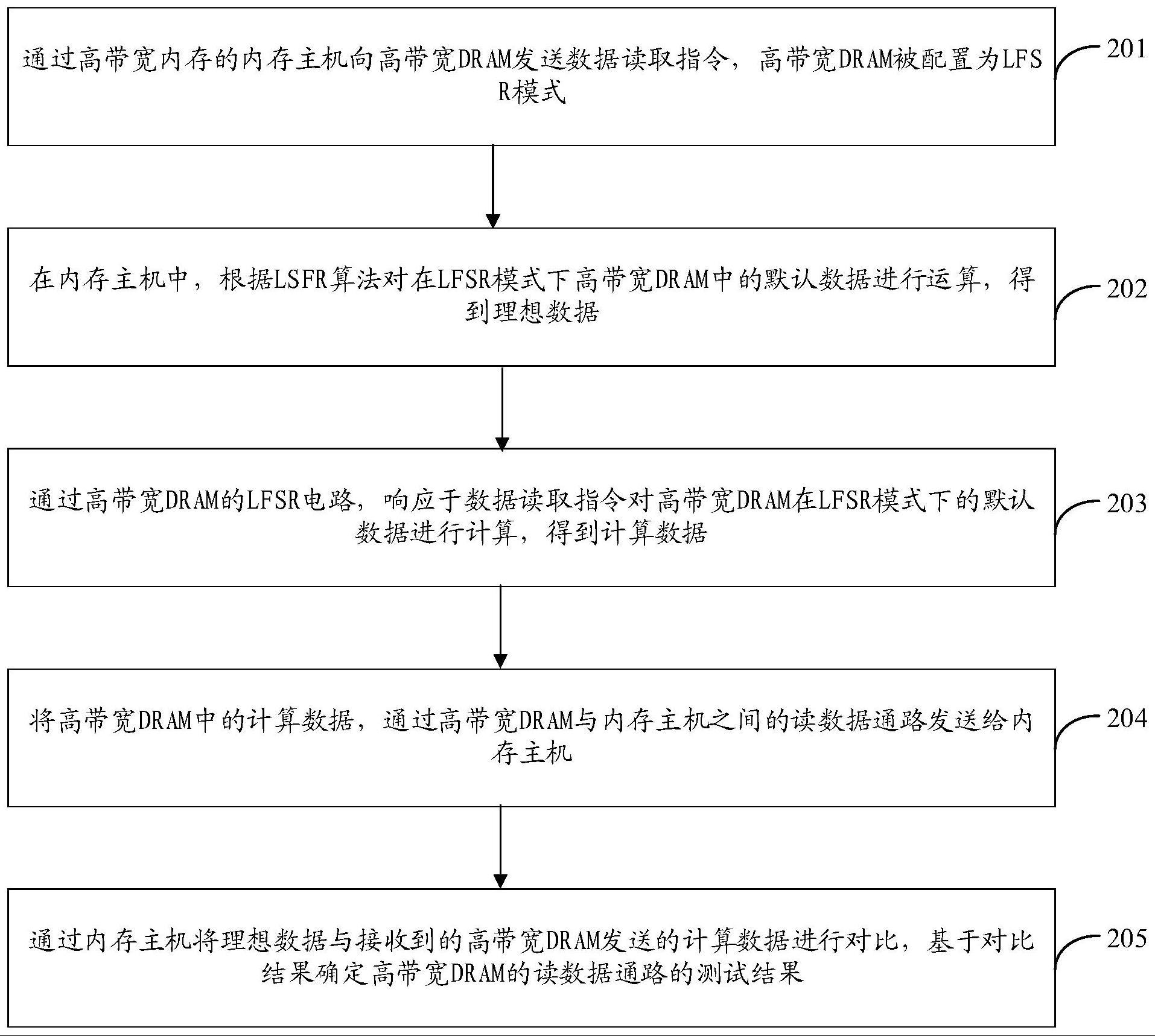

2、本发明实施例提供一种高带宽内存测试方法,应用于高带宽内存,所述高带宽内存包括内存主机和高带宽dram,所述方法包括:

3、通过所述高带宽内存的所述内存主机向所述高带宽dram发送数据读取指令,所述高带宽dram被配置为lfsr模式;

4、在所述内存主机中,根据lsfr算法对在所述lfsr模式下所述高带宽dram中的默认数据进行运算,得到理想数据;

5、通过所述高带宽dram的lfsr电路,响应于所述数据读取指令对所述高带宽dram在所述lfsr模式下的默认数据进行计算,得到计算数据;

6、将所述高带宽dram中的所述计算数据,通过所述高带宽dram与所述内存主机之间的读数据通路发送给所述内存主机;

7、通过所述内存主机将所述理想数据与接收到的所述高带宽dram发送的计算数据进行对比,基于对比结果确定所述高带宽dram的读数据通路的测试结果。

8、相应的,本发明实施例还提供一种高带宽内存,包括:

9、指令发送模块,用于通过所述高带宽内存的所述内存主机向所述高带宽dram发送数据读取指令,所述高带宽dram被配置为lfsr模式;

10、理想数据计算模块,用于在所述内存主机中,根据lsfr算法对在所述lfsr模式下所述高带宽dram中的默认数据进行运算,得到理想数据;

11、数据计算模块,用于通过所述高带宽dram的lfsr电路,响应于所述数据读取指令对所述高带宽dram在所述lfsr模式下的默认数据进行计算,得到计算数据;

12、数据读取模块,用于将所述高带宽dram中的所述计算数据,通过所述高带宽dram与所述内存主机之间的读数据通路发送给所述内存主机;

13、数据对比模块,用于通过所述内存主机将所述理想数据与接收到的所述高带宽dram发送的计算数据进行对比,基于对比结果确定所述高带宽dram的读数据通路的测试结果。

14、可选的,本发明实施例提供的高带宽内存测试装置还包括配置指令发送模块,用于通过所述内存主机向所述高带宽dram发送寄存器配置指令;

15、通过所述高带宽dram响应于所述寄存器配置指令,将所述高带宽dram中的寄存器配置为lfsr模式。

16、可选的,所述寄存器配置指令包括寄存器复位指令和模式配置指令,所述配置指令发送模块,用于通过所述高带宽dram响应于所述寄存器复位指令,将寄存器中的默认值复位为默认数据;

17、通过所述高带宽dram响应于所述模式配置指令,将所述寄存器配置为所述lfsr模式。

18、可选的,所述数据对比模块,用于通过所述内存主机将所述理想数据与接收到的所述高带宽dram发送的计算数据进行对比,得到当前的对比结果;

19、若所述当前的对比结果为对比成功,返回执行所述通过所述高带宽内存的所述内存主机向所述高带宽dram发送数据读取指令的步骤,直到对比成功的所述对比结果的数量满足预设的测试成功次数,确定所述高带宽dram的读数据通路的测试结果为读数据通路正确。

20、可选的,所述数据对比模块,用于通过所述内存主机将接收到的所述高带宽dram发送的计算数据中的上升沿数据、下降沿数据、高电平数据和低电平数据与所述理想数据中的上升沿数据、下降沿数据、高电平数据和低电平数据逐位进行对比;

21、若所述读取数据与所述理想数据的各位均相同,则当前的对比结果为对比成功。

22、可选的,本发明实施例提供的高带宽内存测试装置还包括错误上报模块,用于若所述当前的对比结果为对比失败,从所述读取数据中确定出于所述理想数据不同的错误数据位;

23、将所述错误数据位上报给预设的错误处理模块,以使得所述错误处理模块基于所述错位数据位进行错误处理。

24、可选的,所述指令发送模块,用于通过所述高带宽内存的所述内存主机的控制单元,控制所述内存主机中的读指令发送单元向所述高带宽dram发送数据读取指令;

25、所述理想数据计算模块,用于通过所述控制单元,控制所述内存主机中的lfsr数据计算单元对在所述lfsr模式下所述高带宽dram中的默认数据进行运算,得到理想数据;

26、所述数据对比模块,用于通过所述控制单元,控制所述内存主机中的读数据接收单元接收所述高带宽dram通过所述读数据通路发送的计算数据;

27、通过所述控制单元,控制所述读数据接收单元将所述理想数据与接收到的所述高带宽dram发送的计算数据进行对比,基于对比结果确定所述高带宽dram的读数据通路的测试结果。

28、可选的,本发明实施例提供的高带宽内存测试装置还包括写数据通路测试模块,用于当所述高带宽dram的读数据通路的测试结果为读数据通路正确时,通过所述内存主机向所述高带宽dram中写入写通道测试数据;

29、通过所述内存主机向所述高带宽dram发送测试数据读取指令;

30、将所述高带宽dram中的所述写通道测试数据,通过所述读数据通路发送给所述内存主机;

31、将接收到的所述高带宽dram发送的写通道测试数据与写入所述高带宽dram的写通道测试数据进行对比,基于对比结果确定所述高带宽dram的写数据通路的测试结果。

32、相应的,本发明实施例还提供一种电子设备,包括存储器和处理器;所述存储器存储有应用程序,所述处理器用于运行所述存储器内的应用程序,以执行本发明实施例所提供的任一种高带宽内存测试方法中的步骤。

33、相应的,本发明实施例还提供一种计算机可读存储介质,所述计算机可读存储介质存储有多条指令,所述指令适于处理器进行加载,以执行本发明实施例所提供的任一种高带宽内存测试方法中的步骤。

34、此外,本发明实施例还提供一种计算机程序产品,包括计算机程序或指令,所述计算机程序或指令被处理器执行时实现本发明实施例所提供的任一种高带宽内存测试方法中的步骤。

35、采用本发明实施例的方案,可以通过高带宽内存的内存主机向高带宽dram发送数据读取指令,该高带宽dram被配置为lfsr模式,在该内存主机中,根据lsfr算法对在该lfsr模式下该高带宽dram中的默认数据进行运算,得到理想数据,通过该高带宽dram的lfsr电路,响应于该数据读取指令对该高带宽dram在该lfsr模式下的默认数据进行计算,得到计算数据,将该高带宽dram中的该计算数据,通过该高带宽dram与该内存主机之间的读数据通路发送给该内存主机,通过该内存主机将该理想数据与接收到的该高带宽dram发送的计算数据进行对比,基于对比结果确定该高带宽dram的读数据通路的测试结果;由于在本发明实施例中,无需对高带宽dram通过写数据通路写入数据,而是通过直接读取高带宽dram在特定模式下的默认数据,并将读取到的读取数据与理想情况下可以读取到的理想数据进行对比,得到对于读数据通路的测试结果,因此,可以对高带宽dram的读数据通道进行实时的检测,及时的发现读数据通道的错误并进行上报,保证整个高带宽内存运行的正确性和可靠性。

- 还没有人留言评论。精彩留言会获得点赞!