非易失性存储器装置和数据擦除方法与流程

本公开总体上涉及半导体,更具体而言,涉及非易失性存储器装置和所述非易失性存储器装置的数据擦除方法。

背景技术:

1、最近,在电子装置中广泛使用了具有“垂直”(即,在三维(3d)中)堆叠的存储器单元的非易失性存储器。非易失性存储器装置通常可以包括多个垂直堆叠的级,例如由双堆叠工艺形成的顶部级和底部级。每个级可以包括多个垂直堆叠的存储器单元。为了在具有多个级的非易失性存储器装置中实现有效的读取、写入和擦除操作,每个级必须能够单独实现擦除操作。

2、此外,随着非易失性存储器装置的堆叠层的数量增大,沟道层底部结构的连接模式已经从传统选择性外延结构演进到横向连接模式或底部连接模式。通过在沟道层底部形成高度掺杂的半导体层(通常与沟道层具有相同类型的掺杂)作为连接结构,通过现有形成方法制造的非易失性存储器装置不适于大量的擦除操作。因此,引入栅极诱发的漏极泄露(gidl)以产生辅助主体偏置,以在每个级辅助擦除操作,从而实现非易失性存储器装置的数据擦除。

3、因此,期望提高非易失性存储器装置的级擦除操作和gidl擦除操作的效率。

技术实现思路

1、本公开中描述了三维(3d)存储器装置的实施方式。

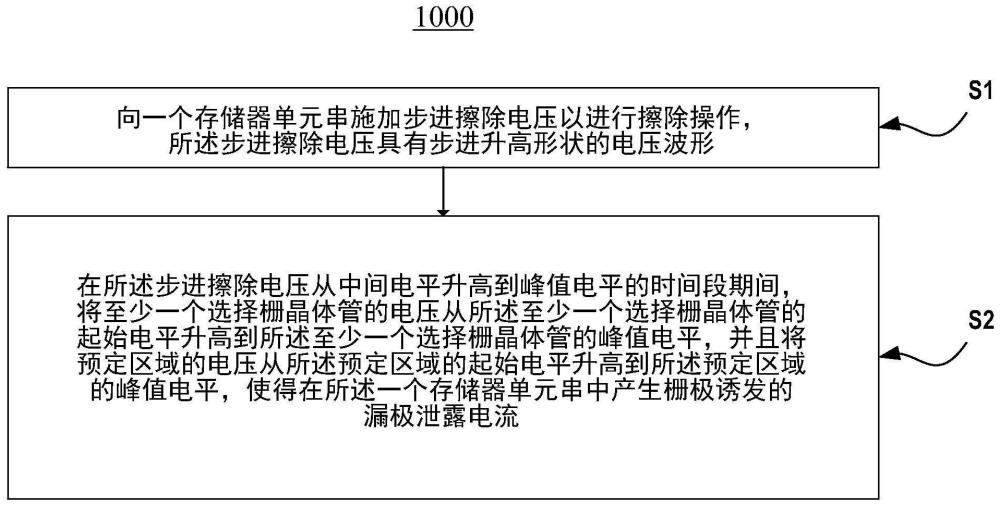

2、本公开的一个方面提供了一种用于非易失性存储器装置的数据擦除的方法。所述存储器包括多个存储器单元串,每个串包括串联连接的至少一个选择栅晶体管和多个存储器单元。所述方法包括向一个存储器单元串施加步进擦除电压进行擦除操作,所述步进擦除电压具有步进升高形状的电压波形。所述方法还包括:在所述步进擦除电压从所述步进擦除电压的中间电平升高到所述步进擦除电压的峰值电平的时间段期间,将所述至少一个选择栅晶体管的电压从所述至少一个选择栅晶体管的起始电平升高到所述至少一个选择栅晶体管的峰值电平,以及将预定区域的电压从所述预定区域的起始电平升高到所述预定区域的峰值电平,使得在一个存储器单元串中产生栅极诱发的漏极泄露电流。所述预定区域与所述至少一个选择栅晶体管相邻并且包括所述多个存储器单元中的至少一个。

3、在一些实施方式中,所述至少一个选择栅晶体管包括连接到位线的顶部选择栅(tsg)晶体管和/或连接到衬底中的阱掺杂区域的底部选择栅(bsg)晶体管,并且所述预定区域包括第一预定区域和第二预定区域,其中,所述第一预定区域与所述bsg晶体管相邻并且包括所述多个存储器单元中的至少一个,所述第二预定区域与所述tsg晶体管相邻并且包括所述多个存储器单元中的至少一个。

4、在一些实施方式中,升高所述至少一个选择栅晶体管的电压和升高所述预定区域的电压包括:在将所述至少一个选择栅晶体管的电压从所述至少一个选择栅晶体管的起始电平升高到所述至少一个选择栅晶体管的峰值电平的时间段期间,将所述预定区域的电压从所述预定区域的起始电平升高到所述预定区域的峰值电平。

5、在一些实施方式中,升高所述至少一个选择栅晶体管的电压和升高所述预定区域的电压包括:同时将所述至少一个选择栅晶体管的电压从所述至少一个选择栅晶体管的起始电平升高到所述至少一个选择栅晶体管的峰值电平以及将所述预定区域的电压从所述预定区域的起始电平升高到所述预定区域的峰值电平,其中,所述至少一个选择栅晶体管的峰值电平等于所述预定区域的峰值电平。

6、在一些实施方式中,升高所述至少一个选择栅晶体管的电压和升高所述预定区域的电压包括:在将所述至少一个选择栅晶体管的电压从所述至少一个选择栅晶体管的起始电平升高之后,将所述预定区域的电压从所述预定区域的起始电平升高。

7、在一些实施方式中,所述多个存储器单元包括至少一个虚设存储器单元;所述至少一个虚设存储器单元还包括位于所述bsg晶体管和所述阱掺杂区域之间的至少一个第一虚设存储器单元;并且所述第一预定区域与所述bsg晶体管相邻,并且包括所述至少一个虚设存储器单元,并且通过所述至少一个第一虚设存储器单元与所述衬底分隔开。

8、在一些实施方式中,所述方法还包括:将所述第一虚设存储器单元中的至少一个在所述擦除操作期间设置成浮置状态。

9、在一些实施方式中,所述方法还包括:向所述第一虚设存储器单元中的至少一个施加另一步进擦除电压。

10、在一些实施方式中,所述至少一个虚设存储器单元还包括与所述至少一个选择栅晶体管相邻的至少一个选择级虚设存储器单元。

11、在一些实施方式中,所述方法还包括:在所述步进擦除电压从所述中间电平升高到所述峰值电平的时间段期间,将所述至少一个选择级虚设存储器单元的电压从所述至少一个选择级虚设存储器单元的起始电平升高到所述至少一个选择级虚设存储器单元的峰值电平。

12、在一些实施方式中,所述方法还包括:在将所述至少一个选择栅晶体管的电压从所述至少一个选择栅晶体管的起始电平升高到所述至少一个选择栅晶体管的峰值电平的时间段期间,将所述至少一个选择级虚设存储器单元的电压从所述至少一个选择级虚设存储器单元的起始电平升高到所述至少一个选择级虚设存储器单元的峰值电平。

13、在一些实施方式中,所述方法还包括:同时将所述至少一个选择栅晶体管的电压从所述至少一个选择栅晶体管的起始电平升高到所述至少一个选择栅晶体管的峰值电平以及将所述至少一个选择级虚设存储器单元的电压从所述至少一个选择级虚设存储器单元的起始电平升高到所述至少一个选择级虚设存储器单元的峰值电平。

14、在一些实施方式中,所述方法还包括:在将所述至少一个选择栅晶体管的电压从所述至少一个选择栅晶体管的起始电平升高之后,将所述至少一个选择级虚设存储器单元的电压从所述至少一个选择级虚设存储器单元的起始电平升高。

15、在一些实施方式中,升高所述至少一个选择栅晶体管的电压和升高所述预定区域的电压包括:在将所述bsg晶体管的电压从所述bsg晶体管的起始电平升高到所述bsg晶体管的峰值电平的时间段期间,将所述第一预定区域的电压从所述第一预定区域的起始电平升高到所述第一预定区域的峰值电平;以及在将所述tsg晶体管的电压从所述tsg晶体管的起始电平升高到所述tsg晶体管的峰值电平的时间段期间,将所述第二预定区域的电压从所述第二预定区域的起始电平升高到所述第二预定区域的峰值电平。

16、在一些实施方式中,升高所述至少一个选择栅晶体管的电压和升高所述预定区域的电压包括:在将所述bsg晶体管的电压从所述bsg晶体管的起始电平升高之后,将所述第一预定区域的电压从所述第一预定区域的起始电平升高;以及同时将所述tsg晶体管的电压从所述tsg晶体管的起始电平升高到所述tsg晶体管的峰值电平以及将所述第二预定区域的电压从所述第二预定区域的起始电平升高到所述第二预定区域的峰值电平。

17、在一些实施方式中,升高所述至少一个选择栅晶体管的电压和升高所述预定区域的电压包括:同时将所述bsg晶体管的电压从所述bsg晶体管的起始电平升高到所述bsg晶体管的峰值电平以及将所述第一预定区域的电压从所述第一预定区域的起始电平升高到所述第一预定区域的峰值电平;以及在将所述tsg晶体管的电压从所述tsg晶体管的起始电平升高之后,将所述第二预定区域的电压从所述第二预定区域的起始电平升高。

18、在一些实施方式中,升高所述至少一个选择栅晶体管的电压和升高所述预定区域的电压包括:同时将所述bsg晶体管的电压从所述bsg晶体管的起始电平升高到所述bsg晶体管的峰值电平以及将所述第一预定区域的电压从所述第一预定区域的起始电平升高到所述第一预定区域的峰值电平;以及同时将所述tsg晶体管的电压从所述tsg晶体管的起始电平升高到所述tsg晶体管的峰值电平以及将所述第二预定区域的电压从所述第二预定区域的起始电平升高到所述第二预定区域的峰值电平。

19、在一些实施方式中,升高所述至少一个选择栅晶体管的电压和升高所述预定区域的电压包括:在将所述bsg晶体管的电压从所述bsg晶体管的起始电平升高之后,将所述第一预定区域的电压从所述第一预定区域的起始电平升高;以及在将所述tsg晶体管的电压从所述tsg晶体管的起始电平升高之后,将所述第二预定区域的电压从所述第二预定区域的起始电平升高。

20、本公开的另一方面提供了一种非易失性存储器装置,包括:形成于衬底的阱掺杂区域上的存储器阵列,包括多个块,其中每个块包括多个存储器单元串,每个存储器单元串包括多个串联连接到对应位线的多个存储器单元,并且每个块包括在垂直于所述衬底的方向上垂直堆叠的一个或多个级;以及耦接到所述存储器阵列的外围电路,所述外围电路被配置成控制对所述多个级的级选择,并且对所选择的级执行级擦除操作和上文描述的电平调节。

21、在一些实施方式中,所述存储器阵列是三维nand存储器阵列,所述非易失性存储器装置是三维nand存储器装置。

22、在一些实施方式中,每个块包括在垂直于所述衬底的方向上垂直堆叠的两个级。

23、在一些实施方式中,每个块包括在垂直于所述衬底的方向上垂直堆叠的三个或更多个级。

24、本公开的另一方面提供了一种存储器系统,包括:上述存储器装置;以及控制器,所述控制器耦接到所述存储器装置并且被配置成控制所述存储器装置以存储数据。

25、本公开的另一方面提供了一种电子装置,包括上述存储器装置。

26、本领域技术人员根据本公开的描述、权利要求和附图能够理解本公开的其他方面。

- 还没有人留言评论。精彩留言会获得点赞!