内存控制器和芯片的制作方法

1.本发明涉及芯片技术领域,尤其涉及一种内存控制器和芯片。

背景技术:

2.双通道内存交织技术,是指芯片支持同时访问两个内存,以此提升整体内存带宽,缓解芯片内存瓶颈问题。双通道内存交织技术的实现方法通常是,将总线上针对内存空间的传输,按照预先定义的内存颗粒度进行拆分,然后将拆分过后的传输同时投递到两个内存上,以此实现两个内存并行工作。其中,负责实现两个内存并行工作的组件,通常被称为双通道内存交织控制器,然而这类双通道内存交织控制器仅支持双通道的访问,这样便不利于芯片产品形态的灵活性。

技术实现要素:

3.本发明的目的旨在解决上述背景技术中的问题。为此,本发明第一个目的在于提出一种内存控制器,该内存控制器通过配置接口所输入的控制信号,确定读或写访问信号所需使用的传输通道是单通道还是双通道,并通过所需使用的传输通道对相应的内存进行访问,从而兼容了双通道访问内存和单通道访问内存,这样有利于芯片产品形态的灵活性。

4.本发明的第二个目的在于提出一种芯片。

5.为达到上述目的,本发明第一方面实施例提出了一种内存控制器,包括:配置接口,用于输入控制信号;数据分配模块,用于接收读或写访问信号和所述控制信号,并根据所述控制信号,确定所述读或写访问信号所需使用的传输通道;数据选择模块,用于将通过使用确定的传输通道所传输的所述读或写访问信号,投递到相应的内存上。

6.本发明实施例的内存控制器包括配置接口、数据分配模块和数据选择模块,其中,配置接口用于输入控制信号,数据分配模块用于接收读或写访问信号和控制信号,并根据控制信号,确定读或写访问信号所需使用的传输通道,数据选择模块用于将通过使用确定的传输通道所传输的读或写访问信号,投递到相应的内存上。本发明实施例的内存控制器通过配置接口所输入的控制信号,确定读或写访问信号所需使用的传输通道是单通道还是双通道,并通过所需使用的传输通道访问内存,从而兼容了双通道访问内存和单通道访问内存,有利于芯片产品形态的灵活性。

7.另外,根据本发明上述实施例提出的内存控制器还可以具有如下附加的技术特征:

8.根据本发明的一个实施例,所述数据分配模块确定所述读或写访问信号所需使用的传输通道为单通道时,所述数据分配模块通过使用所述单通道将所述读或写访问信号传输至所述数据选择模块,所述数据选择模块根据所述控制信号,确定所需访问的内存,并将所述读或写访问信号,投递到所述所需访问的内存上。

9.根据本发明的一个实施例,所述数据分配模块确定所述读或写访问信号所需使用的传输通道为双通道时,所述数据分配模块将所述读或写访问信号投递到对应的读模块或

写模块,所述对应的读模块或所述写模块根据内存颗粒度和所述读或写访问信号所访问的地址空间,将处理后的所述读或写访问信号从所述对应的读模块或所述写模块的两个内存访问接口传输至所述数据选择模块,所述数据选择模块将从所述两个内存访问接口传输出来的所述读或写访问信号,投递到两个内存上。

10.根据本发明的一个实施例,基于所述内存控制器的地址位宽,用以区分交织空间和非交织空间。

11.根据本发明的一个实施例,在所述两个内存的容量不对称时,对所述两个内存中超出对称区域的容量采用非交织访问的方式进行访问。

12.根据本发明的一个实施例,上述的内存控制器,还包括:

13.时钟管理模块,所述时钟管理模块分别与所述数据分配模块、读模块写模块和所述配置接口连接,用于根据所述控制信号,对所述传输通道的通断进行控制。

14.根据本发明的一个实施例,所述时钟管理模块,包括:

15.空闲单元,所述空闲单元的第一端与所述数据分配模块上的双通道读访问接口连接,所述空闲单元的第二端与所述数据分配模块上的双通道写访问接口连接;

16.第一门控时钟单元,所述第一门控时钟单元的控制端与所述空闲单元的第三端连接,所述第一门控时钟单元的输出端与所述读模块连接;

17.第二门控时钟单元,所述第二门控时钟单元的控制端与所述空闲单元的第四端连接,所述第二门控时钟单元的输出端与所述写模块连接;

18.第三门控时钟单元,所述第三门控时钟单元的时钟端用于接收时钟信号,所述第三门控时钟单元的输出端分别与所述第一门控时钟单元的时钟端和所述第二门控时钟单元的时钟端连接,所述第三门控时钟单元的控制端与所述配置接口连接,所述第三门控时钟单元用于在根据所述控制信号确定所述读或写访问信号所需使用的传输通道为单通道时关闭,以使双通道关断,或者,在根据所述控制信号确定所述读或写访问信号所需使用的传输通道为双通道时打开,以使双通道接通。

19.根据本发明的一个实施例,所述数据分配模块确定所述读或写访问信号所需使用的传输通道为双通道时,通过所述空闲单元检测双通道中的读通道和写通道是否空闲;其中,

20.在所述双通道中的读通道空闲时,控制所述第二门控时钟单元关闭;或者,

21.在所述双通道中的写通道空闲时,控制所述第一门控时钟单元关闭。

22.根据本发明的一个实施例,所述传输通道支持axi总线传输;其中,所述axi总线支持fixed、incr和wrap的传输类型,以及符合amba协议要求的传输尺寸和长度的组合。

23.根据本发明的一个实施例,所述读模块和所述写模块支持传输32字节、64字节、128字节和256字节的内存颗粒度。

24.为达到上述目的,本发明第二方面实施例提出了一种芯片,该芯片包括上述的内存控制器。

25.本发明实施例的芯片,通过采用上述内存控制器,能够兼容双通道访问内存和单通道访问内存,有利于芯片产品形态的灵活性。

26.本发明附加的方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本发明的实践了解到。

附图说明

27.本发明上述的和/或附加的方面和优点从下面结合附图对实施例的描述中将变得明显和容易理解,其中:

28.图1是根据本发明实施例的内存控制器的示意图;

29.图2是根据本发明一个实施例的地址空间分配的示意图;

30.图3是根据本发明另一个实施例的地址空间分配的示意图;

31.图4是根据本发明一个实施例的读模块的示意图;

32.图5是根据本发明一个实施例的写模块的示意图;

33.图6是根据本发明一个实施例的内存控制器中时钟管理模块的示意图。

具体实施方式

34.下面详细描述本发明的实施例,所述实施例的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。下面通过参考附图描述的实施例是示例性的,旨在用于解释本发明,而不能理解为对本发明的限制。

35.下面参考附图描述本发明实施例的内存控制器和芯片。

36.在介绍本发明实施例的内存控制器之前,先来介绍下双通道内存交织技术。

37.双通道内存交织技术,是指芯片支持同时访问两个内存,以此提升整体内存带宽,缓解芯片内存瓶颈问题。双通道内存交织技术的实现方法通常是,将总线上针对内存空间的传输,按照预先定义的内存颗粒度进行拆分,然后将拆分过后的传输同时投递到两个内存上,以此实现两个内存并行工作。而负责实现两个内存并行工作的组件,通常被称为双通道内存交织控制器。

38.现有的双通道内存交织控制器存在以下缺陷:

39.1、某些双通道内存交织控制器不支持通道关闭,不利于最终产品形态的灵活性。

40.例如,一旦芯片内置了这样的双通道内存交织控制器,则最终的芯片产品必须使用两个内存组成双通道,否则芯片无法正常工作,也就是说,芯片无法支持单通道内存的产品形态,这不利于最终的芯片产品区分档位,影响芯片的市场策略。

41.2、某些双通道内存交织控制器要求两个内存的容量完全对称。

42.这样的双通道内存交织控制器,在使用不同容量的内存时,会出现内存容量浪费掉的现象,例如,如果两个内存的容量分别为1gb和2gb,则2gb只能使用1gb,剩下的1gb会被浪费掉。

43.3、某些双通道内存交织控制器的可部署性存在限制。

44.这类双通道内存交织控制器并不完全兼容amba axi标准协议,例如仅支持特定的总线传输类型;或者,为了简化设计,改变了传输的axi id,违反了amba原子操作的规则,导致难以部署在处理器访问内存的通路上,也给验证和调试工作带来了极大地不便。

45.而芯片正常工作的一个基本前提是,芯片内部所有主设备都能够通过内存正确的交换数据。双通道内存交织控制器这种可部署性的限制,会打破这个前提,给芯片的架构设计带来阻碍。

46.4、某些双通道内存交织控制器将输入的一笔传输,拆分成多个零散的小传输,这样会额外增加双通道内存交织控制器本身的负担,从而削弱内存的整体性能。

47.为解决上述问题,本发明提出了一种新的内存控制器,该新的内存控制器通过一个配置接口输入控制信号,以确定读或写访问信号所需使用的传输通道是单通道还是双通道,并通过所需使用的传输通道访问内存,从而兼容了双通道访问内存和单通道访问内存,有利于芯片产品形态的灵活性;支持交织空间和非交织空间,当采用容量不对称的两个内存组成双通道时,超出对称区域的内存容量,可以通过非交织空间访问到,将其利用起来;完全兼容标准amba axi协议;不改变读传输或者写传输的axi id;支持硬件自动的门控时钟;支持交织颗粒度可配置。

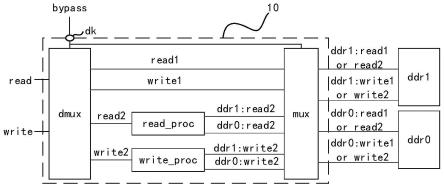

48.图1是根据本发明实施例的内存控制器的示意图。

49.如图1所示,本发明实施例的内存控制器10,包括:配置接口dk、数据分配模块dmux和数据选择模块mux。

50.其中,配置接口dk用于输入控制信号bypass。数据分配模块dmux用于接收读或写访问信号和控制信号bypass,并根据控制信号bypass,确定读或写访问信号所需使用的传输通道。数据选择模块mux用于将通过使用确定的传输通道所传输的读或写访问信号,投递到相应的内存上。

51.在本发明的实施例中,bypass为输入的控制信号,例如为两位静态控制信号bypass,具体可以在内存初始化阶段时配置,该控制信号bypass用于表征读或写访问信号所需使用的传输通道,以及当所需使用的传输通道为单通道时所需访问的内存。

52.控制信号bypass的编码如下:

53.bypass=2’b00时表示为访问内存所使用的传输通道为双通道,访问内存ddr0和内存ddr1;

54.bypass=2’b01时表示为访问内存所使用的传输通道为双通道,访问内存ddr0和内存ddr1;

55.bypass=2’b10时表示访问内存时所使用的传输通道为单通道,且访问内存0;

56.bypass=2’b11时表示访问内存时所使用的传输通道为单通道,且访问内存1。

57.在本发明的实施例中,数据分配模块dmux确定读read或写write访问信号所需使用的传输通道为双通道时,数据分配模块dmux将读或写访问信号投递到对应的读模块read_proc或写模块write_proc,对应的读模块read_proc或写模块write_proc根据内存颗粒度和读read或写write访问信号所访问的地址空间,将处理后的读read或写write访问信号从对应的读模块read_proc或写模块write_proc的两个内存访问接口传输至数据选择模块mux,数据选择模块mux将从两个内存访问接口传输出来的读read或写write访问信号,投递到两个内存上。

58.举例说明,当控制信号bypass为2’b00时,数据分配模块dmux根据控制信号bypass,确定读read或写write访问信号所需使用的传输通道为双通道对应的read2通道或write2通道,并将读read或写write访问信号投递到后级对应的读模块read_proc或写模块write_proc上,读模块read_proc或写模块write_proc根据内存颗粒度和读read或写write访问信号所访问的地址空间,将处理后的传输从对应的读模块read_proc或写模块write_proc的两个内存访问接口送出。然后,后级的数据选择模块mux将通过使用确定的传输通道对应的read2通道或write2通道所传输的读read或写write访问信号,投递到内存ddr0和内存ddr1上。

59.当控制信号bypass为2’b01时,数据分配模块dmux根据该控制信号bypass,确定读read或写write访问信号所需使用的传输通道为双通道对应的read2通道或write2通道,并将读read或写write访问信号投递到后级对应的读模块read_proc或写模块write_proc上,读模块read_proc或写模块write_proc根据内存颗粒度和读read或写write访问信号所访问的地址空间,将处理后的传输从对应的读模块read_proc或写模块write_proc的两个内存访问接口送出。然后,后级的数据选择模块mux将通过使用确定的传输通道对应的read2通道或write2通道所传输的读read或写write访问信号,投递到内存ddr0和内存ddr1上。

60.在本发明的实施例中,数据分配模块dmux确定读read或写write访问信号所需使用的传输通道为单通道时,数据分配模块dmux通过使用单通道将读read或写write访问信号传输至数据选择模块mux,数据选择模块mux根据控制信号bypass,确定所需访问的内存,并将读read或写write访问信号,投递到所需访问的内存上。

61.举例说明,当控制信号bypass为2’b10时,数据分配模块dmux根据该控制信号bypass,确定读read或写write访问信号所需使用的传输通道为单通道对应的read1通道或write1通道后,直接将输入的读read或写write访问信号直接通过相应的单通道read1或write1传输投递到后级的数据选择模块mux。后级的数据选择模块mux将通过使用确定的传输通道对应的read1通道或write1通道所传输的读read或写write访问信号,投递到对应的内存ddr0上。

62.当控制信号bypass为2’b11时,数据分配模块dmux根据该控制信号bypass,确定读read或写write访问信号所需使用的传输通道为单通道对应的read1通道或write1通道后,直接将输入的读read或写write访问信号直接通过相应的单通道read1或write1传输投递到后级的数据选择模块mux。后级的数据选择模块mux将通过使用确定的传输通道对应的read1通道或write1通道所传输的读read或写write访问信号,投递到对应的内存ddr1上。

63.由此,本发明实施例的内存控制器通过设置一个配置接口,该配置接口用于输入控制信号,以确定读或写访问信号所需使用的传输通道是单通道还是双通道,并通过所需使用的传输通道访问内存,从而兼容了双通道访问内存和单通道访问内存,有利于芯片产品形态的灵活性。

64.本发明实施例的内存控制器支持交织控制和非交织空间共存,具体方案如下:

65.在地址最高位额外增加1位,用以通过最高位来区分交织空间和非交织空间,例如:实际内存容量为2个颗粒共4gb,如内存ddr1和ddr0均为2gb,则内存控制器的地址位宽为33位,最高位bit[32],用以区分交织空间和非交织空间,每个空间4gb,如图2所示。

[0066]

这样,当2个内存容量不对称的时候,对超出来的容量依然可以采用非交织访问的方式将其利用起来,示意如图3所示。即言,当两个内存的容量不对称时,对两个内存中超出对称区域的容量采用非交织访问的方式进行访问。

[0067]

图4是根据本发明一个实施例的读模块的示意图。

[0068]

如图4所示,读模块read_proc包括:cmd_split单元和rrsp_reorder单元。

[0069]

其中,cmd_split单元根据输入的颗粒度信息,以及读传输自身的特性,对传输进行拆分,并将拆分后的结果投递到两个内存ddr0和ddr1上,并为rrsp_reorder单元提供拆分信息,方便读响应返回后的重排序操作。

[0070]

cmd_split单元的特性如下:

[0071]

支持所有的amba axi传输类型,以及各种传输尺寸和长度的组合;

[0072]

保持axi id不变,即拆分后的传输,和拆分前的传输axi id一致;

[0073]

对于跨越颗粒度的incr类型传输,只会将其拆分成两笔传输,对应两个内存ddr0和ddr1,而不会拆成更多细碎的传输;

[0074]

对于跨越颗粒度的wpap类型传输,最多拆分成四笔传输(比incr多两笔是为了确保数据的正确传输)。

[0075]

rrsp_reorder单元接受两个内存ddr0和ddr1返回的读响应,鉴于两个内存ddr0和ddr1可能会乱序返回读响应,该模块的一个关键任务是对读响应的重排序,将重排序之后的读响应返回给上游设备。rrsp_reorder单元内部包含了如下子单元:

[0076]

rbf_manage子单元,rbf_manage子单元用于为每笔输入的传输,分配重排序控制资源(rbf_ctrl_per_id),如果两笔传输的axi id一致,则这两笔传输会分配到一样的重排序控制资源;

[0077]

rbf_ctrl_per_id子单元,rbf_ctrl_per_id子单元用于重排序控制模块,使读响应能够按正确的顺序返回给上游;

[0078]

arbiter子单元,arbiter子单元中存储有仲裁逻辑,用于仲裁;

[0079]

buf_ram子单元,buf_ram子单元用于缓冲存储,主要是用来缓冲两个内存的读响应同时写入rbf ram时引起的仲裁冲突;

[0080]

rbf ram子单元,rbf ram子单元用于重排序存储,用来存放两个内存ddr0和ddr1返回的读响应;

[0081]

ram2hsk子单元,ram2hsk子单元具有一个简单的协议转换,用于将rbf ram子单元输出的读数据,转换成axi r通道。

[0082]

图5是根据本发明一个实施例的写模块的示意图。

[0083]

如图5所示,本发明实施例的写模块write_proc,包括:

[0084]

cmd_split单元,cmd_split单元组同read_proc模块中的cmd_split单元,此处不再赘述;

[0085]

wdata_dispatch单元,wdata_dispatch单元用于写传输,除了要向两个内存ddr0和ddr1投递写命令之外,还需要投递写数据,wdata_dispatch单元根据cmd_split单元提供的拆分信息,实现写数据的投递。

[0086]

brsp_reorder单元,brsp_reorder单元类似于read_proc单元中的rrsp_reorder单元,主要是针对写响应的重排序。相较于读响应,axi协议对写响应的规定比较简单,只需要每笔传输返回一个写响应,因此brsp_reorder单元简化很多,内部也不需要大的存储。brsp_reorder单元内部包含了如下子单元:

[0087]

rbf_manage子单元,rbf_manage子单元同rrsp_reorder单元中的rbf_manage子单元;

[0088]

rbf_ctrl_per_id子单元,rbf_ctrl_per_id子单元同rrsp_reorder单元中的rbf_ctrl_per_id子单元;

[0089]

brsp_merge_reg子单元,brsp_merge_reg子单元代替rrsp_reorder单元中的重排序存储,对两个内存ddr0和ddr1返回的写响应进行合并,将合并后的响应返回给上游。

[0090]

图6是根据本发明一个实施例的内存控制器中时钟管理模块的示意图。

[0091]

如图6所示,本发明实施例的内存控制器10,还包括:时钟管理模块11。其中,时钟管理模块11分别与数据分配模块dmux、读模块read_proc、写模块write_proc和配置接口dk连接,时钟管理模块11用于根据控制信号,对传输通道的通断进行控制。

[0092]

如图6所示,时钟管理模块11,包括:空闲单元idle_detect、第一门控时钟单元cg1、第二门控时钟单元cg2和第三门控时钟单元cg3。

[0093]

其中,空闲单元idle_detect的第一端与数据分配模块dmux上的双通道读访问接口连接,空闲单元idle_detect的第二端与数据分配模块dmux上的双通道写访问接口连接;第一门控时钟单元cg1的控制端与空闲单元idle_detect的第三端连接,第一门控时钟单元cg1的输出端与读模块read_proc连接;第二门控时钟单元cg2的控制端与空闲单元idle_detect的第四端连接,第二门控时钟单元cg2的输出端与写模块write_proc连接;第三门控时钟单元cg3的时钟端用于接收时钟信号,第三门控时钟单元cg3的输出端分别与第一门控时钟单元cg1的时钟端和第二门控时钟单元cg2的时钟端连接,第三门控时钟单元cg3的控制端与配置接口连接,第三门控时钟单元cg3用于在根据控制信号确定读或写访问信号所需使用的传输通道为单通道时关闭,以使双通道关断,或者,在根据控制信号确定读或写访问信号所需使用的传输通道为双通道时打开,以使双通道接通。

[0094]

在该实施例中,本发明的内存控制器支持硬件自动关闭空闲电路的时钟,以降低功耗。具体来说,本发明可以采用级联的门控时钟方案,最大程度的关闭空闲电路的时钟,如图6所示。

[0095]

举例说明,当控制信号bypass配置为单通道方案时,通过控制信号bypass将源头的第三门控时钟单元cg3关闭,此时只有第三门控时钟单元cg3的时钟在翻转,第一门控时钟单元cg1和第二门控时钟单元cg2的时钟全部关闭,此时双通道关断;当控制信号bypass配置为双通道方案时,通过控制信号将源头的第三门控时钟单元cg3打开,此时双通道接通。

[0096]

在本发明的一个实施例中,数据分配模块dmux确定读或写访问信号所需使用的传输通道为双通道时,通过空闲单元idle_detect检测双通道中的读通道read2和写通道write2是否空闲;其中,在双通道中的读通道read2空闲时,控制第二门控时钟单元cg2关闭;或者,在双通道中的写通道write2空闲时,控制第一门控时钟单元cg1关闭。

[0097]

也就是说,当控制信号bypass配置为双通道方案时,空闲单元idle_detect检测读通道read2或写通道write2是否空闲;其中,当读通道read2空闲时,将读模块read_proc的时钟关闭;当写通道write2空闲时,将写模块write_proc的时钟关闭。

[0098]

由此,本发明实施例的内存控制器支持硬件自动的门控时钟,配置为单通道方案时,本发明实施例中的绝大多数电路的时钟都会被自动关闭;配置为双通道方案时,当内存通路上的传输结束,本发明也可以自动关闭相应电路的时钟,以节省电路的动态功耗。

[0099]

在本发明的实施例中,传输通道支持axi总线传输;其中,axi总线支持fixed、incr和wrap的传输类型,以及符合amba协议要求的传输尺寸和长度的组合。在本发明的内存控制器,并不改变读传输或者写传输的axi id,使本发明的内存控制器很好的支持axi原子操作,而原子操作对于处理器类型的主设备来说,是必不可少的。本发明可以部署在任意符合amba axi标准协议的内存访问通路上,包括处理器访问内存的通路,而不会引入任何额外的限制。

[0100]

在本发明的实施例中,读模块read_proc和写模块write_proc支持的内存颗粒度可配置,例如支持传输32字节、64字节、128字节和256字节的内存颗粒度,还可以根据内存本身的突发长度,以及性能调优的结果,选择适合的交织颗粒度。本发明不会对内存控制器引入额外的负担,如果一笔传输的数据量超过了指定内存颗粒度,本发明不会将其拆分成许多个零散的小传输,而是尽量将其投递到同一个内存的传输合并成一笔。

[0101]

本发明实施例的内存控制器可以支持更灵活的产品形态和物料选型,例如:既支持内存容量对称的双通道,也支持内存容量非对称的双通道,非对称部分的内存容量也能以非交织的方式访问,而不会造成浪费;即支持双通道内存的产品形态,也支持单通道内存的产品形态,且具体使用哪个通道可以根据pcb板级布局布线调整。

[0102]

综上所述,本发明实施例的内存控制器包括配置接口、数据分配模块和数据选择模块,其中,配置接口用于输入控制信号,数据分配模块用于接收读或写访问信号和控制信号,并根据控制信号,确定读或写访问信号所需使用的传输通道,数据选择模块用于将通过使用确定的传输通道所传输的读或写访问信号,投递到相应的内存上。本发明实施例的内存控制器通过配置接口所输入的控制信号,确定读或写访问信号所需使用的传输通道是单通道还是双通道,并通过所需使用的传输通道访问内存,从而兼容了双通道访问内存和单通道访问内存,有利于芯片产品形态的灵活性;支持交织空间和非交织空间,当采用容量不对称的两个内存组成双通道时,超出对称区域的内存容量,可以通过非交织空间访问到,将其利用起来;完全兼容标准amba axi协议;不改变读传输或者写传输的axi id;支持硬件自动的门控时钟;支持交织颗粒度可配置。

[0103]

基于上述实施例,本发明还提出了一种芯片,该芯片包括上述的内存控制器。

[0104]

本发明实施例的芯片,通过采用上述内存控制器,能够兼容双通道访问内存和单通道访问内存,有利于芯片产品形态的灵活性。

[0105]

在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不必须针对的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任一个或多个实施例或示例中以合适的方式结合。另外,在不相互矛盾的情况下,本领域的技术人员可以将本说明书中描述的不同实施例或示例以及不同实施例或示例的特征进行结合和组合。

[0106]

此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括至少一个该特征。在本发明的描述中,“多个”的含义是至少两个,例如两个,三个等,除非另有明确具体的限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1