一种低电压标准逻辑单元门延时模型的建立方法

1.本发明涉及一种静态时序分析技术,属于集成电路设计自动化技术领域。

背景技术:

2.随着人们对便携式电子设备需求迅速增加,如何提升这一类设备的续航时间成为研究的热点。由于电池技术相比于集成电路发展缓慢,而穿戴设备、环境检测设备、医疗电子等便携设备对于功耗有很高的要求。因此,通过降低芯片功耗来增加设备的续航时间成为更加有效的方式。通过降低供电电压来减少功耗是一项直接有效的技术。而随着电路规模的急剧增大,快速准确的低电压电路时序仿真验证成为一个亟待解决的问题。另一方面,晶体管沟道电流、本征电容等对工艺参数波动(例如沟道长度等)随着电压的降低变得越来越敏感,可以直接导致电路延时造成300%的延迟波动[5,6]。因此,建立准确的低电压电路延时模型的是非常重要的。

[0003]

对于数字集成电路设计而言,要使电路正常工作,必须同时满足建立时间,保持时间的要求。所以电路的性能需要基于这个条件满足的前提下提升。当电路中最长延时路径满足建立时间要求,最短延时路径满足保持建立时间要求,则认为电路满足时序要求。而时序路径是由逻辑门组成,因此,准确预测路径的延时的前提,需要给逻辑门单元建立准确的延时模型。

技术实现要素:

[0004]

技术问题:为了解决现有技术中存在的缺陷,本发明的目的在于提供一种低电压标准逻辑单元门延时模型的建立方法,以提高先进工艺近阈值工作电压条件下,对时序路径延时预测的准确性。

[0005]

技术方案:本发明是一种低电压标准逻辑单元门延时模型的建立方法,所述的模型包括电流源模型和低电压下标准逻辑单元门延时模型,其中:

[0006]

所述电流源模型,表示不同栅源电压v

gs

和漏源电压v

ds

表征pmos和nmos晶体管的沟道电流源模型;

[0007]

所述低电压为标准逻辑单元门的供电电压0.4v;

[0008]

所述标准逻辑单元门,包括反相器、二输入与非门、二输入或非门;

[0009]

所述延时模型,根据输入信号转换时间、标准逻辑单元门的工艺参数和标准逻辑单元门的经验参数,建立逻辑单元门输出电压解析公式,之后,根据电压解析公式建立延时公式计算出标准逻辑门单元的延时;

[0010]

所述标准逻辑单元门的工艺参数,包括晶体管宽度w、晶体管长度l、热电压v

t

、阈值电压v

th

;

[0011]

所述标准逻辑单元门的经验参数,包括参数i0,λ,n,γ;其中,i0是栅源电压、漏源电压为0v时与沟道电流相关的经验参数,λ表示漏致势垒降低效应相关的经验参数,n表示介于1到2之间的常数,γ表示晶体管沟道电流的修正参数;

[0012]

所述延时模型的建立方法的步骤如下,

[0013]

步骤1,建立nmos、pmos晶体管的沟道电流模型;

[0014]

步骤2,基于晶体管的沟道电流模型,建立逻辑单元门的输出电压随时间变化的解析模型;

[0015]

步骤3,基于逻辑单元门的输出电压解析模型,建立逻辑单元的门的延时模型;

[0016]

步骤4,基于逻辑单元门的延时模型,建立组合电路中时序路径的延时模型。

[0017]

其中:

[0018]

所述建立逻辑单元的门的延时模型包括,

[0019]

步骤21,建立反相器的输出电压解析模型;

[0020]

步骤22,对于二输入逻辑单元门,建立晶体管串联的节点电压随时间变化的解析模型;

[0021]

步骤23,基于反相器输出电压和节点电压的解析模型,建立二输入逻辑门单元的输出电压延时模型。

[0022]

所述晶体管沟道电流模型,在低电压下,根据标准逻辑单元门的工艺参数和拟合的经验参数和沟道电流公式其中,v

gs

,v

ds

分别为晶体管的漏源电压和栅源电压,建立的修正后的沟道电流公式其中i0,n,λ,γ表示经验参数,w表示晶体管宽度、l表示晶体管长度、v

t

表示热电压、v

th

表示阈值电压。

[0023]

所述漏源电压和栅源电压,其相关微分方程考虑了参数米勒电容cm,负载电容c

l

,输入转换时间τ,分别表示反相器,二输入与非门和二输入或非门,方程式如下

[0024]

(1)反相器,微分方程为其中,v

in

,v

out

分别为输入输出电压,in,i

p

分别为流过nmos,pmos晶体管的电流;

[0025]

(2)二输入与非门,微分方程为其中,va表示输入信号a,i

n1

,i

p1

,i

p2

分别为流过靠近输出端的nmos晶体管和两个pmos晶体管的沟道电流;

[0026]

(3)二输入或非门,微分方程为其中,i

n1

,i

n2

,i

p1

分别为流过靠近输出端的pmos晶体管和两个nmos晶体管的沟道电流;

[0027]

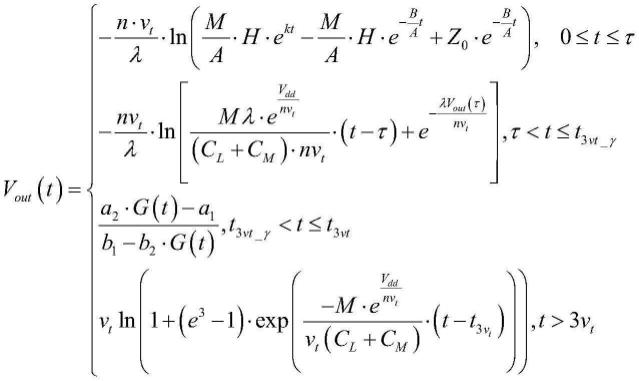

所述输出电压随时间变化的分段解析公式,包括的表达式如下,

[0028]

(1)反相器,输出电压解析式如下,

[0029][0030]

其中,a=(nv

t

/λ)(c

l

+cm),b=cm(v

dd

/τ),m=i0·

w/l

·

exp(v

th0

/nv

t

),

[0031]

d=1/(k+(b/a)),k=v

dd

/(τ

·n·vt

),

[0032][0033][0034][0035][0036]

t0表示输出电压为时所对应的事件;

[0037]

(2)二输入与非门,输出电压解析式如下,

[0038][0039]

其中,

[0040][0041][0042]

t

10

表示二输入与非门中节点电压线性近似需要拟合的参数,

[0043]vmax

表示nmos晶体管串联处的节点电压的最大值,

[0044]

t

max

表示nmos晶体管串联处的节点电压的最大值所对应的时间;

[0045]

(3)二输入或非门,输出电压解析式如下,

[0046][0047]

其中,

[0048][0049][0050]

t

20

表示二输入或非门中节点电压线性近似需要拟合的参数,

[0051]vmin

表示pmos晶体管串联处的节点电压的最小值,

[0052]

t

min

表示pmos晶体管串联处的节点电压的最小值所对应的时间,

[0053]vt

表示热电压,v

dd

表示供电电压,v

out,τ

表示输出电压在时间为τ时的电压值。

[0054]

所述逻辑单元的门的延时模型,基于延时公式t

delay

=t

50%vout-t

50%vin

和输出电压随时间变化解析式得:

[0055]

(1)反相器延时公式如下,

[0056][0057]

(2)二输入与非门延时公式如下,

[0058][0059]

(3)二输入或非门延时公式如下,

[0060][0061]

所述逻辑单元门的输出电压解析模型,基于基尔霍夫电流定律和晶体管沟道电流模型,通过建立漏源电压和栅源电压相关微分方程,并求解得到的输出电压随时间变化的分段解析式。

[0062]

有益效果:本发明提出的基于晶体管沟道电流的逻辑单元门延时模型的建立方法,提高先进工艺近阈值工作电压条件下,提高逻辑单元门时序行为描述的准确性。首先,计算反相器逻辑单元门的输出电压随时间变化的解析公式。其次,计算反相器逻辑单元门

的延时解析公式。最后,计算标准逻辑单元门延时。该方法与hspice仿真相比,平均延时误差不大于4%。并且,本文修正了沟道电流模型,并且提出了通过解析公式建立二输入与非门和二输入或非门的方法。与智能分析反相器链电路的延时模型相比,提高了解析延时模型的应用范围。

附图说明

[0063]

图1是反相器晶体管级电路图示例,

[0064]

图1中,v

dd

表示工作电压,a表示输入信号,q表示输出信号,cm,c

l

分别表示米勒电容和负载电容,i

cm

,i

p

,in,i

cl

分别表示流过米勒电容的电流,pmos的沟道电流,nmos的沟道电流和流过负载电容的电流。

[0065]

图2是二输入与非门晶体管级电路图示例,

[0066]

图2中,v

dd

表示工作电压,a,b表示输入信号,p表示输出信号。cm,c

l

分别表示米勒电容和负载电容,i

cm

,i

p1

,i

p2

,i

n1

,i

n2

,i

cl

,分别表示流过米勒电容的电流,pmos1的沟道电流,pmos2的沟道电流,nmos1的沟道电流,nmos2的沟道电流和流过负载电容的电流。c

m1

,c

m2

,cj是节点q处的寄生电容,i

cm1

,i

cm2

,i

cj

分别表示流过电容c

m1

,c

m2

,cj的电流。

[0067]

图3是二输入或非门晶体管级电路图示例,

[0068]

图3中,v

dd

表示工作电压,a,b表示输入信号,p表示输出信号。cm,c

l

分别表示米勒电容和负载电容,i

cm

,i

p1

,i

p2

,i

n1

,i

n2

,i

cl

,分别表示流过米勒电容的电流,pmos1的沟道电流,pmos2的沟道电流,nmos1的沟道电流,nmos2的沟道电流和流过负载电容的电流。c

m1

,c

m2

,cj是节点q处的寄生电容,i

cm1

,i

cm2

,i

cj

分别表示流过电容c

m1

,c

m2

,cj的电流。

[0069]

图4是计算标准逻辑门单元延时的流程图。

具体实施方式

[0070]

本发明的一种低电压标准逻辑单元门延时模型的建立方法包括以下步骤,

[0071]

步骤1,建立nmos和pmos晶体管沟道电流模型,公式如下,

[0072][0073][0074]

其中,i

ds

分别表示晶体管的源漏沟道电流,v

th0

为阈值电压,v

gs

,v

ds

分别表示晶体管的漏源电压和栅源电压,λ

ds

表示dbli(漏端引入的势垒降低)因子,w表示晶体管宽度,l表示晶体管长度,v

t

为热电压,i0,n为与工艺相关的经验常数。

[0075]

步骤2,拟合步骤1中提出的沟道电流模型的需要拟合的参数λ,γ,n,i0。拟合的方法是与hspice仿真的晶体管沟道电流对比,遍历四个参数,使其与hspice的仿真数据的方差最小采用。其算法伪代码如下表所示,

[0076][0077][0078]

步骤3,基于基尔霍夫电流定律,根据不同逻辑单元门建立不同的方程或方程组,

[0079]

(1)反相器中输出电压随时间变化的解析式,基于基尔霍夫电流定律,在反相器的输出端点建立微分方程,

[0080][0081]

其中,其中,c

l

为负载电容,cm为密勒电容,v

in

,v

out

分别为输入输出电压,in,i

p

分为流过nmos,pmos晶体管的电流。

[0082]

输入从低到高变化的情况下,输入电压满足如下关系,

[0083][0084]

输入由低到高变化时,主要是由nmos晶体管对负载电容c

l

放电,而pmos晶体管的电流很小可以忽略,即,i

p

≈0。因此,再结合步骤1、2建立的晶体管沟道电流模

[0085]

型,得到输出电压随不同时间变化的分段表达式,

[0086]

当0≤t≤τ时,得

[0087][0088]

其中,a=(nv

t

/λ)(c

l

+cm),b=cm(v

dd

/τ),m=i0·

w/l

·

exp(v

th0

/nv

t

),

[0089]

d=1/(k+(b/a)),k=v

dd

/(τ

·n·vt

),

[0090]

当τ<t<t

3vt

时,v

in

(t)=v

dd

,得,

[0091][0092]

当3v

t

≤v

out

≤3v

t

/γ时,得

[0093][0094]

其中,

[0095][0096][0097][0098][0099]

当v

out

《3v

t

时,v

in

(t)=v

dd

.t/τ,此时满足1《exp((λv

out

(t))/(nv

t

))《exp(3λ/n)≈1,所以可得,

[0100][0101]

综上,反相器的输出电压随时间变化的解析式如下,

[0102][0103]

(2)二输入与非门的输出电压随时间变化的解析式,在二输入与非门的输出端点建立微分方程,如下,

[0104][0105]

对节点q电压分段线性近似如下,

[0106][0107]

同反相器分段求解,可得二输入与非门随时间变化的电压如下,

[0108][0109]

(3)二输入或非门的输出电压随时间变化的解析式,在二输入的或非门输出端点建立微分方程,如下,

[0110][0111]

对节点q电压分段线性近似如下,

[0112][0113]

同反相器分段求解,可得二输入或非门随时间变化的电压如下,

[0114][0115]

步骤4,根据步骤3建立的输出电压随时间变化的分段解析式,求解得出不同逻辑单元门的延时公式如下,

[0116]

(1)反相器延时公式如下,

[0117]

[0118]

(2)二输入与非门延时公式如下,

[0119][0120]

(3)二输入或非门延时公式如下,

[0121][0122]

(1)输入smic 28nm工艺pdk文件,使用hspice软件,选择tt工艺角,温度25℃,选择供电电压0.4v,在不同v

gs

,v

ds

下,仿真nmos,pmos晶体管,以拟合参数i0,n,λ,γ,得到沟道电流模型,仿真条件如表1-1所示。

[0123]

表1-1仿真参数设置

[0124][0125]

(2)在(1)的基础上,测试图1,2,3所示的标准逻辑门单元的延时。测量方式,计算不同转换时间和不同负载下逻辑单元门的延时,并与hspice仿真延时作为对比。

[0126]

最后结果表明,与spice仿真结果相比,输出电压由高到低变化时,其最大误差小于3.5%,输出电压由低到高变化时,其最大误差不高于2.5%。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1