一种可支持分区加载的信号处理模块的制作方法

1.本发明涉及数字信号处理技术领域,尤其涉及一种可支持分区加载的信号处理模块。

背景技术:

2.随着我国国力的发展,我国的国防需求日益激增,尤其是在航天航空领域的技术急需突破,因此在航空电子方面的安全性尤为重要,但仍然存在不足之处。

3.由于传统的信号处理模块不支持分区加载的功能,因而在对不同程序烧写过程中,会降低加载效率,使模块的功能受限;另外在程序出现故障时,无法对故障进行准确定位,导致模块设备的可靠性降低,修复难度提升。

技术实现要素:

4.为了解决上述问题,本发明提出一种可支持分区加载的信号处理模块,该模块具有高效率、高性能、可动态分配任务的数字信号处理单元,可完成系统中频及基带信号的采集、处理,同时完成与整机的数据、指令等信息的交互等处理功能。其具有可靠性高、成本低、体积小、适用范围广、可批量生产等优点。

5.本发明采用的技术方案如下:

6.一种可支持分区加载的信号处理模块,包括fpga芯片以及与所述fpga芯片电连接的多个adc芯片、dsp芯片、cpld芯片、时钟管理单元和flash存储器,其中:

7.所述adc芯片设置有多路采集通道,多个所述adc芯片能够根据dsp芯片配置的多种采样频率采集处理多种频率的信号并输出至fpga芯片。

8.所述fpga芯片能够与adc芯片配合完成信号采样与处理,与dsp芯片进行数据交互并给dsp芯片提供时钟和复位,给时钟管理单元提供同步和通信信号,并进行温度和电压采集以及电源控制。

9.所述时钟管理单元能够提供两种基准时钟并形成需要的时钟频率进行多组输出,将外部输入的采样时钟发送给adc芯片进行采样。

10.所述flash存储器设置有多个分区,dsp芯片控制着每个分区内的启动地址,并能够给cpld芯片写初始地址以及启动信号,通过cpld芯片引导flash存储器的程序加载,从而通过启动地址的不同实现分区加载。

11.进一步地,所述fpga芯片设置有对外的数据交互、离线信号线控制以及高速串行数据交互接口。

12.进一步地,所述fpga芯片包括功能fpga和辅助fpga,所述功能fpga电连接辅助fpga、adc芯片、flash存储器和ddr3存储器;所述辅助fpga完成和功能fpga的通信,给dsp芯片提供时钟和复位以及通信,并配置adc芯片,给时钟管理单元提供同步和通信信号,并进行温度和电压采集以及电源控制。

13.进一步地,所述功能fpga设置有通信接口,包括jesd204b、gth、srio、lvds、blvds

和lvttl。

14.进一步地,所述dsp芯片还连接有ddr2存储器和nvram存储器。

15.进一步地,所述fpga芯片通过emif总线连接dsp芯片。

16.进一步地,所述fpga芯片通过spi总线连接cpld芯片。

17.进一步地,所述时钟管理单元提供的基准时钟包括100mhz时钟和125mhz时钟。

18.本发明的有益效果在于:

19.(1)可靠性高:本发明主要采用多个能够独立工作的adc芯片,并且能够通过dsp芯片配置不同的采样频率,同时每个adc芯片具有多路采集通道,进而能够在不同的adc采集通道内配置不同的采样频率,能够增加采样频率范围,极大的提升了系统的可靠性与应用范围。例如在信号采集过程中,出现一个adc芯片损坏停止工作的场景,能够通过更改其他adc芯片的采样率,维持采集系统的基本功能,提升系统的使用寿命,降低出现故障次数。

20.(2)成本低:本发明采用fpga芯片与dsp芯片协同工作,并增加了具有多种时钟频率的时钟管理单元,其价格与多种晶振相比,极大的缩减了成本。其应用范围比较广泛,具有成本低廉的特点。

21.(3)适用面广:本发明通过接收不同频率的信号,来提升模块的适用范围,同时具有分区加载的功能,拥有余度设计优势,能够提升烧写程序的多样性和稳定性。

22.(4)切换简单:本发明在实际使用中能够通过dsp芯片的配置方式来切换采样频率和所需加载的分区,使其能达到切换的目的,并且能够增加芯片实时温度、实时电压。

附图说明

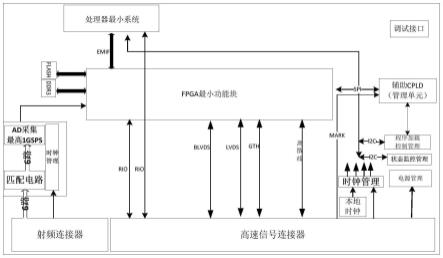

23.图1是本发明实施例的一种可支持分区加载的信号处理模块工作原理图。

24.图2是本发明实施例的时钟分配图。

25.图3是本发明实施例的分区加载流程图。

具体实施方式

26.为了对本发明的技术特征、目的和效果有更加清楚的理解,现说明本发明的具体实施方式。应当理解,此处所描述的具体实施例仅用以解释本发明,并不用于限定本发明,即所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明的实施例,本领域技术人员在没有做出创造性劳动的前提下所获得的所有其他实施例,都属于本发明保护的范围。

27.如图1所示,本实施例提供了一种可支持分区加载的信号处理模块,包括fpga芯片、多个adc芯片、dsp芯片、cpld芯片、时钟管理单元和flash存储器,其中fpga芯片分别电连接多个adc芯片、dsp芯片、cpld芯片、时钟管理单元和flash存储器。

28.adc芯片设置有多路采集通道,多个adc芯片能够根据dsp芯片配置的多种采样频率采集处理多种频率的信号并输出至fpga芯片。由于多个adc芯片能够独立工作,并且能够通过dsp芯片配置不同的采样频率,同时每个adc芯片具有多路采集通道,进而能够在不同的adc采集通道内配置不同的采样频率,增加采样频率范围,极大的提升了系统的可靠性与应用范围。例如,在信号采集过程中,出现一个adc芯片损坏停止工作的场景,能够通过更改其他adc芯片的采样率,维持采集系统的基本功能,提升系统的使用寿命,降低出现故障次

数。

29.fpga芯片能够与adc芯片配合完成信号采样与处理,与dsp芯片进行数据交互并给dsp芯片提供时钟和复位,给时钟管理单元提供同步和通信信号,并进行温度和电压采集以及电源控制。此外,fpga芯片设置有对外的数据交互、离线信号线控制以及高速串行数据交互接口。优选地,fpga芯片包括功能fpga和辅助fpga,功能fpga电连接辅助fpga、adc芯片、flash存储器和ddr3存储器;辅助fpga完成和功能fpga的通信,给dsp芯片提供时钟和复位以及通信,并配置adc芯片,给时钟管理单元提供同步和通信信号,并进行温度和电压采集以及电源控制。

30.时钟管理单元能够提供两种基准时钟,优选地,这两种基准时钟分别为100mhz时钟和125mhz时钟,时钟管理单元把125mhz时钟形成需要的时钟频率进行多组输出,并将外部输入的采样时钟发送给adc芯片进行采样,如图2所示为时钟分配图。

31.flash存储器设置有多个分区,如图3所示为分区加载流程图,dsp芯片控制着每个分区内的启动地址,并能够给cpld芯片写初始地址以及启动信号,通过cpld芯片引导flash存储器的程序加载,从而通过启动地址的不同实现分区加载。因此,通过dsp芯片的配置方式可以切换采样频率和所需加载的分区,使其能达到切换分区的目的。

32.优选地,dsp芯片还连接有ddr2存储器和nvram存储器。

33.优选地,功能fpga设置有通信接口,包括jesd204b、gth、srio、lvds、blvds和lvttl。

34.优选地,fpga芯片通过emif总线连接dsp芯片。

35.优选地,fpga芯片通过spi总线连接cpld芯片。

36.以上所述仅是本发明的优选实施方式,应当理解本发明并非局限于本文所披露的形式,不应看作是对其他实施例的排除,而可用于各种其他组合、修改和环境,并能够在本文所述构想范围内,通过上述教导或相关领域的技术或知识进行改动。而本领域人员所进行的改动和变化不脱离本发明的精神和范围,则都应在本发明所附权利要求的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1