数据处理方法、装置、电子设备及存储介质与流程

本技术涉及芯片数据处理领域,具体而言,涉及一种数据处理方法、装置、电子设备及存储介质。

背景技术:

1、随着fpga芯片的快速发展,用户对fpga芯片的数据传输速度的要求不断提高。在数据传输过程中,数据链路和cpu(central processing unit,中央处理器)均会频繁访问ddr(double data rate synchronous dynamic random access memory,双倍速率同步动态随机存储器,简称ddr)。然而,由于ddr的带宽较为有限,难以支持数据高速传输中的带宽需求,从而限制了fpga芯片的数据传输速度。

技术实现思路

1、本技术实施例的目的在于提供一种数据处理方法、装置、电子设备及存储介质,用以缓解fpga芯片中ddr带宽不足的问题,提高fpga芯片的数据传输速度。

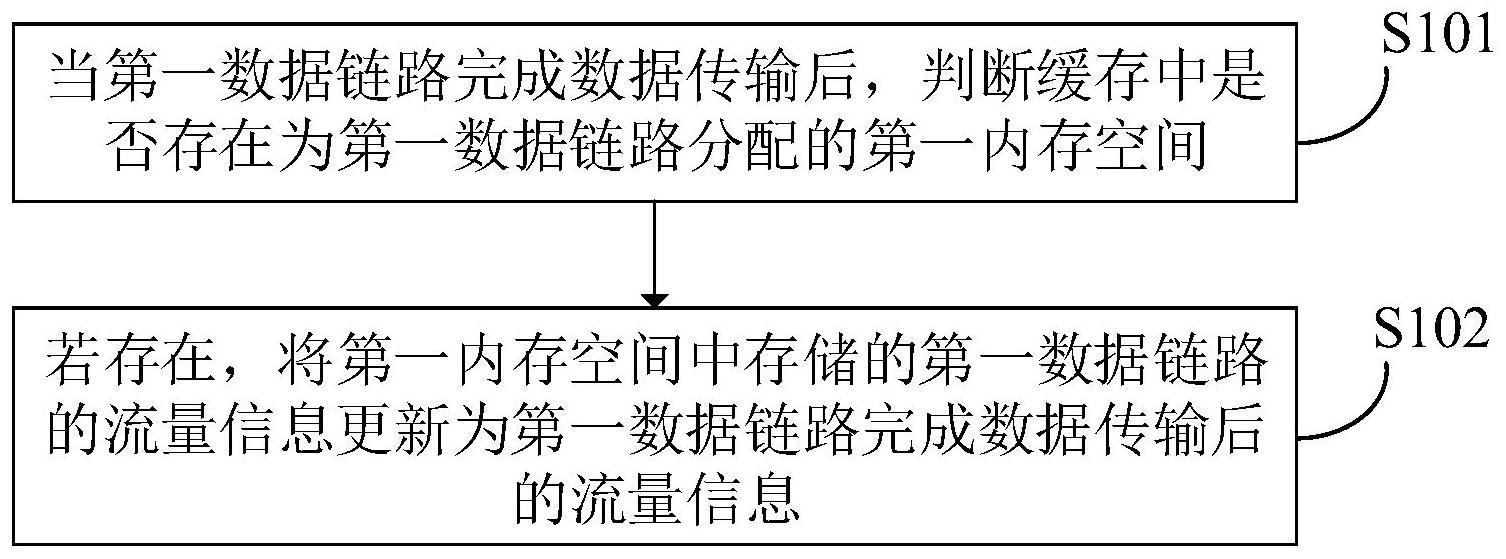

2、第一方面,本技术提供一种数据处理方法,应用于fpga芯片,所述fpga芯片包括缓存和数据通路,所述缓存与所述数据通路连接,所述方法包括:当第一数据链路完成数据传输后,判断所述缓存中是否存在为所述第一数据链路分配的第一内存空间,其中,所述第一数据链路为所述数据通路中的一条传输链路,所述第一内存空间用于存储所述第一数据链路的流量信息;若存在,将所述第一内存空间中存储的第一数据链路的流量信息更新为所述第一数据链路完成数据传输后的流量信息。

3、在上述实现过程中,预先在fpga芯片的缓存(cache)中为数据链路分配内存空间。数据链路完成数据传输后,若该数据链路在缓存中存在内存空间,数据链路直接访问缓存,将本次数据传输的流量信息更新到缓存中,减少数据链路访问ddr的次数,节省ddr的带宽,从而提高fpga芯片的数据传输速度。

4、在可选的实施方式中,在所述判断所述缓存中是否存在为所述第一数据链路分配的第一内存空间之前,所述方法包括:当建立所述第一数据链路时,为所述第一数据链路生成第一id;根据所述第一id在所述缓存中分配一内存空间作为所述第一内存空间。

5、在上述实现过程中,为每条数据链路分配一个唯一的id。每条数据链路在缓存中的读写地址为对应的id,从而可以保证每条数据链路在缓存中的读写地址不冲突。

6、在可选的实施方式中,所述fpga芯片还包括双倍速率同步动态随机存储器,在所述判断所述缓存中是否存在为所述第一数据链路分配的第一内存空间之前,所述方法包括:当建立所述第一数据链路时,为所述第一数据链路生成第一id;根据所述第一id在所述缓存或所述双倍速率同步动态随机存储器中分配一内存空间作为所述第一内存空间。

7、在上述实现过程中,考虑到fpga中的数据链路数量可能很大,为了兼顾资源利用率和数据传输效率,将一部分数据链路对应的内存空间设置在缓存中,其余的数据链路对应的内存空间设置在ddr中。

8、在可选的实施方式中,所述缓存包括多个内存空间,每个内存空间对应一条数据链路的id,每个内存空间的地址为该内存空间对应的数据链路的id的前n位比特位值,所述根据所述第一id在所述缓存或所述双倍速率同步动态随机存储器中分配一内存空间作为所述第一内存空间,包括:当所述缓存中不存在一内存空间的地址与所述第一id的前n位比特位值相同时,在所述缓存中分配一内存空间作为所述第一内存空间;当所述缓存中存在一内存空间的地址与所述第一id的前n位比特位值相同且该内存空间对应的数据链路的id与所述第一id不相同时,在所述双倍速率同步动态随机存储器中分配一内存空间作为所述第一内存空间。

9、在上述实现过程中,在分配内存空间时,根据第一id的前n位比特位值确定缓存中是否存在空闲的内存空间,若存在,在缓存中分配一内存空间作为第一内存空间;若不存在,则在ddr中分配一内存空间作为第一内存空间。通过上述方式,可以有效避免内存空间冲突。

10、在可选的实施方式中,所述缓存包括多个内存空间,每个内存空间对应一条数据链路的id,每个内存空间的地址为该内存空间对应的数据链路的id的前n位比特位值,所述根据所述第一id在所述缓存或所述双倍速率同步动态随机存储器中分配一内存空间作为所述第一内存空间,包括:当所述缓存中不存在一内存空间的地址与所述第一id的前n位比特位值相同时,在所述缓存中分配一内存空间作为所述第一内存空间;当所述缓存中存在一内存空间的地址与所述第一id的前n位比特位值相同且该内存空间对应的数据链路的id与所述第一id不相同时,在所述双倍速率同步动态随机存储器中分配第二内存空间用于存放该内存空间对应的数据链路的流量数据,将所述缓存中该内存空间作为所述第一内存空间。

11、在上述实现过程中,在分配内存空间时,当出现内存空间冲突时,在双倍速率同步动态随机存储器中分配第二内存空间用于存放缓存中原本存放的流量数据,进而将缓存中的内存空间分配给第一数据链路,从而有效避免内存空间冲突。

12、在可选的实施方式中,所述方法还包括:获取所述第一数据链路对应的第一内存空间中存储的当前流量信息;若所述第一内存空间中存储的当前流量信息与cpu中预先保存的所述第一数据链路对应的流量信息相同,关闭所述第一数据链路并清除所述第一数据链路对应的第一内存空间;若所述第一内存空间中存储的当前流量信息与cpu中预先保存的所述第一数据链路对应的流量信息不相同,将cpu中预先保存的所述第一数据链路对应的流量信息更新为所述第一内存空间中存储的当前流量信息。

13、在上述实现过程中,通过上述方式,实现对数据链路的动态监控,维持处于工作状态中的数据链路,关闭长期未发送数据的数据链路。

14、在可选的实施方式中,所述第一数据链路的流量信息包括过包统计信息和字节统计信息。

15、第二方面,本技术提供一种数据处理装置,配置于fpga芯片,所述fpga芯片包括缓存和数据通路,所述缓存与所述数据通路连接,所述装置包括:判断模块,用于在第一数据链路完成数据传输后,判断所述缓存中是否存在为所述第一数据链路分配的第一内存空间,其中,所述第一数据链路为所述数据通路中的一条传输链路,所述第一内存空间用于存储所述第一数据链路的流量信息;更新模块,用于在所述缓存中存在为所述第一数据链路分配的第一内存空间时,将所述第一内存空间中存储的第一数据链路的流量信息更新为所述第一数据链路完成数据传输后的流量信息。

16、在可选的实施方式中,所述装置还包括分配模块,用于当建立所述第一数据链路时,为所述第一数据链路生成第一id;根据所述第一id在所述缓存中分配一内存空间作为所述第一内存空间。

17、在可选的实施方式中,所述fpga芯片还包括双倍速率同步动态随机存储器,所述分配模块用于当建立所述第一数据链路时,为所述第一数据链路生成第一id;根据所述第一id在所述缓存或所述双倍速率同步动态随机存储器中分配一内存空间作为所述第一内存空间。

18、在可选的实施方式中,所述缓存包括多个内存空间,每个内存空间对应一条数据链路的id,每个内存空间的地址为该内存空间对应的数据链路的id的前n位比特位值,所述分配模块具体用于当所述缓存中不存在一内存空间的地址与所述第一id的前n位比特位值相同时,在所述缓存中分配一内存空间作为所述第一内存空间;当所述缓存中存在一内存空间的地址与所述第一id的前n位比特位值相同且该内存空间对应的数据链路的id与所述第一id不相同时,在所述双倍速率同步动态随机存储器中分配一内存空间作为所述第一内存空间。

19、在可选的实施方式中,所述缓存包括多个内存空间,每个内存空间对应一条数据链路的id,每个内存空间的地址为该内存空间对应的数据链路的id的前n位比特位值,所述分配模块具体用于当所述缓存中不存在一内存空间的地址与所述第一id的前n位比特位值相同时,在所述缓存中分配一内存空间作为所述第一内存空间;当所述缓存中存在一内存空间的地址与所述第一id的前n位比特位值相同且该内存空间对应的数据链路的id与所述第一id不相同时,在所述双倍速率同步动态随机存储器中分配第二内存空间用于存放该内存空间对应的数据链路的流量数据,将所述缓存中该内存空间作为所述第一内存空间。

20、在可选的实施方式中,所述装置还包括数据链路控制模块,用于获取所述第一数据链路对应的第一内存空间中存储的当前流量信息;若所述第一内存空间中存储的当前流量信息与cpu中预先保存的所述第一数据链路对应的流量信息相同,关闭所述第一数据链路并清除所述第一数据链路对应的第一内存空间;若所述第一内存空间中存储的当前流量信息与cpu中预先保存的所述第一数据链路对应的流量信息不相同,将cpu中预先保存的所述第一数据链路对应的流量信息更新为所述第一内存空间中存储的当前流量信息。

21、在可选的实施方式中,所述第一数据链路的流量信息包括过包统计信息和字节统计信息。

22、第三方面,本技术提供一种电子设备,包括:处理器、存储器和总线;所述处理器和所述存储器通过所述总线完成相互间的通信;所述存储器存储有可被所述处理器执行的程序指令,所述处理器调用所述程序指令能够执行如前述实施方式任一项所述的方法。

23、第四方面,本技术提供一种计算机可读存储介质,所述计算机可读存储介质上存储有计算机程序指令,所述计算机程序指令被计算机读取并运行时,执行如前述实施方式中任一项所述的方法。

- 还没有人留言评论。精彩留言会获得点赞!