基于UPF的处理器低功耗设计和验证方法与流程

基于upf的处理器低功耗设计和验证方法

技术领域

1.本发明涉及集成电路的低功耗设计与验证技术领域,通过研究集成电路的低功耗设计技术以及upf标准,在逻辑功能描述正确的基础上对soc中的cpu模块进行低功耗设计以降低其功耗,并验证低功耗设计的正确性,特别涉及基于upf的处理器低功耗设计和验证方法。

背景技术:

2.首先,在21世纪的今天,集成电路已经无形之中存在于人们的生活与工作中。人们生活质量的提高,各式各样的消费类电子设备出现在人们的视野中,如智能手机、智能手表、智能手环、平板、电脑、无人机、甚至未来主流的人工智能、汽车电子等。对于这些便携式的电子设备而言,人们对其续航能力的要求越来越高,而电池容量无法无限制增大,这会影响设备的体积与美观,所以低功耗设计在电子产品中变得尤为重要。另外,电子设备的寿命受功耗影响,功耗越低其电池续航越长,则寿命也就越长。越来越多的芯片设计者为了提高其产品的市场占有率与竞争力,低功耗设计成为了其重要指标。

3.同时,低功耗设计也可以降低封装的成本。主流的有塑料封装和陶瓷封装,陶瓷比塑料有更好的导热性,但是其成本也较高,若芯片功耗控制较好,则可以选用廉价的封装技术来降低成本。在一些性能较高的高速工作芯片中(比如电脑的cpu),需要设计专门的散热系统来为芯片降温,保证其性能。所以,低功耗设计对芯片的制造成本也意义重大。

4.最后,低功耗设计对生态环保的好处也日益彰显。如今消费类电子普及率很高,几乎人手一部手机,大多数年轻人还有智能手表、电脑等需求,电子产品消耗的电能急剧增加。若每颗芯片的电能降低lmw/每小时,则数以万亿计的芯片累计的电能也相当庞大,而不管哪种发电方式对生态环境都有或多或少的污染。因此低功耗设计正符合现代绿色、环保、低碳的生活方式。

技术实现要素:

5.针对现有技术的不足,本发明提供了基于upf的处理器低功耗设计和验证方法,通过研究集成电路的低功耗设计技术以及upf标准,在逻辑功能描述正确的基础上对soc芯片中的一个cpu模块进行低功耗设计以降低其功耗,并提供了一种验证方法验证低功耗设计的正确性。

6.本发明通过以下技术方案予以实现:基于upf的处理器低功耗设计和验证方法,包括如下步骤:步骤一:利用upf文件对soc芯片的cpu单元进行低功耗设计;步骤二:利用upf文件对待测的数字逻辑模块的电压域进行供电时序验证。

7.优选的,所述步骤一具体包括:所述upf文件包括电源电压域的描述,供电网络的描述,电源开关的描述,隔离单元的描述以及低功耗状态的描述;

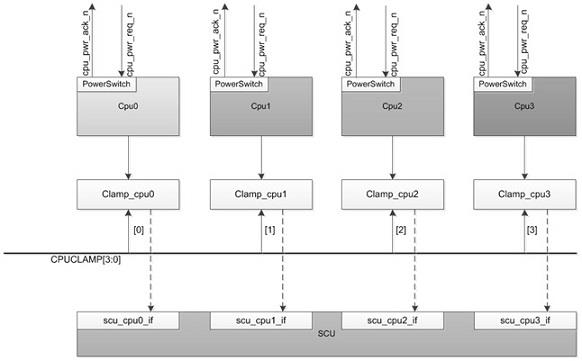

电源电压域的描述:本设计共需要创建五个电压域(power domain),即一个默认常开的电压域,另四个是包含所有内核cpu的可关断电压域;电压域的划分,在完成电源网络搭建之前需要定义全局电压域及其连接关系,确保不同电压域单独供电;所有供电电源共用地线,每个电压域都单独供电,确保每个电压域都能够独立开关电源;电源网络的描述:电源电压域的描述定义了power domain之后,要对各个电压域中的电源网络进行描述,即定义每个电压域的电压端口以及端口和电源线的连接关系;电源开关的描述:即定义soc芯片在进入休眠模式的时候,需要对不工作的模块进行电源切断;隔离单元的描述:soc芯片的某些模块在关断电源之后,cpu其输出信号处于不确定的状态,为了把它们固定在某个电平上,需要加入隔离单元 isolation cell;隔离单元的控制信号由硬件控制,在电源关断之前,首先使隔离单元有效,保证掉电模块的输出固定在一个确定的值上,然后关掉该模块的电源;当模块电源恢复供电后,隔离单元需要维持一段时间再回到无效状态,确保芯片功能的正常;低功耗状态的描述:主要用来描述芯片在不同模式工作下所有电源的状态,并且目前eda工具中的仿真验证工具mvsim与mvrc根据电源状态表来判断upf文件的可行性与完整性,这大大降低了设计的风险性。eda工具可以根据这个低功耗状态表来决定如何插入特殊的低功耗控制单元。

8.优选的,所述步骤二具体包括:利用 rtl 代码与 upf 文件一起做低功耗设计的仿真验证,即 power aware simulation,检查 upf 文件所描述的低功耗设计意图是否正确。目的是为了检查 upf 中对功耗意图的描述是否正确。设计者可以在 rtl 设计阶段结合upf 文件来验证低功耗设计的正确性,检查 upf 文件所描述的低功耗设计意图是否正确,这样能够在设计初期发现问题,大幅度地降低设计的成本和风险。

9.优选的,所述仿真验证流程的步骤如下:1)在编译时增加-upf选项读入upf文件:

“‑

upf upf_file_name”,增加-power_top 选项:

“‑

power_top design_top”;2)在测试平台里添加以下语句给电源上电:initial beginimport upf::*;supply_on("design_test/design_top/vdd_top ", 1.05);supply_on("design_test/design_top/vss", 0.0);end;3)针对于门控电源技术,在测试平台里添加一些功耗控制语句,检查控制信号,如电源开关单元、隔离单元变化后,电路是否按照设计要求正确的工作;4)运行过程与一般的 rtl仿真相同。

10.本发明具有以下有益效果:本发明揭示了一种基于upf的处理器低功耗设计和验证方法,包括:利用upf文件对所述soc芯片的cpu单元的低功耗设计,并在整个集成电路设计流程中都采用这个upf文件所提供的功耗意图,并应用到低功耗的仿真验证流程中,可以快速且完整地描述soc芯片的供电架构,使低功耗验证覆盖到供电架构中的所有电源信号以及相关的控制信号,从而

在很大程度上降低了低功耗设计的复杂度以及风险。

附图说明

11.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

12.图1为本发明的电源开关设计架构图。

13.图2为本发明的低功耗验证仿真流程图。

具体实施方式

14.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

15.实施例一:首先全局电压域划分在upf文件中定义如下:create_power_domain pd_top

ꢀ‑

include_scopecreate_power_domain pd_u_cpu0

ꢀ‑

elements u_cpu0create_power_domain pd_u_cpu1

ꢀ‑

elements u_cpu1create_power_domain pd_u_cpu2

ꢀ‑

elements u_cpu2create_power_domain pd_u_cpu3

ꢀ‑

elements u_cpu3然后对各个电压域中的电源网络进行描述,upf文件中连接关系的定义如下:create_supply_port vdd_topcreate_supply_net vdd_top

ꢀ‑

domain pd_topcreate_supply_net vdd_top

ꢀ‑

domain pd_u_cpu0

ꢀ‑

reusecreate_supply_net vdd_top

ꢀ‑

domain pd_u_cpu1

ꢀ‑

reusecreate_supply_net vdd_top

ꢀ‑

domain pd_u_cpu2

ꢀ‑

reusecreate_supply_net vdd_top

ꢀ‑

domain pd_u_cpu3

ꢀ‑

reuseconnect_supply_net vdd_top

ꢀ‑

ports vdd_topcreate_supply_port vsscreate_supply_net vss

ꢀ‑

domain pd_topcreate_supply_net vss

ꢀ‑

domain pd_u_cpu0

ꢀ‑

reusecreate_supply_net vss

ꢀ‑

domain pd_u_cpu1

ꢀ‑

reusecreate_supply_net vss

ꢀ‑

domain pd_u_cpu2

ꢀ‑

reusecreate_supply_net vss

ꢀ‑

domain pd_u_cpu3

ꢀ‑

reuseconnect_supply_net vss

ꢀ‑

ports vsscreate_supply_net vddcpu_psw0

ꢀ‑

domain pd_u_cpu0

ꢀ‑

resolve parallelcreate_supply_net vddcpu_psw1

ꢀ‑

domain pd_u_cpu1

ꢀ‑

resolve parallel

create_supply_net vddcpu_psw2

ꢀ‑

domain pd_u_cpu2

ꢀ‑

resolve parallelcreate_supply_net vddcpu_psw3

ꢀ‑

domain pd_u_cpu3

ꢀ‑

resolve parallel下一步添加独立的电源开关,如下所示为upf关于不同电压域内的独立的电源开关的整体描述。

16.create_power_switch uswitch_head_cpu0-domain pd_u_cpux-input_supply_port { vdd_top vdd_top }-output_supply_port { vddcpu_pswx }-control_port {cpu_pwr_req u_cpux/cpu_pwr_req}-ack_port {cpu_pwr_ack u_cpux/cpu_pwr_ack {cpu_pwr_req} }-on_state {on_state vdd_top {cpu_pwr_req}}-off_state {off_state vdd_top {!cpu_pwr_req}}在本发明中做低功耗验证仿真流程的主要步骤如下所示:1)在编译时增加-upf选项读入upf文件:

“‑

upfupf_file_name”,增加-power_top 选项:

“‑

power_topdesign_top”。

17.2)在测试平台里添加以下语句给电源上电:initial beginimport upf::*;supply_on("design_test/design_top/vdd_top ", 1.05);supply_on("design_test/design_top/vss", 0.0);end;3)针对于门控电源技术,在测试平台里添加一些功耗控制语句,检查控制信号(如电源开关单元、隔离单元)变化后,电路是否按照设计要求正确的工作。

18.4)运行过程与一般的 rtl仿真相同。

19.下表为本发明的电源状态(或者低功耗状态的描述)描述状态表;以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1