用于专用处理块中的结构化混合精度的系统和方法与流程

本公开总体涉及集成电路(ic)器件,例如可编程逻辑器件(pld)。更具体地,本公开涉及一种能够包括在集成电路器件上的处理块(例如,数字信号处理(dsp)块)以及能够使用该处理块执行的应用。

背景技术:

1、本节旨在向读者介绍可能与本公开各个方面相关的技术的各个方面,这些方面在下文中描述和/或声称。本讨论被认为有助于向读者提供背景信息,以便于更好地理解本公开的各个方面。因此,可以理解,这些陈述是从这个角度解读的,而不是对现有技术的承认。

2、集成电路器件可以用于多种用途或应用,例如机器学习或人工智能(ai)应用。在某些情况下,机器学习和ai架构可能需要大量的计算和处理能力来进行处理。稀疏性(sparsity)可以用于减少执行ai操作所需的计算量。稀疏性可能需要重新训练硬件,这可能很耗时,并且需要大的设备功率输出来实现。替代地,结构化混合精度运算(structuredmixed-precision operation)可以在ai架构中实现。结构化多精度运算(structuredmulti-precision operation)可以在不需要重新训练的情况下重新组织规则的训练网络,同时仍然提供计算和功率节省。

技术实现思路

1、根据本公开的一个实施例,提供了一种用于执行结构化混合精度运算的数字信号处理(dsp)块,包括:多个权重寄存器,可配置为接收和存储第一多个值,其中,所述第一多个值包括第一部分和第二部分,其中:所述第一部分包括所述第一多个值中具有第一精度的一个或多个第一值;并且所述第二部分包括所述第一多个值中具有第二精度的一个或多个第二值;多个乘法器,其中,所述多个乘法器中的每个相应乘法器可配置为接收所述第一多个值中的相应值,其中,所述多个乘法器包括:一个或多个第一乘法器,可配置为执行涉及具有所述第一精度的值的乘法;以及一个或多个第二乘法器,可配置为执行涉及具有所述第二精度的值的乘法;一个或多个输入,可配置为接收第二多个值;复用器网络,可配置为接收所述第二多个值并将所述第二多个值中的每个相应值路由到所述多个乘法器中的乘法器,其中,所述多个乘法器可配置为同时将所述第一多个值中的每个值与所述第二多个值中的相应值相乘,以产生多个乘积;以及加法器电路,可配置为基于所述多个乘积来产生第一和以及第二和。

2、根据本公开的一个实施例,提供了一种集成电路器件,包括用于执行结构化混合精度运算的数字信号处理(dsp)块,所述dsp块包括:多个权重寄存器,可配置为接收和存储第一多个值,其中,所述第一多个值包括第一部分和第二部分,其中:所述第一部分包括所述第一多个值中具有第一精度的一个或多个第一值;并且所述第二部分包括所述第一多个值中具有第二精度的一个或多个第二值;多个乘法器,其中,所述多个乘法器中的每个相应乘法器可配置为接收所述第一多个值中的相应值,其中,所述多个乘法器包括:一个或多个第一乘法器,可配置为执行涉及具有所述第一精度的值的乘法;以及一个或多个第二乘法器,可配置为执行涉及具有所述第二精度的值的乘法;一个或多个输入,可配置为接收第二多个值;复用器网络,可配置为接收所述第二多个值并将所述第二多个值中的每个相应值路由到所述多个乘法器中的乘法器,其中,所述多个乘法器可配置为同时将所述第一多个值中的每个值与所述第二多个值中的相应值相乘,以产生多个乘积;以及加法器电路,可配置为基于所述多个乘积来产生第一和以及第二和。

3、根据本公开的一个实施例,提供了一种用于执行结构化混合精度运算的数字信号处理(dsp)块,包括:多个权重寄存器,可配置为接收和存储第一多个值,其中,所述第一多个值包括第一部分和第二部分,其中:所述第一部分包括所述第一多个值中具有第一精度的一个或多个第一值;并且所述第二部分包括所述第一多个值中具有第二精度的一个或多个第二值;多个乘法器,其中,所述多个乘法器中的每个相应乘法器可配置为接收所述第一多个值中的相应值,其中,所述多个乘法器包括:一个或多个第一乘法器,可配置为执行涉及具有所述第一精度的值的乘法;以及一个或多个第二乘法器,可配置为执行涉及具有所述第二精度的值的乘法;一个或多个输入,可配置为接收第二多个值;多个控制寄存器,可配置为存储第三多个值,其中,所述第三多个值中的值分别指示所述第二多个值中的值是要乘以所述第一多个值的所述第一部分的值还是要乘以所述第一多个值的所述第二部分的值;复用器网络,可配置为:接收所述第二多个值和所述第三多个值;以及基于所述第三多个值中的相应值,将所述第二多个值中的每个相应值路由到所述多个乘法器中的乘法器,其中,所述多个乘法器可配置为同时将所述第一多个值中的每个值与所述第二多个值中的相应值相乘,以产生多个乘积;以及加法器电路,可配置为基于所述多个乘积来产生第一和以及第二和。

技术特征:

1.一种用于执行结构化混合精度运算的数字信号处理(dsp)块,包括:

2.根据权利要求1所述的dsp块,包括多个控制寄存器,可配置为存储第三多个值,其中:

3.根据权利要求2所述的dsp块,其中,所述第三多个值中的值分别指示所述第二多个值中的值是要乘以所述第一多个值的所述第一部分的值还是要乘以所述第一多个值的所述第二部分的值。

4.根据权利要求1所述的dsp块,其中:

5.根据权利要求4所述的dsp块,其中,所述一个或多个第二乘法器不可配置为在具有所述第一精度的值之间执行乘法。

6.根据权利要求4所述的dsp块,其中,所述加法器电路可配置为:

7.根据权利要求6所述的dsp块,其中,所述加法器电路包括:

8.根据权利要求1至7中任一项所述的dsp块,其中:

9.根据权利要求1至7中任一项所述的dsp块,其中:

10.一种集成电路器件,包括用于执行结构化混合精度运算的数字信号处理(dsp)块,所述dsp块包括:

11.根据权利要求10所述的集成电路器件,包括多个控制寄存器,可配置为存储第三多个值,其中:

12.根据权利要求11所述的集成电路器件,其中,所述复用器网络包括多个复用器,每个复用器可配置为:

13.根据权利要求10至12中任一项所述的集成电路器件,其中,所述一个或多个第一值各自包括八位,并且所述一个或多个第二值各自包括少于八位。

14.根据权利要求13所述的集成电路器件,其中,所述一个或多个第二值各自包括一个以上的位。

15.根据权利要求10至12中任一项所述的集成电路器件,其中:

16.根据权利要求10至12中任一项所述的集成电路器件,包括第二dsp块,通信耦合到所述dsp块,并且所述第二dsp块可配置为输出第一输出和第二输出,其中:

17.根据权利要求10所述的集成电路器件,其中,所述集成电路器件包括现场可编程门阵列(fpga)。

18.一种用于执行结构化混合精度运算的数字信号处理(dsp)块,包括:

19.根据权利要求18所述的dsp块,其中:

20.根据权利要求19所述的dsp块,其中:

技术总结

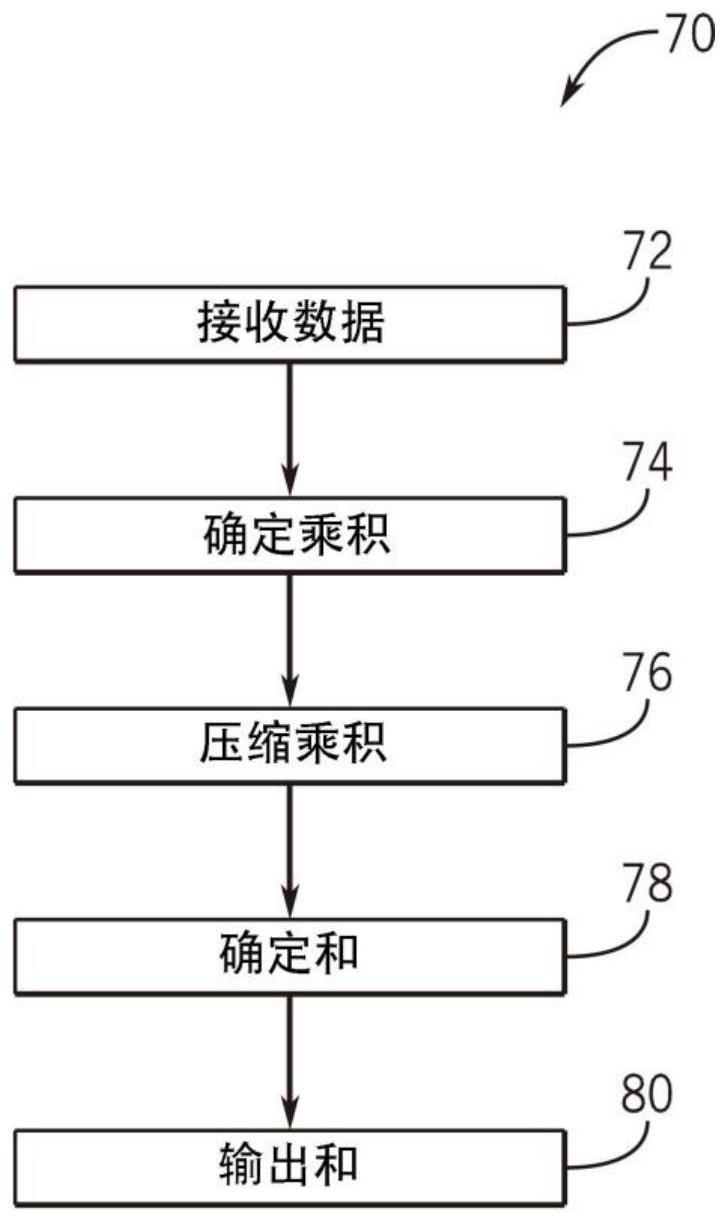

本公开涉及用于专用处理块中的结构化混合精度的系统和方法。本公开涉及数字信号处理(DSP)块,该DSP块包括:多个权重寄存器,可配置为接收和存储具有多个精度的第一多个值;以及多个乘法器,每个乘法器可配置为接收第一多个值中的相应值。DSP块还包括:一个或多个输入,可配置为接收第二多个值;以及复用器网络,可配置为接收第二多个值,并将第二多个值中的每个相应值路由到多个乘法器中的乘法器。乘法器可配置为同时将第一多个值中的每个值与第二多个值中的相应值相乘,以产生多个乘积。此外,DSP块包括加法器电路,可配置为基于多个乘积来产生第一和以及第二和。

技术研发人员:马丁·朗格默,迈克尔·吴,尼哈特·恩金·图纳利

受保护的技术使用者:英特尔公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!