一种抗辐照FPGA内嵌PCIExpressIP核的测试电路和方法与流程

本发明涉及一种抗辐照fpga内嵌pciexpress ip核的测试电路和方法,属于集成电路领域。

背景技术:

1、pciexpress ip核是一种高速通信接口电路,广泛集成在集成电路器件上,满足用户的高带宽和高传输速率需求。通常现场可编程门阵列(即fpga)为代表的可编程逻辑器件(pld)中,内嵌1个或多个相同的pciexpress ip核。

2、fpga内嵌pciexpress ip核功能复杂,规模巨大,是fpga的重要组成部分。为保障器件整体功能正常,避免缺陷产品交付用户,需要对pciexpress ip核进行快速高覆盖率的量产测试,保证其功能正确,同时降低测试时间,减少测试成本。

3、不同于一般的pciexpress ip核,fpga内嵌pciexpress ip核具备可编程的特征,端口分为配置端口和用户端口。首先,fpga内嵌pciexpress ip核增加了大量配置端口。用户定义pciexpressip核功能,生成包含pciexpressip核功能信息的码流文件,通过码流配置fpga,将码流信息存储在sram等配置存储单元中,fpga内嵌pciexpress ip核再通过专门的配置接口读取sram等配置存储单元信息,从而实现可编程功能。其次,fpga内嵌pciexpress ip核的用户端口连接在fpga的互联资源上。fpga内嵌1个或多个pciexpressip核的用户可控制输入和输出端口连接在可编程的fpga互联资源上,用户可通过配置互联资源可将pciexpress ip核的用户端口连接到fpga其他资源或者fpga引脚上。

4、基于以上特征,传统的测试电路如dft、bist电路难以满足fpga内嵌pciexpressip核的测试需求。采用传统可测性设计(即dft)的扫描链测试方法难以实现对pciexpressip核的配置端口相关逻辑的测试,导致测试覆盖率降低,同时在fpga内嵌多个pciexpressip核的情况下测试时间增长。采用传统内建自测试(bist)方法的测试覆盖率低,测试向量多,设计开发复杂,导致测试时间长,测试成本高。

5、中国专利公开号cn 112597009 a,公开日是2021年4月2日,名称为“一种基于覆盖率排行的fpga内嵌pciexpress ip核量产测试方法”中公开了fpga内嵌pciexpress ip核的测试向量集的排序方法,减少了测试向量数量,保持了一定的测试覆盖率,但是未对测试向量集的生成过程进行定义。

技术实现思路

1、本发明所解决的技术问题是:克服现有技术的不足,提供一种抗辐照fpga内嵌pciexpress ip核的测试电路和方法,形成数量较少的高覆盖率测试向量,测试能够实现对fpga内嵌的1个或多个相同的pciexpress ip核的快速、高覆盖率的量产测试,满足器件测试快速、准确、全面的需求。

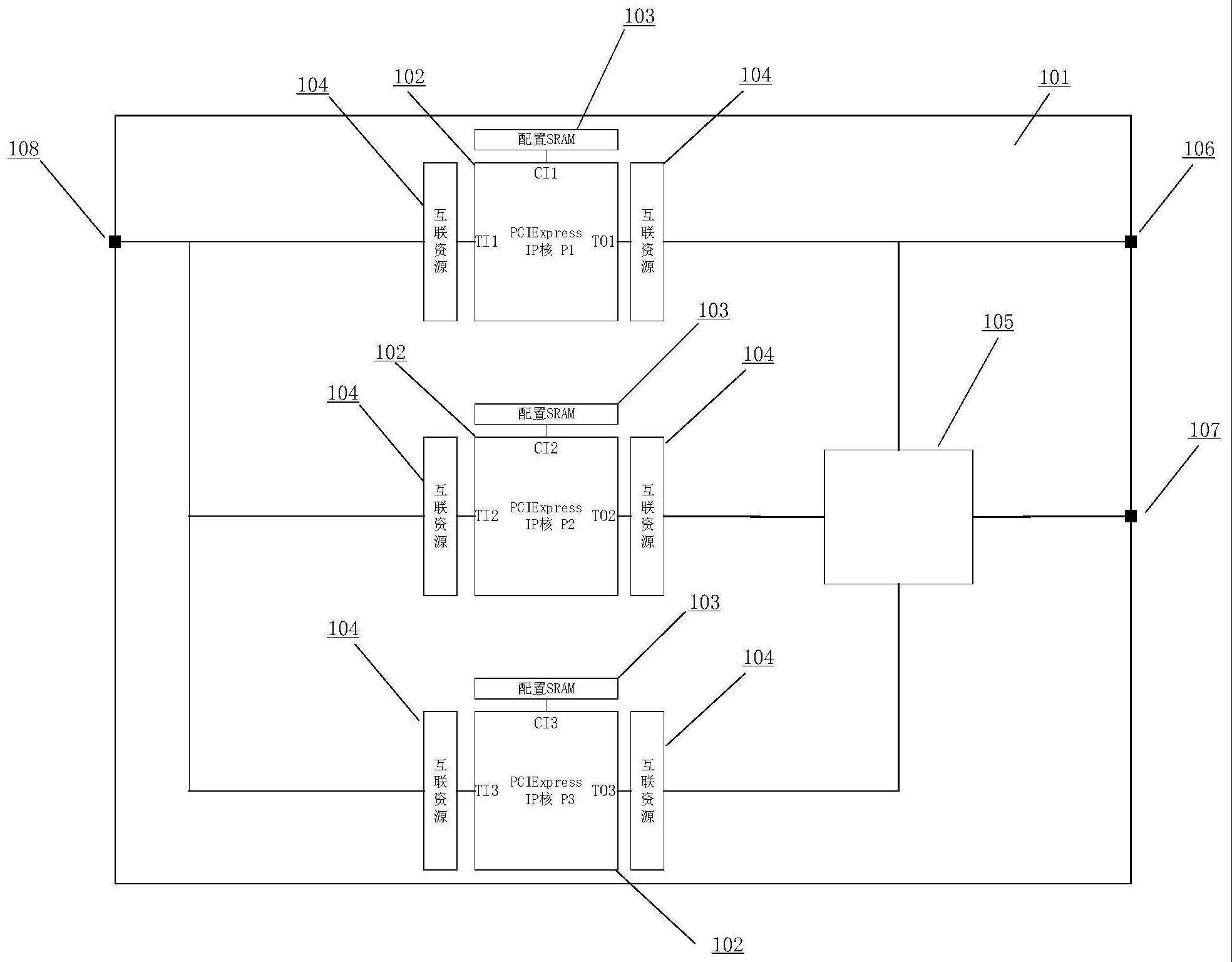

2、本发明的技术方案是:一种抗辐照fpga内嵌pciexpress ip核的测试电路,所述抗辐照fpga内嵌n个被测pciexpress ip核,n大于等于1,该测试电路包括测试用输入管脚tdi、测试用输出管脚tdo、对比模块;

3、测试用输入端口tdi,通过fpga互联资源连接至n个被测pciexpress ip核的测试用输入端口ti;

4、测试用输出管脚tdo,通过fpga互联资源连接至n个被测pciexpress ip核的测试用输出端口to;

5、对比模块,当n为1时,设定测试输出指示信号result恒为1;当n大于1时,按位对比n个被测pciexpress ip核的测试用输出端口to,如果任意被测pciexpress ip核的测试用输出端口to不同,输出result信号为0,否则,输出被测pciexpress ip核的测试用输出端口to为1;

6、测试机台ate,往测试用输入管脚tdi中分两次先后输入不同的测试向量进行测试,如果两次测试中,n个被测pciexpress ip核的测试用输出端口to输出的数据符合预期,且对比模块输出result信号为1,则认为测试通过,否则,认为测试未通过。

7、优选地,所述pciexpress ip核还包括ci端口,用于连接配置sram,配置sram用于存储配置pciexpress ip核的ci端口的初始值。

8、优选地,被测pciexpress ip核的测试用输入端口包括测试复位信号reset、测试时钟tclk[num_clk-1:0]、测试模式信号scanmode、测试使能信号scaneable、测试链输入信号scanin[numsacnin-1:0];

9、num_clk为时钟位数;numsacnin为扫描链个数。

10、优选地,所述被测pciexpress ip核的测试用输出端口包括测试链输出信号scanout[numsacnin-1:0],numsacnout为输出位数。

11、优选地,对比模块采用bist方法设计实现。

12、本发明的另一个技术方案是:一种抗辐照fpga内嵌pciexpress ip核的测试方法,该方法包括如下步骤:

13、s1、建立权利要求1所述的测试电路,设置测试电路中pciexpress ip核配置接口对应的配置存储单元sram为全1;

14、s2、基于步骤s1所建立的测试电路,生成整个fpga的测试配置码流a;

15、s3、基于被测pciexpress ip核门级网表netlist和测试配置码流a对应的pciexpress ip核端口设置,生成测试向量a;

16、s4、将测试配置码流a加载至pciexpress ip核,并按照预设时序向测试用输入管脚tdi输入测试向量a,提取第一result信号,并判断n个被测pciexpress ip核的测试用输出端口to输出的数据是否符合预期;

17、s5、基于步骤s1所建立的测试电路,设置pciexpress ip核配置接口对应的配置存储单元sram为全0;

18、s6、基于步骤s1所建立的测试电路,生成整个fpga的测试配置码流b;

19、s7、基于被测pciexpress ip核门级网表netlist和测试码流b对应的pciexpressip核端口设置,生成测试向量b;

20、s8、将测试配置码流b加载至pciexpress ip核,并按照预设时序向测试用输入管脚tdi输入测试向量b,提取第二result信号,并判断n个被测pciexpress ip核的测试用输出端口to输出的数据是否符合预期;

21、s9、如果第一result信号和第二result信号均为高电平,且n个被测pciexpressip核的测试用输出端口to输出的数据均符合预期,则认为抗辐照fpga内嵌pciexpress ip核测试通过,否则,认为抗辐照fpga内嵌pciexpress ip核测试不通过。

22、优选地,被测pciexpress ip核的测试用输入端口包括测试复位信号reset、测试时钟tclk[num_clk-1:0]、测试模式信号scanmode、测试使能信号scaneable、测试链输入信号scanin[numsacnin-1:0];

23、num_clk为时钟位数;numsacnin为扫描链个数。

24、优选地,所述被测pciexpress ip核的测试用输出端口包括测试链输出信号scanout[numsacnin-1:0],numsacnout为输出位数。

25、优选地,于所述测试向量a和测试向量b采用atpg方法生成。

26、优选地,所述被测pciexpress ip核为经过dft设计的pciexpress ip核。

27、本发明与现有技术相比的优点在于:

28、(1)、本发明针对fpga内嵌pciexpress ip核的可编程特性,设置了了对pciexpress ip核配置端口全1和全0两种测试环境,并通过atpg方法分别生成测试向量,提升了测试覆盖率,同时大幅减少了测试向量数量;

29、(2)、本发明针对fpga内嵌多个pciexpress ip核情况,通过bist方法设计了测试输出端口电路,实现了多个pciexpress ip核的同时测试,缩短了测试时间,降低了测试成本;

30、(3)、本发明pcie内核采用dft扫描测试链测试,外围电路为bist测试,采用基于扫描链测试和bist混合测试方法,相对与传统fpga的bist方式降低了测试向量开发难度,缩短了向量开发时间。

- 还没有人留言评论。精彩留言会获得点赞!