基于信号依赖关系的波形自动对比分析方法、设备和介质与流程

1.本发明涉及芯片技术领域,尤其涉及一种基于信号依赖关系的波形自动对比分析方法、设备和介质。

背景技术:

2.在芯片设计仿真工具的运行结果中,信号的差异往往成千上万,但是这些信号之间的差异往往存在着依赖关系。而现有的eda软件通常仅提供信号波形比较的功能,无法提供自动的波形分析,也无法直观地向用户展示对比结果,现有技术中,芯片设计工程师或验证工程师通常需要花费人工分析这些波形信号的差异来找出导致结果不如预期的根本原因,导致波形分析的成本高、效率低,从而增加了导致芯片设计和芯片验证的成本,降低了芯片设计和芯片验证的效率。

技术实现要素:

3.本发明目的在于,提供一种基于信号依赖关系的波形自动对比分析方法、设备和介质,降低了波形分析的成本,提高了波形分析的效率,进而降低了片设计和芯片验证的成本,提高了芯片设计和芯片验证的效率。

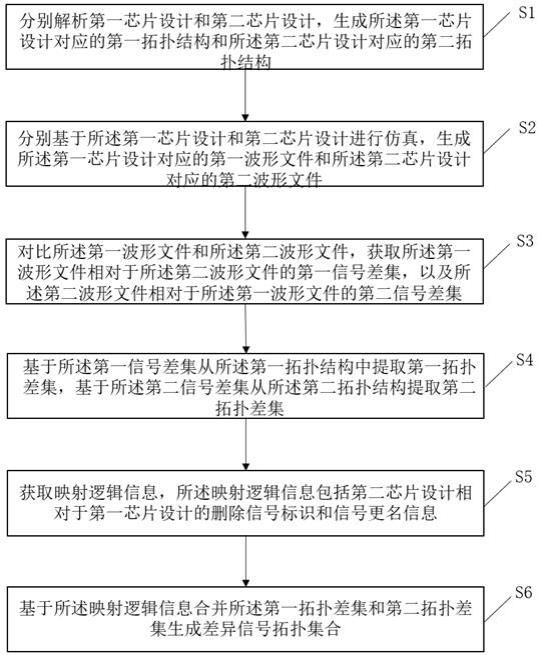

4.根据本发明一方面,提供了一种基于信号依赖关系的波形自动对比分析方法,包括以下步骤:步骤s1、分别解析第一芯片设计和第二芯片设计,生成所述第一芯片设计对应的第一拓扑结构和所述第二芯片设计对应的第二拓扑结构,拓扑结构包括信号节点和信号节点之间的拓扑依赖关系。

5.步骤s2、分别基于所述第一芯片设计和第二芯片设计进行仿真,生成所述第一芯片设计对应的第一波形文件和所述第二芯片设计对应的第二波形文件。

6.步骤s3、对比所述第一波形文件和所述第二波形文件,获取所述第一波形文件相对于所述第二波形文件的第一信号差集,以及所述第二波形文件相对于所述第一波形文件的第二信号差集。

7.步骤s4、基于所述第一信号差集从所述第一拓扑结构中提取第一拓扑差集,基于所述第二信号差集从所述第二拓扑结构提取第二拓扑差集。

8.步骤s5、获取映射逻辑信息,所述映射逻辑信息包括第二芯片设计相对于第一芯片设计的删除信号标识和信号更名信息。

9.步骤s6、基于所述映射逻辑信息合并所述第一拓扑差集和第二拓扑差集生成差异信号拓扑集合。

10.根据本发明另一方面,提供了一种电子设备,包括:至少一个处理器;以及,与所述至少一个处理器通信连接的存储器;其中,所述存储器存储有可被所述至少一个处理器执行的指令,所述指令被设置

为用于执行前述内容所述的方法。

11.根据本发明又一方面,提供了一种计算机可读存储介质,存储有计算机可执行指令,所述计算机可执行指令用于执行前述内容所述的方法。

12.本发明与现有技术相比具有明显的优点和有益效果。借由上述技术方案,本发明提供的一种基于信号依赖关系的波形自动对比分析方法、设备和介质可达到相当的技术进步性及实用性,并具有产业上的广泛利用价值,其至少具有下列优点:本发明能够基于信号依赖关系,根据信号波形自动化地分析信号的差异,并导出逻辑关系图,可以为芯片设计或验证过程节省大量的人工时间,并准确、清晰地为用户展示分析结果,提高了波形分析的效率,降低了波形分析的成本,进而提高了芯片设计或芯片验证的效率。

13.上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,而可依照说明书的内容予以实施,并且为了让本发明的上述和其他目的、特征和优点能够更明显易懂,以下特举较佳实施例,并配合附图,详细说明如下。

附图说明

14.图1为本发明实施例提供的基于信号依赖关系的波形自动对比分析方法流程图;图2(a)为本发明实施例提供的第一拓扑差集示意图;图2(b)为本发明实施例提供的第二拓扑差集示意图;图3为本发明实施例提供的第一拓扑差和第二拓扑差合并示意图。

具体实施方式

15.为更进一步阐述本发明为达成预定发明目的所采取的技术手段及功效,以下结合附图及较佳实施例,对依据本发明提出的一种基于信号依赖关系的波形自动对比分析方法、设备和介质的具体实施方式及其功效,详细说明如后。

16.本发明实施例提供了一种基于信号依赖关系的波形自动对比分析方法,如图1所示,包括以下步骤:步骤s1、分别解析第一芯片设计和第二芯片设计,生成所述第一芯片设计对应的第一拓扑结构和所述第二芯片设计对应的第二拓扑结构,拓扑结构包括信号节点和信号节点之间的拓扑依赖关系。

17.需要说明的是,芯片开发过程中,需要不断地对芯片设计进行调整,并对比调整前后的芯片设计以判断是否达到调整目标,因此,所述步骤s1中的第二芯片设计可以为第一芯片设计调整后的设计。此外,第一芯片设计和第二芯片设计均包括对应的芯片设计代码,例如verilog代码,通过分析芯片设计代码能够解析出芯片设计中对应的信号传递关系,从而得到第一芯片设计和第二芯片设计的完整的信号依赖拓扑结构。

18.步骤s2、分别基于所述第一芯片设计和第二芯片设计进行仿真,生成所述第一芯片设计对应的第一波形文件和所述第二芯片设计对应的第二波形文件。

19.其中,所述步骤s2可以直接基于现有的芯片设计仿真工具实现对第一芯片设计和第二芯片设计的仿真,生成对应的波形文件,在此不再赘述。需要说明的是,波形文件包括芯片设计中每一信号在每一时刻的信号值信息。

20.步骤s3、对比所述第一波形文件和所述第二波形文件,获取所述第一波形文件相对于所述第二波形文件的第一信号差集,以及所述第二波形文件相对于所述第一波形文件的第二信号差集。

21.步骤s4、基于所述第一信号差集从所述第一拓扑结构中提取第一拓扑差集,基于所述第二信号差集从所述第二拓扑结构提取第二拓扑差集。

22.需要说明的是,通过步骤s4能够获取的第一芯片设计相对于第二芯片设计的拓扑差异集合,即第一拓扑差集,以及第二芯片设计相对于第一芯片设计的拓扑差异集合,即第二拓扑差集。

23.所述步骤s4中虽然清楚获取到了第一芯片设计相对于第二芯片设计的拓扑差异集合以及第二芯片设计相对于第一芯片设计的拓扑差异集合,但是,由于芯片规模的庞大,通常情况下,第一拓扑差集和第二拓扑差集中仍有可能存在大量的差异拓扑结构,因此可以通过步骤s5进行进一步处理。

24.步骤s5、获取映射逻辑信息,所述映射逻辑信息包括第二芯片设计相对于第一芯片设计的删除信号标识和信号更名信息。

25.需要说明的是,通常情况下,从第一芯片设计到第二芯片设计,大多数的信号标识和信号拓扑依赖关系不变,只有少部分信号标识会更名,更名即更改信号标识,或者会删除部分无需再关注的信号标识,也可能新增部分信号标识和信号依赖关系。因此,可以预先设置映射逻辑关系,对第一拓扑差集和第二拓扑差集进行进一步化简。

26.步骤s6、基于所述映射逻辑信息合并所述第一拓扑差集和第二拓扑差集生成差异信号拓扑集合。

27.通过步骤s6可以对第一拓扑差集和第二拓扑差集的合集进行进一步化简,从而准确清晰定位到可能出现问题的信号节点,无需通过所有差异波形逐一分析,提高了波形分析的效率,进而提高了芯片设计和芯片验证的效率,同时降低了波形分析的成本,进而降低了芯片设计和芯片验证的成本。

28.作为一种实施例,所述步骤s6之后还包括:步骤s7、基于所述差异信号拓扑集合生成每一差异信号拓扑的逻辑关系图进行显示。

29.通过步骤s7能够将每一差异信号拓扑的逻辑关系图通过示意图渲染等方式在显示界面上进行直观显示,供用户分析。

30.需要说明的是,虽然差异信号通常包括多个,但是基于信号的依赖关系,通常一个差异信号拓扑结构中的差异是由该差异信号拓扑中的根节点引起的,因此,可以对应的根节点突出显示,作为一种实施例,所述步骤s7还包括:步骤s70、将每一差异信号拓扑的逻辑关系图中的根节点进行突出显示。

31.作为一种实施例,所述第一波形文件包括第一芯片设计中所有第一信号节点标识以及每一第一信号节点标识对应的第一波形信息,所述第二波形文件包括第二芯片设计中所有第二信号节点标识以及每一第二信号节点标识对应的第二波形信息,需要说明的是,由于通常情况下,第二芯片设计是基于第一芯片设计的部分修改得到的,因此,第一芯片设计中打第一信号节点标识和第二芯片设计中的第二信号节点标识是相同的,但由于设计的更改,相同的节点信号对应的信号值可能不同,所述步骤s3包括:

步骤s31、判断每一第一信号节点标识是否存在第二波形文件中,若不存在,则将该第一信号节点标识存储至第一信号差集中,否则,执行步骤s32。

32.步骤s32、则判断该第一信号节点标识在第一波形文件中对应的第一波形信息和在第二波形文件中对应的第二波形信息是否相同,若不相同,则将该第一信号节点标识存储至第一信号差集中,生成所述第一信号差集。

33.步骤s33、判断每一第二信号节点标识是否存在第一波形文件中,若不存在,则将该第二信号节点标识存储至第二信号差集中,否则,执行步骤s34。

34.步骤s34、则判断该第二信号节点标识在第二波形文件中对应的第二波形信息和在第一波形文件中对应的第一波形信息是否相同,若不相同,则将该第二信号节点标识存储至第二信号差集中,生成所述第二信号差集。

35.通过步骤s31-步骤s34能够快速准确获取到第一芯片设计相对于第二芯片设计的差异信号标识,以及第二芯片设计相对于第一芯片设计的差异信号标识。

36.作为一种实施例,所述步骤s4包括:步骤s41、从所述第一拓扑结构中提取第一信号差集中的第一信号节点标识对应的信号节点,以及第一信号差集中的第一信号节点之间的拓扑依赖关系,生成所述第一拓扑差集。

37.步骤s42、从所述第二拓扑结构中提取第二信号差集中的第二信号节点标识对应的信号节点,以及第二信号差集中的第二信号节点之间的拓扑依赖关系,生成所述第二拓扑差集。

38.通过步骤s41-步骤s42获取第一拓扑差集和第二拓扑差集,能够便于通过差异信号拓扑依赖关系定位需要分析的差异信号,提高波形分析的效率。

39.作为一种实施例,所述步骤s6包括:步骤s61、根据所述删除信号标识将所述第一拓扑差集中对应的信号节点删除。

40.需要说明的是,从第一芯片设计更新为第二芯片设计的过程中,存在部分不需要再关注的信号,因此可以基于已知的已删除的信号标识将所述第一拓扑差集中对应的信号节点删除,从而滤除噪声,提高波形分析的效率。

41.步骤s62、根据所述信号更名信息,确定所述第一拓扑差集和第二拓扑差集中相同的信号节点,将所述第一拓扑差集和第二拓扑差集中相同的拓扑结构进行合并,生成所述差异信号拓扑集合。

42.需要说明的是,通过将更名的信号标识统一,能够准确合并第一拓扑差集和第二拓扑差集中相同的拓扑结构,提高波形分析的效率和准确性。

43.映射逻辑信息可以预先根据设计的更改设计好,但可能存在遗漏等情况,因此,可以基于差异信号拓扑的逻辑关系图,更新映射逻辑信息。作为一种实施例,所述步骤s31中,若第一信号节点标识不存在第二波形文件中,则为该第一信号节点标识设置第一提示标识;所述步骤s33中,若第二信号节点标识不存在第一波形文件中,则为该第二信号节点标识设置第二提示标识。

44.所述步骤s6之后还包括:步骤s71、基于所述差异信号拓扑集合生成每一差异信号拓扑的逻辑关系图进行显示,并在显示界面上标注节点对应的第一提示标识和第二提示标识;

步骤s72、基于差异信号拓扑的逻辑关系图上标注的第一提示标识和第二提示标识更新所述映射逻辑信息,并返回步骤s5。

45.通过更新映射逻辑信息,可以进行多次迭代,得到准确的拓扑的逻辑关系图,提高波形分析的效率和准确性。

46.以下通过一个具体示例来进一步说明本发明,假设通过步骤s3得到的第一信号差集为{a2,a11,a12,a40,a41},第二信号差集为{a2,a76,a40,a41,a51},通过步骤s4得到的第一拓扑差集如图2(a)所示,第二拓扑差集如图2(b)所示。需要说明的是,为了便于说明本发明,本示例简化处理,仅列举了少量数据进行说明,实际应用中,第一信号差集、第二信号差集、第一拓扑差集、第二拓扑差集中的元素可能比本示例中的多。进一步的,假设步骤s5中,映射逻辑信息包括“a12 removed”、“a11=》a76

”ꢀ

,

ꢀ“

a12 removed”表示从第一芯片设计到第二芯片设计过程中,将a12删除。“a11=》a76

”ꢀ

,表示从第一芯片设计到第二芯片设计过程中,将a11更名为a76,基于此映射逻辑信息进行合并,生成差异信号拓扑集合,如图3所示。可以理解的是,差异信号拓扑集合的逻辑关系图进行显示时,可以标注根节点,第二提示标识信息等,更加直观展示逻辑关系图。

47.需要说明的是,一些示例性实施例被描述成作为流程图描绘的处理或方法。虽然流程图将各步骤描述成顺序的处理,但是其中的许多步骤可以被并行地、并发地或者同时实施。此外,各步骤的顺序可以被重新安排。当其操作完成时处理可以被终止,但是还可以具有未包括在附图中的附加步骤。处理可以对应于方法、函数、规程、子例程、子程序等等。

48.本发明实施例还提供一种电子设备,包括:至少一个处理器;以及,与所述至少一个处理器通信连接的存储器;其中,所述存储器存储有可被所述至少一个处理器执行的指令,所述指令被设置为用于执行本发明实施例所述的方法。

49.本发明实施例还提供一种计算机可读存储介质,所述计算机指令用于执行本发明实施例所述的方法。

50.本发明实施例能够基于信号依赖关系,根据信号波形自动化地分析信号的差异,并导出逻辑关系图,可以为芯片设计或验证过程节省大量的人工时间,并准确、清晰地为用户展示分析结果,提高了波形分析的效率,降低了波形分析的成本,进而提高了芯片设计或芯片验证的效率。

51.以上所述,仅是本发明的较佳实施例而已,并非对本发明作任何形式上的限制,虽然本发明已以较佳实施例揭露如上,然而并非用以限定本发明,任何熟悉本专业的技术人员,在不脱离本发明技术方案范围内,当可利用上述揭示的技术内容作出些许更动或修饰为等同变化的等效实施例,但凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化与修饰,均仍属于本发明技术方案的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1