基于PSoC芯片的神经网络实时图像识别系统及方法与流程

本发明涉及智能图像识别,特别涉及一种基于psoc(programmablesystem-on-chip,可编程系统级芯片)芯片的神经网络实时图像识别系统及方法。

背景技术:

1、随着人工智能技术的发展,深度卷积神经网络已经广泛应用于图像识别、语音识别、模式分析、预测估计等场景,成功的解决了许多传统算法难以解决的实际问题。其强大的特征学习能力、多自由度的网络结构,决定了深度卷积神经网络算法具有计算密集、更新迭代速度快等特点。

2、考虑到通用图形处理器gpu的功耗壁垒,目前卷积神经网络边缘计算硬件平台主要有通用处理器(cpu)、专用集成电路(asic,application specific integratedcircuit)、现场可编程逻辑门阵列(fpga),其基本设计思想为可编程、可通用、可重构。鉴于通用cpu相对较低的性能功耗比,asic的高昂的研发成本与时间滞后性,如何高效的实现神经网络算法已成为行业的迫切需求。fpga具有配置灵活、高度并行、高能效比等优势,对于部分市场变化迅速的行业非常适用。同时,fpga器件中也可以逐渐增加dsp核(dsp digitalsingnal processor数字信号处理器)、arm核(advanced risc machines,risc reducedinstruction set computer精简指令集计算机)、ai(artificial intelligence人工智能)硬核等模块形成可重构psoc,以实现更为复杂的网络算法。如何结合psoc芯片特点与深度卷积神经网络计算模型的并行性和流水型,充分利用片上有限资源进行高效的协同部署仍是亟待解决的问题。

技术实现思路

1、本发明的目的是提供一种基于psoc芯片的神经网络实时图像识别系统及方法,能够充分挖掘psoc芯片中ai加速硬核的计算资源,同时结合深度卷积神经网络模型计算过程中潜在的并行性和流水型,配合片上可编程逻辑资源进行响应,合理高效的进行软硬件部署,能够高性能、低功耗的实现深度卷积神经网络的图像识别。

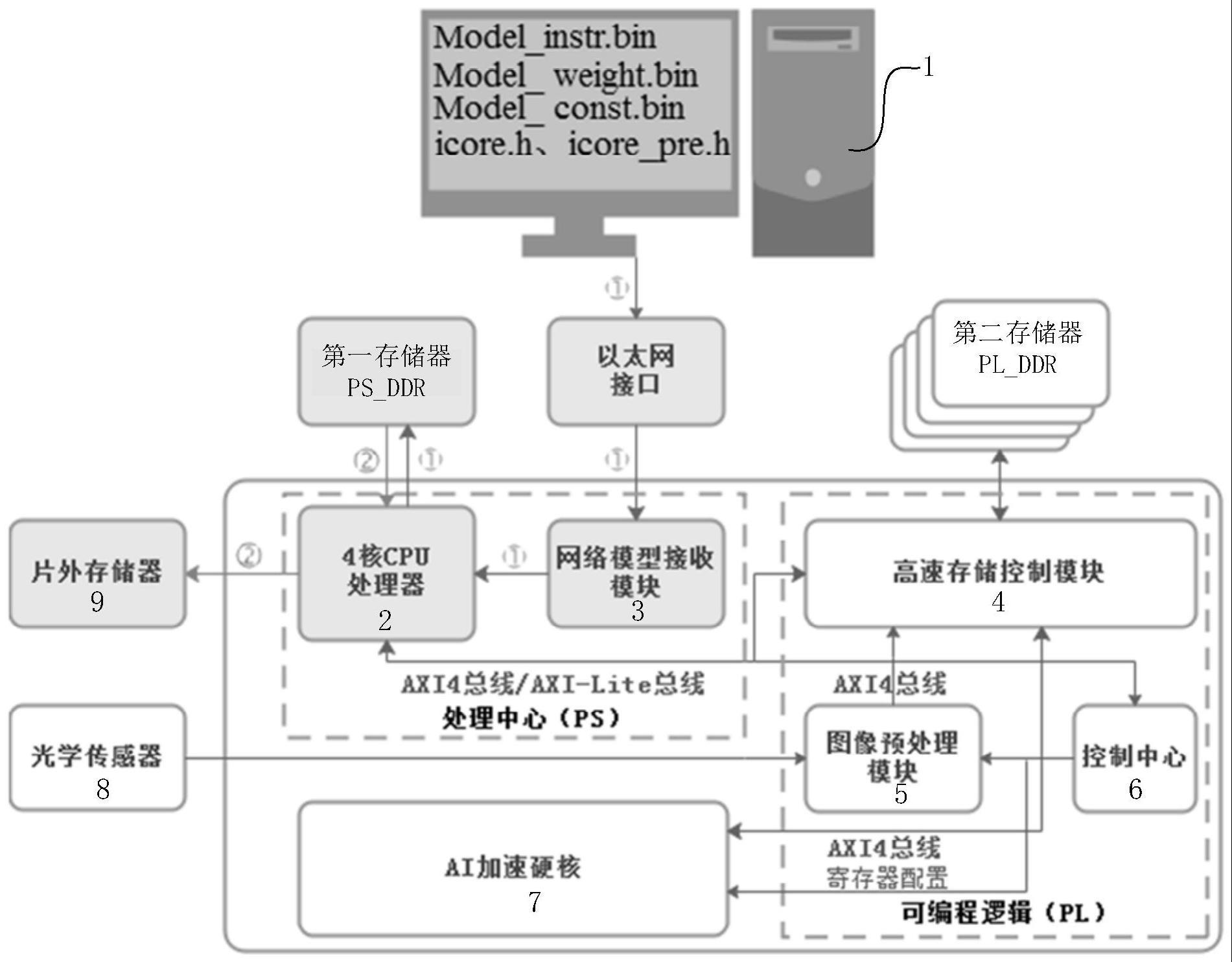

2、为了达到上述目的,本发明提供一种基于psoc芯片的神经网络实时图像识别系统,包含:psoc异构多核处理器、网络模型接收模块、第一存储器、第二存储器;所述psoc异构多核处理器包含:cpu处理器、ai加速硬核和fpga模块;

3、所述网络模型接收模块用于接收上位机发送的配置信息,并通过所述cpu处理器缓存至第一存储器中;所述配置信息包含:指令文件,用于指示卷积神经网络模型程序代码中函数的运算步骤;第一数据文件,其包含卷积神经网络模型的各层网络的权重参数;第一配置文件,用于配置所述ai加速硬核;第二配置文件,其定义了对图像数据进行预处理的参数;

4、所述fpga模块包含:图像预处理模块、高速存储控制模块;

5、所述图像预处理模块接收外部采集的图像数据,并基于所述第二配置文件对接收的图像数据进行预处理;

6、所述高速存储控制模块将预处理后的图像数据缓存至所述第二存储器中;高速存储控制模块还通cpu处理器获取第一存储器中的配置信息并缓存至第二存储器中;

7、所述ai加速硬核通过高速存储控制模块获取第二存储器中的配置信息及预处理后的图像数据,基于所述配置信息对图像数据进行识别,并将识别结果缓存至第二存储器;通过高速存储控制模块将第二存储器中的识别结果发送给cpu处理器。

8、可选的,所述的基于psoc芯片的神经网络实时图像识别系统还包含控制中心;所述控制中心包含:图像预处理控制器、高速存储控制器、状态监控器;

9、cpu处理器通过所述高速存储控制器为高速存储控制模块配置从第二存储器读取数据的指令、地址、数据长度,以及向第二存储器写入数据的指令、地址、数据长度;cpu处理器通过所述高速存储控制器为高速存储控制模块配置从第一存储器读取数据的指令、地址、数据长度,以及向第一存储器写入数据的指令、地址、数据长度;

10、所述状态监控器用于启动ai加速硬核,回读ai加速硬核的多个状态,所述多个状态包含:启动状态、待注入配置文件状态、待注入图像数据状态、图像数据识别完成状态;状态监控器基于回读的启动状态、待注入配置文件状态、待注入图像数据状态触发ai加速硬核获取第二存储器中的预处理后的图像数据、配置信息,基于回读的图像数据识别完成状态触发ai加速硬核向第二存储器发送已识别的图像数据;

11、所述图像预处理控制器基于所述启动状态触发图像预处理模块从第二存储器获取第二配置文件、向第二存储器写入预处理后的图像数据,基于所述启动状态、图像数据识别完成状态触发图像预处理模块接收外部采集的图像数据。

12、可选的,ai加速硬核内包含多个状态寄存器;状态监控器通过所述状态寄存器回读ai加速硬核对应的状态。

13、可选的,所述基于psoc芯片的神经网络实时图像识别系统还包含片外存储器,其为非易失性存储器;cpu处理器还将所述配置信息烧写至所述片外存储器中;第一、第二存储器为易失性存储器;cpu处理器在所述图像识别系统上电时,将片外存储器中的配置信息缓存至第一存储器和第二存储器。

14、可选的,所述状态监控器还在所述图像识别系统上电完成后,比对所述第一存储器、片外存储器中的配置信息,以判断第一存储器加载配置信息是否出现错误。

15、可选的,高速存储控制模块包含:

16、第一存储器访问模块,通信连接cpu处理器,用于获取cpu处理器配置的从第一存储器读取数据的指令、地址、数据长度,以及向第一存储器写入数据的指令、地址、数据长度;

17、第二存储器访问模块,通信连接cpu处理器,用于获取cpu处理器配置的从第二存储器读取数据的指令、地址、数据长度,以及向第二存储器写入数据的指令、地址、数据长度;

18、数据交互模块,包含:第一存储器数据缓存模块、第二存储器数据缓存模块、交互状态机;所述第一存储器数据缓存模块、第二存储器数据缓存模块分别用于缓存从第一存储器、第二存储器中读入的数据;所述交互状态机用于交换第一存储器数据缓存模块、第二存储器数据缓存模块读入的数据;

19、第二存储器读写控制器,用于根据cpu处理器配置的从第二存储器读取数据的指令、地址、数据长度,从第二存储器读入数据并缓存至第二存储器数据缓存模块;第二存储器读写控制器还根据cpu处理器配置的向第二储器写入数据的指令、地址、数据长度,将第二存储器数据缓存模块中的已交换数据写入第二存储器中。

20、可选的,所述基于psoc芯片的神经网络实时图像识别系统还包含:第一存储器读写控制器,通信连接所述第一存储器访问模块、数据交互模块;

21、所述第一存储器读写控制器用于根据cpu处理器配置的从第一存储器读取数据的指令、地址、数据长度,从第一存储器读入数据并缓存至第一存储器数据缓存模块;第一存储器读写控制器还根据cpu处理器配置的向第一存储器写入数据的指令、地址、数据长度,将第一存储器数据缓存模块中的已交换数据写入第一存储器中。

22、可选的,cpu处理器还对图像数据中已识别的图像信息进行加框处理,并将加框处理后的图像数据转换为hdmi格式,发送给显示器进行可视化显示。

23、本发明还提供一种实时图像识别方法,采用如本发明所述的基于psoc芯片的神经网络实时图像识别系统实现的,包含步骤:

24、s1、网络模型接收模块接收上位机发送的配置信息,通过cpu处理器缓存至第一存储器中;通过高速存储控制模块获取第一存储器中的配置信息并缓存至第二存储器中;

25、s2、图像预处理模块接收外部采集的图像数据,基于配置信息对采集的图像数据进行预处理,并将预处理后的图像数据缓存至第二存储器中;

26、s3、控制中心启动ai加速硬核,触发ai加速硬核从第二存储器中获取配置信息和图像数据;ai加速硬核基于获取配置信息,通过深度卷积神经网络对图像数据进行识别,并将已识别的图像数据存储至第二存储器;

27、s4、通过高速存储控制模块将第二存储器中已识别图像数据发送第一存储器;cpu对第一存储器中的已识别图像数据中的图像信息进行加框,并转换为hdmi格式,提供给显示器进行可视化的显示。

28、可选的,步骤s1中,cpu处理器通过控制中心为高速存储控制模块配置从第一存储器读取数据的指令、地址、数据长度,以及向第二存储器写入数据的指令、地址、数据长度;通过控制中心触发高速存储控制模块从第一存储器中读取配置信息并写入第二存储器;

29、步骤s2中,当控制中心读取到ai加速硬核已经完成一帧图像数据的识别,控制中新模块触发图像预处理模块接收外部采集的新的一帧图像;

30、数据步骤s4中,控制中心基于cpu处理器为高速存储控制模块配置从第二存储器读取数据的指令、地址、数据长度,以及向第一存储器写入数据的指令、地址、数据长度,触发高速存储控制模块从第二存储器中读取已识别的图像数据并写入第一存储器。

31、与现有技术相比,本发明的基于psoc芯片的神经网络实时图像识别系统及方法的有益效果在于:

32、1)本发明的识别系统通过注入与深度卷积神经网络算法对应的配置信息,并通过ai加速硬核基于该配置信息对图像数据进行识别,完成了深度卷积神经网络算法的实时嵌入式实现,且不受网络算法类型的限制。本发明中ai加速硬核的利用率超过80%,平均计算算力达到1.6tops。相比于传统的通过cpu处理器识别图像数据,本发明大大提高了智能图像识别的速度并降低了计算成本。

33、2)本发明识别系统的控制逻辑由控制中心基于实时回读的ai加速硬核状态来实现,控制中心也作为调度中心,通过控制中心启动ai加速硬核、触发图像预处理模块接收新的一帧图像数据、触发ai加速硬核从第二存储器读入图像数据和配置信息、触发高速存储控制模块读取第一存储器的配置信息并缓存至第二存储器、触发高速存储控制模块读取第二存储器的已识别图像数据并缓存至第一存储器。本发明的控制逻辑高效,由于不需要由cpu处理器实现控制逻辑,大大减轻了cpu处理器的负担,并提高了数据处理速度。

34、3)本发明中,读/写第一存储模块、第二存储模块的指令、起始地址、数据长度均由cpu处理器配置,高速存储控制模块通过不同的接口与第一、第二存储器通信,并在高速存储控制模块内实现第一存储模块、第二存储模块之间的数据交换,大大提高了系统内部数据的传输效率。

35、4)进一步,本发明具备指令的扩展性,可以通过cpu处理器快速开发额外的运算单元来进行辅助计算,以支持新的深度卷积神经网络。

- 还没有人留言评论。精彩留言会获得点赞!