芯片的数据访问错误的处理方法及相关产品与流程

本申请涉及电子,尤其涉及一种芯片的数据访问错误的处理方法及相关产品。

背景技术:

1、芯片中的杂项控制模块(miscellaneous control module,简称mcm)为芯片提供杂项的控制功能,但是现有的芯片的mcm写数据的位宽仅支持32位,非32位访问会出现错误,导致寄存器异常。

技术实现思路

1、本申请实施例公开了一种芯片的数据访问错误的处理方法及相关产品,该方法可以避免非32位访问的寄存器异常,提高芯片的安全性。

2、第一方面,提供一种芯片的数据访问错误的处理方法,所述方法包括如下步骤:

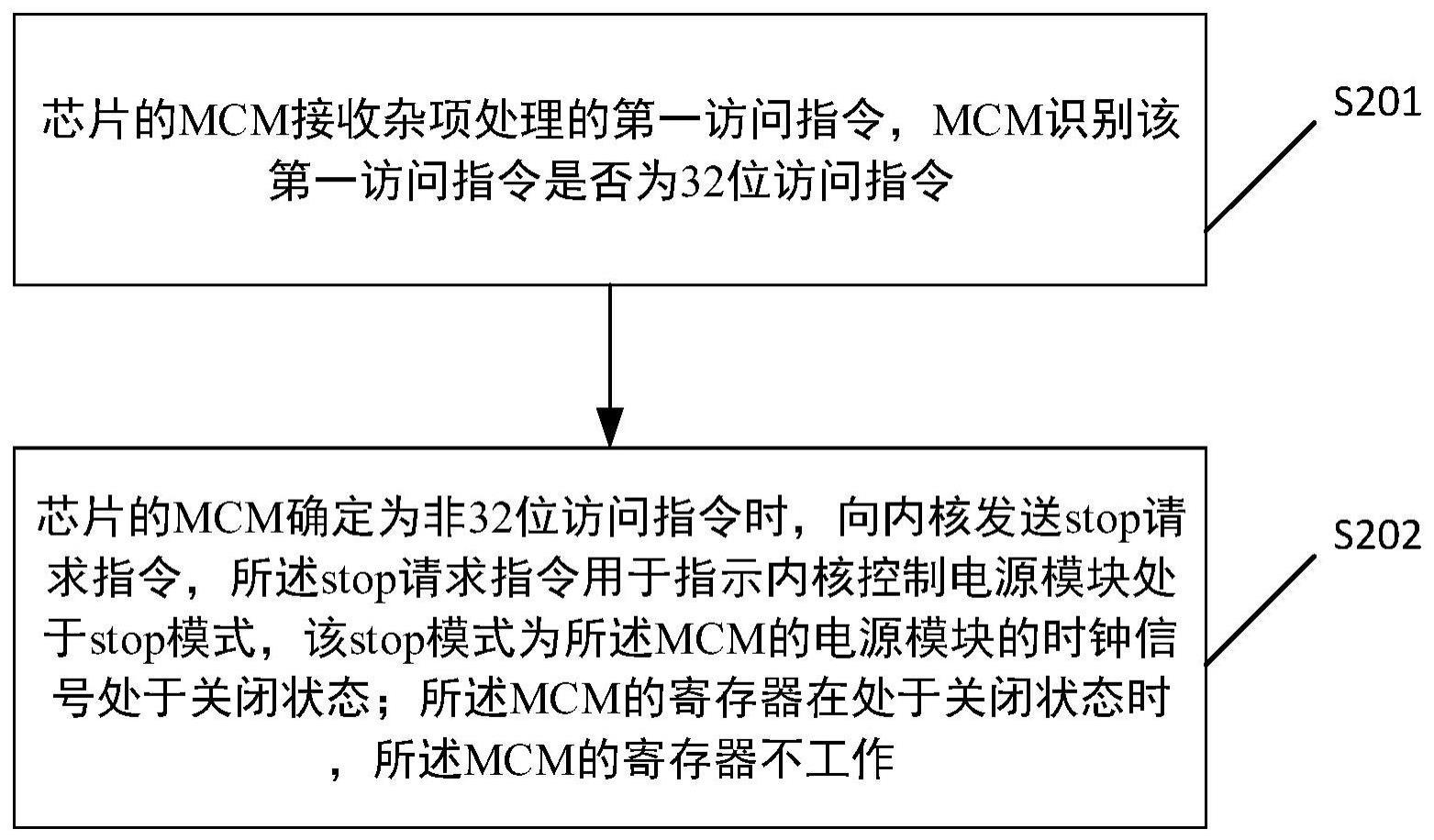

3、芯片的mcm接收杂项处理的第一访问指令,mcm识别该第一访问指令是否为32位访问指令;

4、芯片的mcm确定为非32位访问指令时,向内核发送stop请求指令,所述stop请求指令用于指示内核控制电源模块处于stop模式,该stop模式为所述mcm的电源模块的时钟信号处于关闭状态;所述mcm的寄存器在处于关闭状态时,所述mcm的寄存器不工作。

5、第二方面,提供一种芯片的数据访问错误的处理系统,所述系统应用于芯片,所述芯片包括:mcm、内核和嵌套向量中断控制器,内核分别与mcm以及嵌套向量中断控制器连接,所述系统包括:

6、mcm,用于接收杂项处理的第一访问指令,mcm识别该第一访问指令是否为32位访问指令;

7、mcm,还用于确定为非32位访问指令时,向内核发送stop请求指令,所述stop请求指令用于指示内核控制电源模块处于stop模式,该stop模式为所述mcm的电源模块的时钟信号处于关闭状态;所述mcm的寄存器在处于关闭状态时,所述mcm的寄存器不工作。

8、第三方面,提供一种电子设备,包括处理器、存储器、通信接口,以及一个或多个程序,所述一个或多个程序被存储在所述存储器中,并且被配置由所述处理器执行,所述程序包括用于执行第一方面所述的方法中的步骤的指令。

9、第四方面,提供了一种计算机可读存储介质,存储用于电子数据交换的计算机程序,其中,所述计算机程序使得计算机执行第一方面所述的方法。

10、第五方面,提供了一种计算机程序产品,其中,上述计算机程序产品包括存储了计算机程序的非瞬时性计算机可读存储介质,上述计算机程序可操作来使计算机执行如本申请实施例第一方面中所描述的部分或全部步骤。该计算机程序产品可以为一个软件安装包。

11、本申请提供的技术方案mcm接收杂项处理的第一访问指令,mcm识别该第一访问指令是否为32位访问指令;mcm确定为非32位访问指令时,向内核发送stop请求指令,所述stop请求指令用于指示内核控制电源模块处于stop模式,该stop模式为所述mcm的电源模块的时钟信号处于关闭状态;所述mcm的寄存器在处于关闭状态时,所述mcm的寄存器不工作,这样在非32位访问指令时,通过发送对应的stop请求指令让内核控制电源模块将其处于stop状态,进而关闭寄存器,避免了寄存器出现错误,避免非32位访问的寄存器异常,提高芯片的安全性。

技术特征:

1.一种芯片的数据访问错误的处理方法,其特征在于,所述方法包括如下步骤:

2.根据权利要求1所述的方法,其特征在于,所述方法还包括:

3.根据权利要求1所述的方法,其特征在于,所述方法还包括:

4.根据权利要求3所述的方法,其特征在于,所述依据仲裁配置来确定执行前门指令和后门指令的执行顺序具体包括:

5.根据权利要求1所述的方法,其特征在于,所述方法还包括:

6.根据权利要求5所述的方法,其特征在于,所述获取该中断指令对应的第一任务的第一优先级具体包括:

7.根据权利要求5所述的方法,其特征在于,所述依据该比较结果确定是否向内核发送中断嵌套指令具体包括:

8.一种芯片的数据访问错误的处理系统,所述系统应用于芯片,其特征在于,所述芯片包括:mcm、内核和嵌套向量中断控制器,内核分别与mcm以及嵌套向量中断控制器连接,所述系统包括:

9.一种电子设备,包括处理器、存储器、通信接口,以及一个或多个程序,所述一个或多个程序被存储在所述存储器中,并且被配置由所述处理器执行,所述程序包括用于执行如权利要求1-7任意一项所述的方法的步骤的指令。

10.一种计算机可读存储介质,所述计算机可读存储介质中存储有计算机程序,当其在计算机设备上运行时,执行如权利要求1-7任意一项所述的方法。

技术总结

本申请实施例提供一种芯片的数据访问错误的处理方法及相关产品,所述方法包括:芯片的MCM接收杂项处理的第一访问指令,MCM识别该第一访问指令是否为32位访问指令;芯片的MCM确定为非32位访问指令时,向内核发送stop请求指令,所述stop请求指令用于指示内核控制电源模块处于stop模式,该stop模式为所述MCM的电源模块的时钟信号处于关闭状态;所述MCM的寄存器在处于关闭状态时,所述MCM的寄存器不工作。本申请提供的技术方案具有安全性高的优点。

技术研发人员:陈婷,黄志文,师广涛

受保护的技术使用者:深圳曦华科技有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!