一种结构化的芯片设计架构与方法与流程

本发明涉及芯片的低功耗设计,具体涉及一种soc芯片系统和/或ip模块结构化的低功耗设计架构与方法。

背景技术:

1、随着移动设备的越来越流行,电池的容量发展速度的限制以及人们对绿色环保的要求越来越高,研究芯片的超低功耗设计架构与方法越来越受到人们的重视。

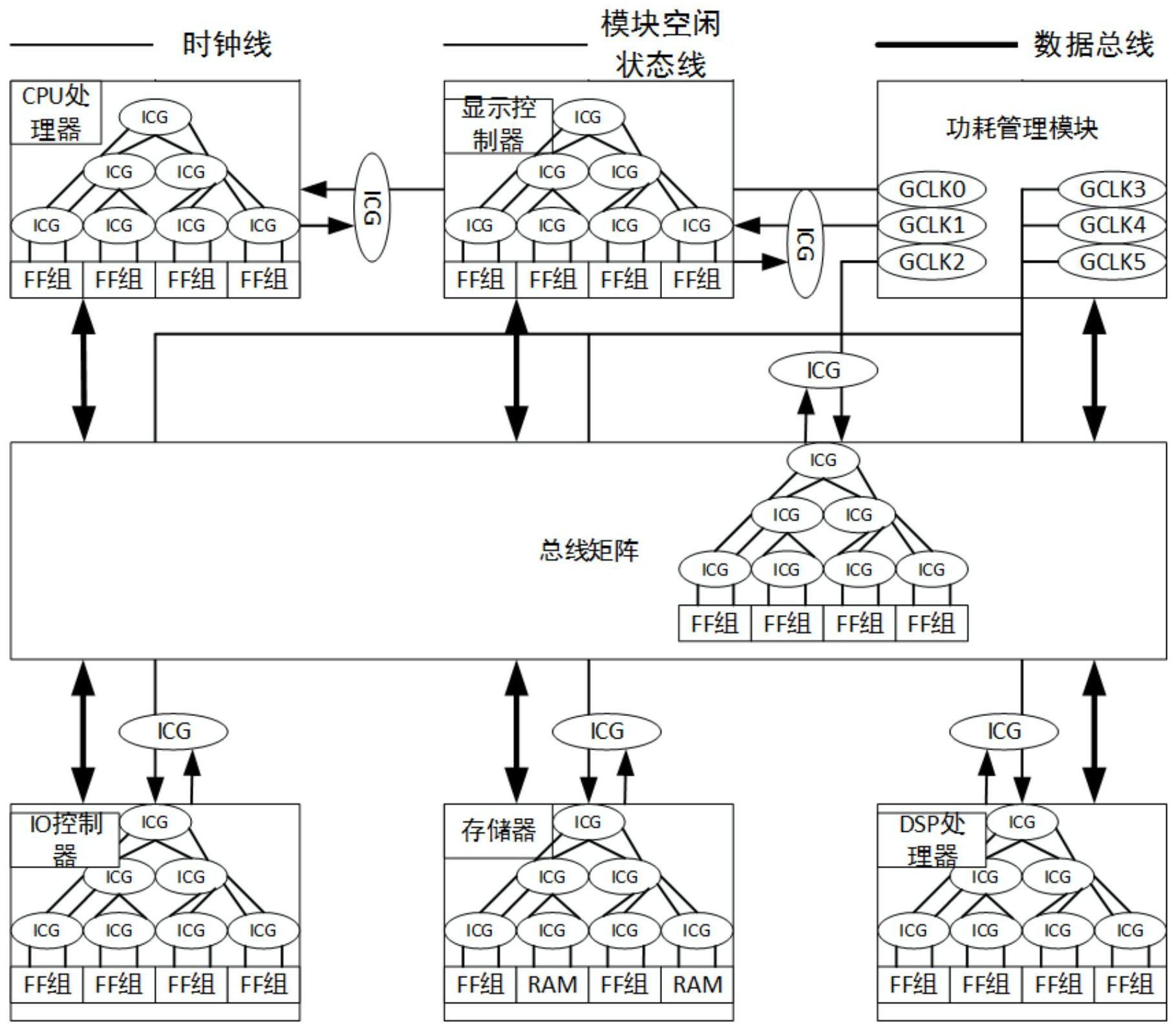

2、优异的超低功耗设计不仅能改善芯片因发热而导致的可靠性问题,降低对芯片封装的散热要求,降低对冷却系统的要求,也意味着系统成本的降低。众所周知,超低功耗设计方法有很多种,根据经验统计时钟功耗占了整个系统60%左右的功耗,传统上优化时钟功耗的方法包括:一、在功耗管理模块中的时钟管理部分为每个ip模块(如图1的cpu处理器模块、显示控制器模块等等)分别产生一个或多个时钟(如图1的gclk0、gclk1等)送给对应的模块,当对应的模块不工作时,由软件来关闭对应的模块所对应的时钟,来降低此模块不使用时的功耗;二、利用逻辑综合工具自动根据寄存器组(ff组)的逻辑条件状态分组插入时钟门控单元(icg)到对应的寄存器组的前面(如图3所示),来降低这些寄存器组(ff组)的功耗。

3、在芯片的物理实现的时钟树综合时,因物理电路扇出(fanout)的负载数值限制(一个时钟电路单元只能推一定数目的下一级的时钟电路单元)及时序平衡(balance)的要求(从时钟的起点到每个寄存器时钟端口(pin)的延迟尽可能相等),经时钟树综合以后,整个时钟网络会变成一个倒立的树形结构(如图2所示,图2只示出了cpu处理器模块的时钟树示意图,其他模块类似),从图2可知,因时钟树综合而插入的大量的时钟缓冲器(buf)是一直在切换(toggle)而消耗功耗,当soc芯片或ip模块的ff组(寄存器组)的数量越多,所需的时钟buf也越多,这些未受控的时钟buf所消耗的功耗也越大。

4、现有技术一直没有提出能够解决因时钟树综合所插入的大量时钟buf消耗大量功耗的问题的技术方案。

技术实现思路

1、本发明旨在提供一种结构化的芯片设计架构与方法,以解决现有技术中由于时钟树综合所插入的大量时钟buf消耗大量功耗的问题。

2、本发明的目的是解决现有技术的不足,提供一种结构化的芯片设计架构,包括切分组件、空闲状态信号增加组件、时钟产生组件和时钟树综合组件;所述的切分组件用于对所述芯片的各个ip模块的各个子模块做合适的模块切分及层级切分;所述的空闲状态信号增加组件用于对每个子模块增加模块空闲状态信号;所述的时钟产生组件用于在每个子模块前调用时钟门控单元,根据所对应的模块空闲状态信号产生门控的时钟并送给对应的子模块;所述的时钟树综合组件用于在时钟树综合时,按分段长时钟树的思想,从时钟门控单元的时钟输出段长时钟树。

3、优选地,所述的合适的模块切分具体是指将功能近似的子模块合并在同一个模块,并限制每个子模块的寄存器组ff组的数量到200。

4、优选地,所述的层级切分具体是指按逻辑功能嵌套的规则对各个子模块分多级子模块嵌套。

5、优选地,对于里面有嵌套多个子模块的模块,模块的空闲状态信号是其内部的多个子模块的空闲状态信号的“与”。

6、优选地,所述的按分段长时钟树的思想,从时钟门控单元的时钟输出段长时钟树具体是指分段插入时钟buf,每段时钟buf尽量插到时钟门控单元之后。

7、优选地,所述的ip模块包括cpu处理器模块、显示控制器模块、io控制器模块、存储器模块和/或dsp处理器模块。

8、优选地,所述的芯片为soc芯片系统。

9、本发明还提供一种结构化的芯片设计架构的功耗降低方法,包括以下步骤:

10、第一步、设计优化所述芯片的各个ip模块,对ip模块的各个子模块做合适的模块切分及层级切分;所述的合适的模块切分具体是指将功能近似的子模块合并在同一个模块,并限制每个子模块的寄存器组ff组的数量到200;所述的层级切分具体是指按逻辑功能嵌套的规则对各个子模块分多级子模块嵌套;

11、第二步、对每个子模块增加模块空闲状态信号,对于里面有嵌套多个子模块的模块,模块的空闲状态信号是其内部的多个子模块的空闲状态信号的“与”;

12、第三步、在每个子模块前调用时钟门控单元,根据所对应的模块空闲状态信号产生门控的时钟并送给对应的子模块;

13、第四步、在时钟树综合时,按分段长时钟树的思想,从时钟门控单元的时钟输出段长时钟树,分段插入时钟buf,每段时钟buf尽量插到时钟门控单元之后;

14、所述芯片的各个ip模块、子模块以及对应的时钟树都能够自动根据电路的空闲状态把不需要工作的电路关闭,从而降低功耗。

15、优选地,本发明还提供所述的结构化的芯片设计架构在时钟门控、电源域和/或电压域中的应用。

16、优选地,本发明还提供所述的结构化的芯片设计架构的功耗降低方法在时钟门控、电源域和/或电压域中的应用。

17、有益效果

18、与现有技术相比,本发明的有益效果是:

19、本发明所述的结构化的芯片设计架构与方法使整个soc系统的各个ip模块、子模块、对应的时钟树都可以自动根据电路的空闲状态多粒度(此处多粒度是指不同模块等级的粗细粒度等级的多粒度)多层级的把某时刻不需要工作的电路关闭,从而将功耗降到了最低。

20、本发明的具体实施例虽然是以时钟门控为例来说明结构化的低功耗架构与方法,但是对于本领域技术人员来说,可以推广到电源域、电压域或三者组合的结构化的设计架构与方法。

技术特征:

1.一种结构化的芯片设计架构,其特征在于,所述的结构化的芯片设计架构包括切分组件、空闲状态信号增加组件、时钟产生组件和时钟树综合组件;所述的切分组件用于对所述芯片的各个ip模块的各个子模块做合适的模块切分及层级切分;所述的空闲状态信号增加组件用于对每个子模块增加模块空闲状态信号;所述的时钟产生组件用于在每个子模块前调用时钟门控单元,根据所对应的模块空闲状态信号产生门控的时钟并送给对应的子模块;所述的时钟树综合组件用于在时钟树综合时,按分段长时钟树的思想,从时钟门控单元的时钟输出段长时钟树。

2.根据权利要求1所述的结构化的芯片设计架构,其特征在于,所述的合适的模块切分具体是指将功能近似的子模块合并在同一个模块,并限制每个子模块的寄存器组ff组的数量到200。

3.根据权利要求1所述的结构化的芯片设计架构,其特征在于,所述的层级切分具体是指按逻辑功能嵌套的规则对各个子模块分多级子模块嵌套。

4.根据权利要求1所述的结构化的芯片设计架构,其特征在于,对于里面有嵌套多个子模块的模块,模块的空闲状态信号是其内部的多个子模块的空闲状态信号的“与”。

5.根据权利要求1所述的结构化的芯片设计架构,其特征在于,所述的按分段长时钟树的思想,从时钟门控单元的时钟输出段长时钟树具体是指分段插入时钟缓冲器,每段时钟缓冲器尽量插到时钟门控单元之后。

6.根据权利要求1所述的结构化的芯片设计架构,其特征在于,所述的ip模块包括cpu处理器模块、显示控制器模块、io控制器模块、存储器模块和/或dsp处理器模块。

7.根据权利要求1所述的结构化的芯片设计架构,其特征在于,所述的芯片为soc芯片系统。

8.根据权利要求1至7任一项所述的结构化的芯片设计架构的功耗降低方法,其特征在于,包括以下步骤:

9.根据权利要求1至7任一项所述的结构化的芯片设计架构在时钟门控、电源域和/或电压域中的应用。

10.根据权利要求8所述的结构化的芯片设计架构的功耗降低方法在时钟门控、电源域和/或电压域中的应用。

技术总结

本发明涉及一种结构化的芯片设计架构与方法,该架构包括切分组件、空闲状态信号增加组件、时钟产生组件和时钟树综合组件;所述的切分组件用于对所述芯片的各个IP模块的各个子模块做合适的模块切分及层级切分;所述的空闲状态信号增加组件用于对每个子模块增加模块空闲状态信号;所述的时钟产生组件用于在每个子模块前调用时钟门控单元,根据所对应的模块空闲状态信号产生门控的时钟并送给对应的子模块;所述的时钟树综合组件用于在时钟树综合时,按分段长时钟树的思想,从时钟门控单元的时钟输出段长时钟树。

技术研发人员:刘泽义,高鹰

受保护的技术使用者:格睿通智能科技(深圳)有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!