并行随机计算神经网络系统及其硬件压缩方法、系统与流程

本发明涉及超大规模集成电路架构设计,具体地,涉及一种并行随机计算神经网络系统及其硬件压缩方法、系统,同时提供了一种相应的终端及计算机可读存储介质。

背景技术:

1、神经网络近年来在图像分类、目标检测、自然语言处理等领域取得了巨大的成功。一个神经网络模型往往包含大量的乘加运算,传统cpu并不满足其计算密集的需求,因此基于fpga或者asic的神经网络硬件加速器研究得到了广泛的关注。神经网络本身具有高并行计算的潜力,但受限于硬件平台有限的资源,高并行神经网络硬件架构设计一直是一个有挑战性的问题。

2、随机计算作为后摩尔时代的新型计算范式,近年来得到了较多关注。他利用近似计算的思想,以牺牲一定计算精度为代价,可以用极低的硬件资源开销实现一些常用的算数单元,例如乘法器、加法器、双曲正切函数等。因为神经网络的容错能力,基于随机计算的神经网络可以在保证精度的前提下有效降低硬件资源开销,已被学界广泛研究。传统随机计算利用比特流串行编码的方式,将二进制数转换成单比特序列,并且该序列中比特1出现的概率等于某个常数值。该编码方式使得随机计算的性能受随机数质量的影响较大,为增强序列分布可控性、提高随机计算精度,确定性编码方式被提出,在该编码方式中,序列中1的分布不再具有随机性。

3、随机计算神经网络为取得较好的性能,往往需要较长的序列长度,这导致较高的计算延迟,严重降低了随机计算神经网络的吞吐率。基于比特扩展的随机计算架构为解决低吞吐率的问题,在比特层面采用全并行结构,并利用近似计算的思想,用比特扩展、比特选择、加法来实现传统的二进制乘加操作,成功减少了硬件开销。但是,并行随机计算神经网络(parallel stochastic-computing neural network,psc-nn)仍然需要大量的硬件资源开销,在如今网络深度越来越大的趋势下,在例如可穿戴式设备等资源有限的硬件平台上部署psc-nn仍然面临着巨大挑战。

技术实现思路

1、本发明针对现有技术中存在的上述不足,提供了一种并行随机计算神经网络系统及其硬件压缩方法、系统,同时提供了一种相应的终端及介质。

2、本发明是通过以下技术方案实现的。

3、根据本发明的一个方面,提供了一种并行随机计算神经网络系统的硬件压缩方法,采用如下任意一种或任意多种压缩方法,基于fpga或asic,对fpga或asic实现的并行随机神经网络中加法树的输入比特数量进行压缩,实现对并行随机计算神经网络系统的硬件压缩:

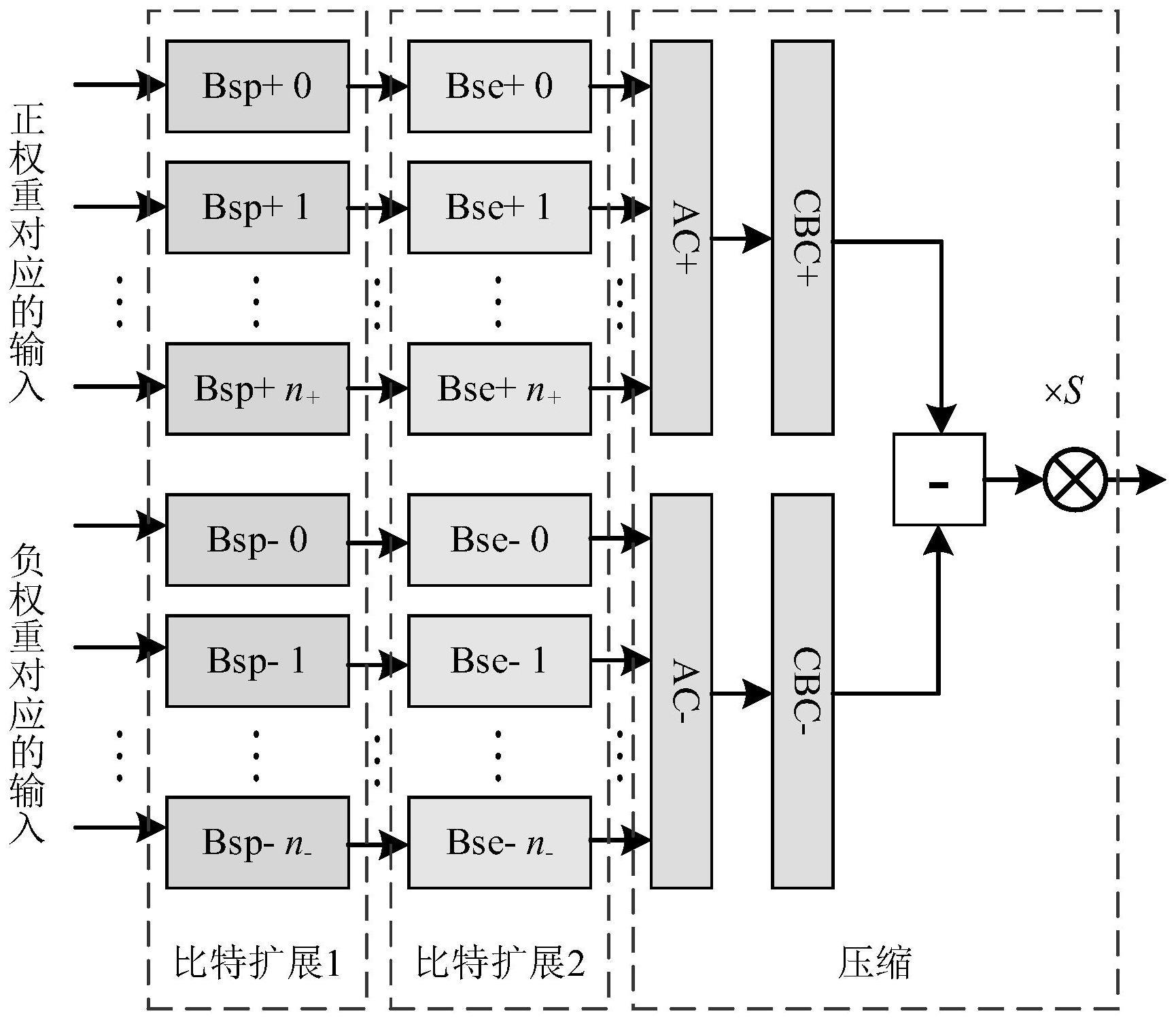

4、-正负分离压缩方法,该压缩方法对训练好的神经网络的权重进行正负分离,分别对正负权重对应的输入进行不包含符号位的并行随机比特扩展,并将扩展后的比特作为加法树的输入,降低加法树的输入规模;

5、-连续比特压缩方法,该压缩方法对同源比特进行压缩,并分组赋权后作为加法树的输入,减少同源比特输入到加法树的数量;

6、-近似压缩方法,该压缩方法对待输入加法树的比特进行部分选择,相加后乘上对应的倍数因子,将原加法树的规模减小为权重加法树的规模。

7、可选地,所述正负分离压缩方法,包括:

8、对神经网络的每一个神经元的权重进行正负分离,采用符号-绝对值的形式表示每一个神经元的输入激活数值;

9、对正负权重对应的输入激活数值进行并行随机比特扩展,包括:将二进制权重为w的比特扩展出w个权重为1的比特,根据权重绝对值w在扩展后的n个比特中随机选取wn个比特,完成并行随机比特扩展;其中,w<1;在并行随机比特扩展过程中,符号位不参与比特扩展;

10、所述并行随机比特扩展通过逻辑线的扩展实现;

11、将正负权重对应的扩展后的比特作为加法树的输入。

12、可选地,所述连续比特压缩方法,包括:

13、对二进制数的某个比特进行比特扩展,得到一系列数值相同的比特序列,即为同源比特;对所述同源比特进行压缩,以得到的单比特值表征这些同源比特;

14、对压缩后的单比特赋予相应的权重,所述权重等于该比特压缩前的同源比特数量;

15、对神经网络的每一个神经元中所有相同权重的单比特值进行相加后,乘以该权重,再将得到的不同权重对应的结果作为加法树的输入进行相加得到最终神经元的输出。

16、可选地,所述近似压缩方法,包括:

17、对待输入加法树的并行随机比特扩展后的比特进行部分选择,选择后的比特数目为原比特数目的1/s,其中s为倍数因子;

18、对选择后的比特进行求和,并将求和结果乘以倍数因子s作为加法树的输入进行相加得到神经元的输出。

19、可选地,所述对并行随机比特扩展后的比特进行部分选择的方法,包括:随机选择方法、分组后组内随机选择方法和均匀选择方法;其中:

20、所述随机选择方法,包括:随机选择原比特数目的1/s个比特;

21、所述分组后组内随机选择方法,包括:将原比特中的每s个比特分为一组,每组随机选择1个比特;

22、所述均匀选择方法,包括:在原比特中每s个比特选择一个比特。

23、可选地,当采用多种压缩方法进行并行随机计算神经网络的硬件压缩时,按照正负分离压缩方法、近似压缩方法和/或连续比特压缩方法的前后顺序进行实施,并得到新的并行随机计算神经网络硬件架构。

24、可选地,该方法还包括如下任意一项或任意多项:

25、-通过所述正负分离压缩方法得到加法树的输入后,所述加法树对所述输入进行独立累加计算,得到两个非负的数值结果;采用减法器将两个数值结果相减并通过激活函数单元得到最终神经元的输出;

26、-通过所述连续比特压缩方法得到加法树的输入后,所述加法树对所述输入进行相加得到最终神经元的输出;

27、-通过所述近似压缩方法得到加法树的输入后,所述加法树对所述输入进行相加得到神经元的输出。

28、根据本发明的另一个方面,提供了一种并行随机计算神经网络的硬件压缩系统,采用如下任意一个或任意多个压缩模块,对并行随机神经网络中加法树的输入比特数量进行压缩,实现对并行随机计算神经网络系统的硬件压缩:

29、-正负分离压缩模块,该压缩模块对训练好的神经网络的权重进行正负分离,分别对正负权重对应的输入进行不包含符号位的并行随机比特扩展,并将扩展后的比特作为加法树的输入,降低加法树的输入规模;

30、-连续比特压缩模块,该压缩模块对同源比特进行压缩,并分组赋权后作为加法树的输入,减少同源比特输入到加法树的数量;

31、-近似压缩模块,该压缩模块对待输入加法树的比特进行部分选择,相加后乘上对应的倍数因子,将原加法树的规模减小为权重加法树的规模;

32、通过上述任意一个压缩模块的独立实施或任意多个压缩模块的共同实施,完成对并行随机计算神经网络系统的硬件压缩。

33、根据本发明的第三个方面,提供了一种基于fpga或asic的并行随机计算神经网络系统,采用上述任一项所述的方法,或,上述的系统,对fpga或asic实现的并行随机神经网络中加法树的输入比特数量进行压缩,实现对并行随机计算神经网络系统的硬件压缩。

34、根据本发明的第四个方面,提供了一种终端,包括存储器、处理器及存储在存储器上并可在处理器上运行的计算机程序,所述处理器执行所述程序时可用于上述中任一项所述的方法,或,运行上述的系统。

35、根据本发明的第五个方面,提供了一种计算机可读存储介质,其上存储有计算机程序,该程序被处理器执行时可用于执行上述中任一项所述的方法,或,运行上述的系统。

36、由于采用了上述技术方案,本发明与现有技术相比,具有如下至少一项的有益效果:

37、本发明提供的并行随机计算神经网络系统及其硬件压缩方法、系统,采用正负分离压缩、连续比特压缩、近似压缩中任意一种或任意多种压缩技术,有效减少并行随机计算网络神经网络系统中加法树的输入规模,将其运用到现有并行随机计算神经网络架构中,可以得到三种对应的硬件模块,有效降低现有并行随机计算神经网络系统原有硬件开销。

38、本发明提供的并行随机计算神经网络系统及其硬件压缩方法、系统,通过在传统并行随机计算神经网络系统上实施正负分离压缩、连续比特压缩和近似压缩中任意一种或任意多种压缩技术,实现对并行随机计算神经网络中硬件开销占比最大的加法树的输入比特数量规模的压缩,从而减小加法树的硬件开销,进而能够得到一个全新的压缩后的并行随机计算神经网络系统。

39、本发明提供的并行随机计算神经网络系统及其硬件压缩方法、系统,应用于asic或fpga实现的并行随机计算神经网络,可以有效降低asic或fpga的逻辑资源开销。

40、本发明提供的并行随机计算神经网络系统及其硬件压缩方法、系统,尤其适用于图像分类、目标检测、自然语言处理等技术领域,能够有效降低所用神经网络系统的硬件开销,提升能量效率。

- 还没有人留言评论。精彩留言会获得点赞!