一种基于ARM总线动态时钟门控装置的制作方法

一种基于arm总线动态时钟门控装置

技术领域

1.本发明涉及电子信息技术领域,尤其涉及一种基于arm总线动态时钟门控装置。

背景技术:

2.模块级静态时钟门控,需要软件进行控制。当该模块工作时软件使能时钟门控,不工作时软件禁止。

3.软件只能对整个模块的时钟网络进行统一的使能或禁止操作,不够灵活。也无法做到进一步细分模块内部的时钟网络,从而达到进一步节省功耗的目的。而且在嵌入式soc系统中,一个模块往往处于间歇性工作的状态,该模块时钟网络的功耗开销还取决于软件控制程序的品质优劣,同时也极大增加了软件程序的复杂程度,复杂的程序本身功耗开销也更大。

4.此外,rtl综合工具自动产生动态时钟门控对rtl的代码书写规范有着严格的限制,只有满足该规范书写的要求的代码,综合工具才会将触发器d端的使能信号自动综合到时钟端。另外,rtl综合工具自动产生动态时钟门控会额外增加逻辑单元;又由于rtl综合工具是对满足转换条件的rtl代码逐个进行转换的,所以代码量越大增加的逻辑单元也越多,增加的逻辑单元本身也是有功耗开销的。

技术实现要素:

5.本发明的目的是为了解决现有技术中存在的缺点,而提出的一种基于arm总线动态时钟门控装置。

6.为了实现上述目的,本发明采用了如下技术方案:

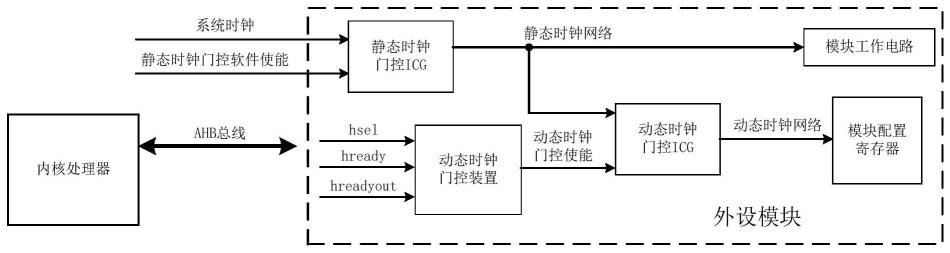

7.一种基于arm总线动态时钟门控装置,包括外设模块,其中所述外设模块通过ahb总线与内核处理器连接或通过apb总线与apb桥控制器连接,所述外设模块由静态时钟门控icg、模块工作电路、动态时钟门控装置、动态时钟门控icg、模块配置寄存器组成,其中静态时钟门控icg通过静态时钟网络与模块工作电路及动态时钟门控icg连接,动态时钟门控装置通过动态时钟网络与模块配置寄存器连接。

8.优选地,所述静态时钟门控icg通过软件开启或关闭静态时钟门控的使能信号。

9.优选地,所述动态时钟门控装置由ahb总线或apb总线访问的状态开启或关闭动态时钟网络的使能信号。

10.优选地,所述动态时钟门控icg通过动态时钟门控装置产生的使能信号开启或关闭。

11.优选地,所述模块配置寄存器用于模块的功能配置。

12.本发明具有以下有益效果:

13.1、通过增加动态时钟门控装置,进一步细分模块内部的时钟网络。精准的降低模块内部配置寄存器的时钟网络的功耗开销。

14.2、ahb总线动态时钟门控装置是固定的单一的控制逻辑,与配置寄存器的实际数

量无关,只要符合动态时钟条件的配置寄存器都可以使用该动态时钟网络。也不会因为配置寄存器的代码数量的多寡,而在rtl综合时产生更多的冗余的动态时钟门控逻辑,增加面积和功耗的开销。

附图说明

15.图1为ahb总线动态时钟门控整体框图;

16.图2为ahb总线动态时钟门控电路图;

17.图3为ahb总线动态时钟门控时序图;

18.图4为apb总线动态时钟门控整体框图;

19.图5为apb总线动态时钟门控电路图;

20.图6为apb总线动态时钟门控时序图;

21.图7为静态时钟门控整体框图;

22.图8为rtl综合工具自动产生动态时钟门控示意图。

具体实施方式

23.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。

24.一种基于arm总线动态时钟门控装置,包括外设模块,其中外设模块通过ahb总线与内核处理器连接或通过apb总线与apb桥控制器连接,外设模块由静态时钟门控icg、模块工作电路、动态时钟门控装置、动态时钟门控icg、模块配置寄存器组成,其中静态时钟门控icg通过静态时钟网络与模块工作电路及动态时钟门控icg连接,动态时钟门控装置通过动态时钟网络与模块配置寄存器连接。模块配置寄存器用于模块的功能配置。

25.本发明中,在嵌入式soc中,各个模块内部存在大量的配置寄存器(用于模块的功能配置),通常在系统初始化后(直到模块关闭)将极少被总线二次访问。将这些配置寄存器使用动态时钟网络,在总线不访问时这些配置寄存器的时钟信号将禁止翻转,可以极大的节省时钟网络的功耗开销。

26.静态时钟门控icg通过软件开启或关闭静态时钟门控的使能信号。动态时钟门控装置由ahb总线或apb总线访问的状态开启或关闭动态时钟网络的使能信号。动态时钟门控icg通过动态时钟门控装置产生的使能信号开启或关闭。具体的,参照图2,在ahb总线动态时钟门控装置中,hsel=1且hready=1时开启动态时钟门控使能信号;当动态时钟门控使能且hreadyout=0时,动态时钟门控将保持为开启状态;当hreadyout=1时,关闭动态时钟门控使能信号。

27.或参照图4,在apb总线动态时钟门控装置中,当psel=1且penable=0时开启动态时钟门控使能信号;当动态时钟门控使能且pready=0时,动态时钟门控将保持为开启状态;当pready=1时,关闭动态时钟门控使能信号。

28.需要说明的是,如图7所示的目前现有的只通过软件对整个模块的时钟网络进行统一的使能或禁止操作,在嵌入式soc设计中,通常会为每个外设模块增加一个静态时钟门控icg单元。当该外设模块未使用时,软件禁止该模块的时钟网络;当该外设模块初始时,再由软件使能时钟网络,软件程序的复杂程度高,复杂的程序本身功耗开销也更大。

29.再如图8所示的rtl综合工具自动产生动态时钟门控,rtl综合工具可以将本该综合到触发器d端的使能信号,综合到触发器clk端。当使能信号有效时,释放一个clk时钟将触发器d端的数据传递到触发器的q端。综合工具会分析rtl代码,为符合条件的rtl代码自动产生动态时钟门控icg。随着代码量的上升,插入的icg的数量也会越多,从而造成冗余的icg电路,浪费电路面积和功耗开销。

30.而本发明中,在模块级静态时钟门控的基础上,增加arm总线动态时钟门控icg。将模块内部的时钟网络细分为2部分,静态时钟网络和动态时钟网络。

31.具体应用过程中,参照图1及图2,以ahb总线为例,使用hsel,hready和hreadyout总线控制信号,产生ahb总线动态时钟门控的使能信号。当ahb总线发起访问,在总线地址相位hsel=1且hready=1时使能动态时钟门控;当ahb总线完成访问时,在总线数据相位hreadyout=1时关闭动态时钟门控。

32.或参照图4及图5,以apb总线为例,使用psel,penable和pready总线控制信号,产生apb总线动态时钟门控的使能信号。当apb总线发起访问,psel=1且penable=0时使能动态时钟门控;当apb总线完成访问pready=1时关闭动态时钟门控。

33.相较于本文背景技术所提及的只通过软件对整个模块的时钟网络进行统一的使能或禁止操作的技术手段,进一步细分模块内部的时钟网络。精准的降低模块内部配置寄存器的时钟网络的功耗开销。

34.而相较于本文背景技术所提及的rtl综合工具自动产生动态时钟门控的技术手段,插入的icg的数量少,不会造成冗余的icg电路,也不会浪费电路面积和功耗开销。

35.以上所述,仅为本发明较佳的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,根据本发明的技术方案及其发明构思加以等同替换或改变,都应涵盖在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1