芯片时钟管理方法、装置及芯片、电子设备与流程

本申请涉及芯片,具体涉及一种芯片时钟管理方法、装置及芯片、电子设备。

背景技术:

1、随着芯片设计工艺的不断更新迭代,芯片规模越来越大,芯片功耗问题也愈加重要,过高的功耗不仅对芯片内部电路高温稳定工作状态提出更高要求,而且对于封装散热和外部电源系统也提出更为严格要求。

2、目前,相关技术对于芯片功耗的控制的一种方式是:通过优化电路设计,时钟频率切换以及综合工具优化功耗,优化电路设计和综合工具优化功耗的方式往往和具体设计功能相关,每个芯片设计差别较大;时钟工作频率在设计方案里面需要根据性能需求设定最高工作频率,往往性能指标确定后时钟频率也就固定了,只能按照当前电路是否工作或是否满负荷来决定降低或关闭时钟,这也是对动态功耗有直接影响,电路固定的情况下,时钟频率越低动态功耗就会越小。另一种方式是通过cpu控制开关或更改时钟频率,以及通过硬件电路自动开关,其中通过硬件电路自动开关对于动态功耗控制更加及时,且对性能影响较小;然而,对于硬件自动开关时钟或动态时钟变频,传统设计中往往只会在一些功能电路局部实现且实现方式也会有差异,这样很难从时钟根节点完全关闭时钟,功耗优化效果有限。

3、因此,如何在不影响芯片性能的情况下,有效的降低芯片的功耗具有重要意义。

技术实现思路

1、本申请实施方式主要解决目前芯片功耗大的技术问题,以实现在不影响芯片性能的情况下,有效降低芯片功耗的目的。

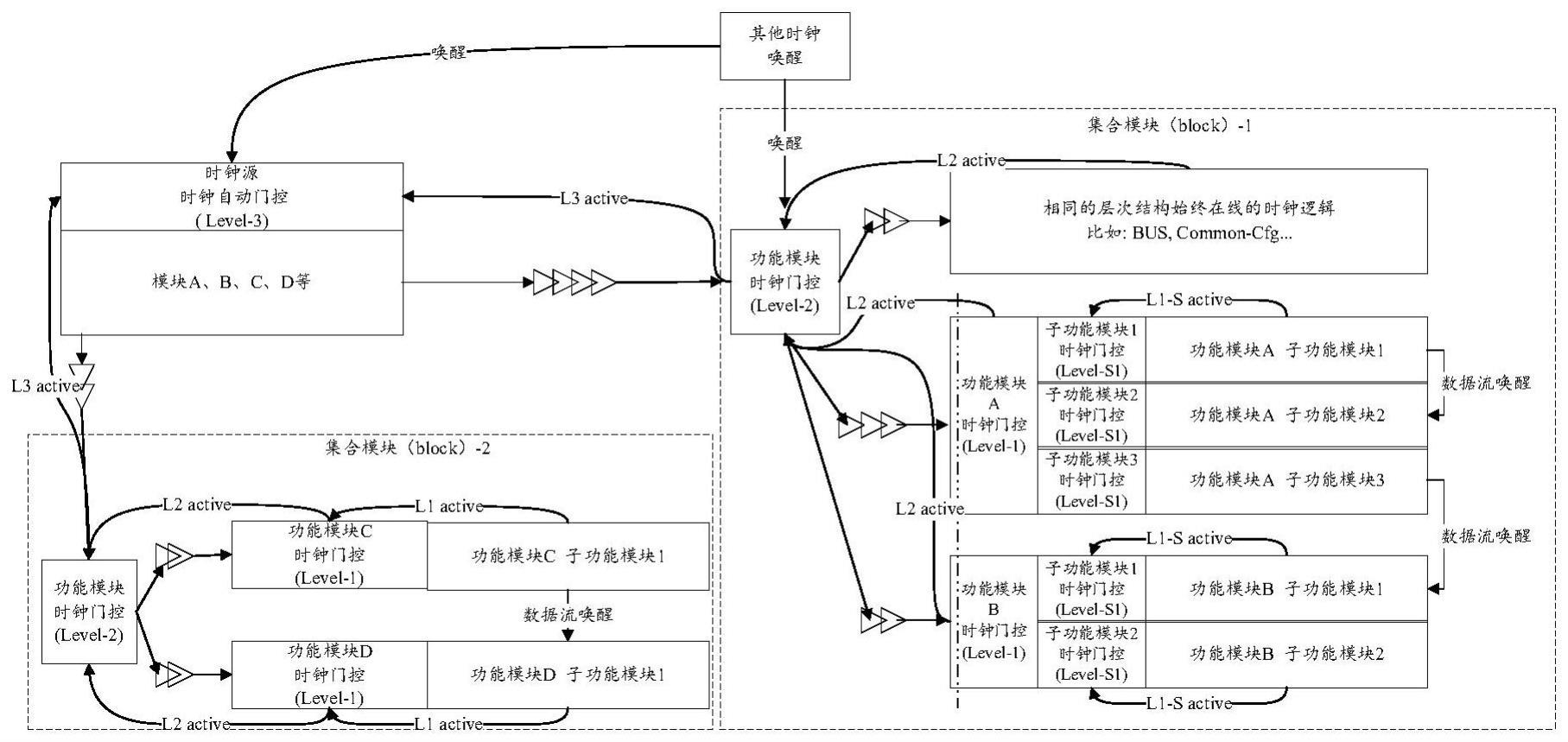

2、为解决上述技术问题,本申请实施方式采用的一个技术方案是:提供一种芯片时钟管理方法,所述芯片包括时钟源、多层级时钟自动门控、至少一个功能模块、至少一个子功能模块以及至少一个集合模块,所述功能模块包括至少一个所述子功能模块,所述集合模块包括至少一个所述功能模块;

3、所述方法包括:根据所述子功能模块的工作状态,通过所述多层级时钟门控控制所述功能模块的时钟;根据所述功能模块的工作状态,通过所述多层级时钟门控控制所述集合模块的时钟;根据所述集合模块的工作状态,通过所述多层级时钟门控控制所述时钟源。

4、可选地,所述根据所述子功能模块的工作状态,通过所述多层级时钟门控控制所述功能模块的时钟,包括:当所述子功能模块都处于非工作状态时,控制所述功能模块的时钟关闭。

5、可选地,所述根据所述功能模块的工作状态,通过所述多层级时钟门控控制所述集合模块的时钟,包括:当所述功能模块都处于非工作状态时,控制所述集合模块的时钟关闭。

6、可选地,所述根据所述集合模块的工作状态,通过所述多层级时钟门控控制所述时钟源,包括:当所述集合模块都处于非工作状态时,控制所述时钟源的关闭。

7、可选地,所述方法还包括:当任一所述子功能模块或所述功能模块接收到其它子功能模块或所述功能模块发送的数据流时,

8、所述子功能模块的时钟、所述子功能模块所在的所述功能模块的时钟、及所述功能模块所在的时钟源被依次唤醒,

9、或者所述功能模块及其所在的时钟源被依次唤醒。

10、可选地,所述方法还包括:所述功能模块或所述时钟源通过所述子功能模块或所述功能模块发送的信号强度,判断是否关闭所述功能模块的时钟或所述时钟源。

11、可选地,当所述时钟源包括至少两个时,所述方法还包括:通过非关闭状态的所述时钟源向待唤醒的所述时钟源发送唤醒命令,以唤醒待唤醒的所述时钟源;或者通过非关闭状态的所述时钟源所在的所述功能模块或子功能模块发送的数据流唤醒待唤醒的所述时钟源。

12、为解决上述技术问题,本申请实施方式采用的另一个技术方案是:提供一种芯片时钟管理装置,所述芯片包括时钟源、多层级时钟门控、至少一个功能模块、至少一个子功能模块以及至少一个集合模块,所述功能模块包括至少一个所述子功能模块,所述集合模块包括至少一个所述功能模块;

13、所述装置包括:第一控制模块,用于根据所述子功能模块的工作状态,通过所述多层级时钟门控控制所述功能模块的时钟;第二控制模块,用于根据所述功能模块的工作状态,通过所述多层级时钟门控控制所述集合模块的时钟;第三控制模块,用于根据所述集合模块的工作状态,通过多少多层级时钟门控控制所述时钟源。

14、为解决上述技术问题,本申请实施方式采用的又一个技术方案是:提供一种芯片,包括:至少一个处理器;以及,与所述至少一个处理器通信连接的存储器;其中,所述存储器存储有可被所述至少一个处理器执行的指令,以使所述至少一个处理器执行如上所述的芯片时钟管理方法。

15、为解决上述技术问题,本申请实施方式采用的还一个技术方案是:提供一种电子设备,包括如上所述的芯片。

16、本申请实施例提供的芯片时钟管理方法、装置及芯片、电子设备,通过在芯片的系统模块设计阶段,考虑每一功能模块的功耗问题,具体通过设计时钟源、多层级时钟门控、至少一个功能模块、至少一个子功能模块以及至少一个集合模块,该至少一个功能模块包括至少一个所述子功能模块;该集合模块包括至少一个所述功能模块;其中可以根据子功能模块的工作状态,通过所述多层级时钟门控控制功能模块的时钟,根据功能模块的工作状态,通过所述多层级时钟门控控制集合模块的时钟,还可以根据集合模块的工作状态,通过所述多层级时钟门控控制时钟源。由此,按照系统时钟结构划分各个模块的时钟管理单元,每个子功能模块的本地时钟是否关闭由子功能模块的工作状态决定,每个功能模块的本地时钟是否关闭由其包括的子功能模块的工作状态决定,时钟源的关闭或打开由其对应的全部集合模块的工作状态共同决定。本申请提供的实施方式能够按系统功能模块的层次划分时钟门控,实现逐层控制管理功能模块的时钟门控,可以准确的控制各个分支上的时钟门控的开、关,而且通过时钟源可以实现从源头关闭时钟,因此,本申请的实施方式能够在不影响芯片性能的情况下,有效地降低芯片时钟树上的功耗,从而降低了芯片的功耗。

技术特征:

1.一种芯片时钟管理方法,其特征在于,所述芯片包括时钟源、多层级时钟门控、至少一个功能模块、至少一个子功能模块以及至少一个集合模块,所述功能模块包括至少一个所述子功能模块,所述集合模块包括至少一个所述功能模块;

2.根据权利要求1所述的方法,其特征在于,所述根据所述子功能模块的工作状态,通过所述多层级时钟门控控制所述功能模块的时钟,包括:

3.根据权利要求1所述的方法,其特征在于,所述根据所述功能模块的工作状态,通过所述多层级时钟门控控制所述集合模块的时钟,包括:

4.根据权利要求3所述的方法,其特征在于,所述根据所述集合模块的工作状态,通过所述多层级时钟门控控制所述时钟源,包括:

5.根据权利要求1所述的方法,其特征在于,所述方法还包括:

6.根据权利要求1所述的方法,其特征在于,所述方法还包括:

7.根据权利要求1所述的方法,其特征在于,当所述时钟源包括至少两个时,所述方法还包括:

8.一种芯片时钟管理装置,其特征在于,所述芯片包括时钟源、多层级时钟门控、至少一个功能模块、至少一个子功能模块以及至少一个集合模块,所述功能模块包括至少一个所述子功能模块,所述集合模块包括至少一个所述功能模块;

9.一种芯片,其特征在于,包括:

10.一种电子设备,其特征在于,包括如权利要求9所述的芯片。

技术总结

本申请涉及芯片技术领域,公开了一种芯片时钟管理方法、装置及芯片、电子设备。该芯片包括时钟源、多层级时钟门控、至少一个功能模块、至少一个子功能模块及至少一个集合模块,其中,功能模块包括所述子功能模块,集合模块包括所述功能模块。本申请可以根据子功能模块的工作状态,通过所述多层级时钟门控控制功能模块的时钟,根据功能模块的工作状态,通过所述多层级时钟门控控制集合模块的时钟,根据集合模块的工作状态,通过所述多层级时钟门控控制时钟源。本申请能够按系统功能模块的层次划分时钟门控,实现逐层控制管理功能模块的时钟门控,在不影响芯片性能的情况下,有效地降低芯片时钟树上的功耗,从而降低了芯片的功耗。

技术研发人员:孟鹏涛

受保护的技术使用者:深圳大普微电子科技有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!