一种嵌入式人工智能计算机主板的制作方法

1.本实用新型涉及计算机主板技术领域,具体涉及一种嵌入式人工智能计算机主板。

背景技术:

2.开发板是用来进行嵌入式系统开发的电路板,包括中央处理器、存储器、输入设备、输出设备、数据通路/总线和外部资源接口等一系列硬件组件。硬件组内包括有ai开发模块,通过开发板连接外设的ai设备,但现有的ai设备种类多样,使用到的用于数据传输的串口类型也不完全相同,包括有单路串口、双路串口和四路串口,应此需要一种兼容多种类型串口的aia开发模块。

技术实现要素:

3.有鉴于此,本实用新型要解决的问题是提供一种嵌入式人工智能计算机主板,能够使计算机主板连接不同类型串口的ai外设。

4.为解决上述技术问题,本实用新型采用的技术方案是:

5.一种嵌入式人工智能计算机主板,包括有嵌入安装的主控芯片和ai串口电路,所述ai串口电路包括有四路通信电路、双路通信电路和单路通信电路,所述主控芯片包括有spi同步串行口、若干i2c双线串口和若干gpio单线串口,所述spi同步串行口并接有若干组四路通信电路,所述i2c双线串口连接有双路通信电路,所述gpio单线串口连接有单路通信电路,用于使主控芯片可通过ai串口电路与任意类型串口的ai外设数据互通。

6.进一步的,所述四路通信电路包括有u12四位双向转换器和用于与ai外置连接的cn8连接器,所述cn8连接器通过u12四位双向转换器与spi同步串行口数据互通。

7.进一步的,所述spi同步串行口连接有两条四路通信电路。

8.进一步的,所述主控芯片连接有用于显示两条四路通信电路是否正常接通的第一指示电路;

9.所述指示电路包括有基栅极与ai串口电路连接的q28mos管和q27mos管,所述q28mos管和q27mos管的源极均接地设置,所述q23mos管和q24mos管的漏极分别接有led8发光二极管和led9发光二极管的一端,另一端接均接vcc电源设置。

10.进一步的,所述双路通信电路包括有cn11连接器和用于与ai外置连接的u16双路电平转换器,所述n11连接器通过u16双路电平转换器与i2c双线串口数据互通;

11.所述n11连接器包括有四个传输接口,用于同时与两个u16双路电平转换器连接,构成两条双路通信电路。

12.进一步的,所述单路通信电路包括有cn10连接器和用于与ai外置连接的u14电平转换器,所述cn10连接器通过u14电平转换器与gpio单线串口数据互通;

13.所述u14电平转换器为四位双向转换器,所述cn10连接器包括有四个传输接口,用于同时构成四条双向单路通信电路。

14.进一步的,述主控芯片的int_out_gpio69端口和int_in_gpio1端口共同连接有第二指示电路,用于分别显示两条双路通信电路是否导通,所述u14电平转换器的所有数据传输端口分别连接有第三指示电路和第四指示电路,均用于分别显示每条单路通信电路是否导通;

15.所述第二指示电路、第三指示电路和第四指示电路的结构与第一指示电路的结构相同。

16.进一步的,所述主控芯片的pwm0端口和gpio73端口共同连接有用于安装扇热风扇的cn5插针;

17.所述cn5插针的4端口通过d20二极管与主控芯片的gpio73端口数据互通,所述d20二极管并接有r57电阻,所述cn5插针的2端口连接有q1三极管的集电极,所述q1三极管的基极与主控芯片的pwm0端口连接,所述q1三极管的发射极与基极之间串接有d12二极管。

18.进一步的,所述cn5插针的1端口通过l6滤波电容与vcc电源连接,所述l6滤波电容并接有d18二极管。

19.本实用新型具有的优点和积极效果是:

20.通过将主控芯片与若干四路通信电路、双路通信电路和单路通信电路连接,四路通信电路用于与四路通信的外设ai连接,双路通信电路用于与双路通信的外设ai连接,单路通信电路用于与单路通信的外设ai连接,使得计算机主板能够连接不同类型串口的外设ai。

附图说明

21.附图用来提供对本实用新型的进一步理解,并且构成说明书的一部分,与本实用新型的实施例一起用于解释本实用新型,并不构成对本实用新型的限制。在附图中:

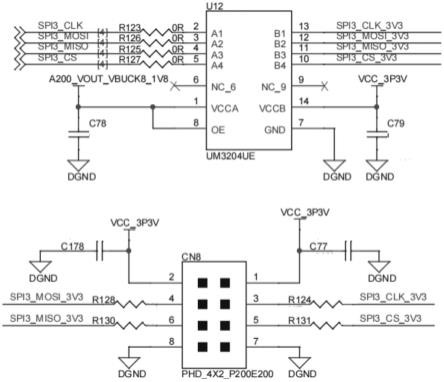

22.图1是本实用新型的一种嵌入式人工智能计算机主板的四路通信电路图;

23.图2是本实用新型的一种嵌入式人工智能计算机主板的双路通信电路图;

24.图3是本实用新型的一种嵌入式人工智能计算机主板的单路通信电路图;

25.图4是本实用新型的一种嵌入式人工智能计算机主板的第一指示电路图;

26.图5是本实用新型的一种嵌入式人工智能计算机主板的cn5插针的连接电路图。

具体实施方式

27.下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本实用新型一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

28.需要说明的是,当组件被称为“固定于”另一个组件,它可以直接在另一个组件上或者也可以存在居中的组件。当一个组件被认为是“连接”另一个组件,它可以是直接连接到另一个组件或者可能同时存在居中组件。当一个组件被认为是“设置于”另一个组件,它可以是直接设置在另一个组件上或者可能同时存在居中组件。本文所使用的术语“垂直的”、“水平的”、“左”、“右”以及类似的表述只是为了说明的目的。

29.除非另有定义,本文所使用的所有的技术和科学术语与属于本实用新型的技术领

域的技术人员通常理解的含义相同。本文中在本实用新型的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本实用新型。本文所使用的术语“及/或”包括一个或多个相关的所列项目的任意的和所有的组合。

30.本实用新型提供一种嵌入式人工智能计算机主板,如图1至图3所示,包括有嵌入安装于计算机主板上的主控芯片和ai串口电路,主控芯片通过ai串口电路与外设ai数据互通,以获取外设ai的数据或控制外设ai动作。

31.ai串口电路包括有四路通信电路、双路通信电路和单路通信电路,用于匹配外设ai其不同类型的通信串口。主控芯片包括有spi同步串行,同步串行可同时接多条四路通信电路。如图1所示,四路通信电路包括有cn8连接器和u12四位双向转换器,cn8连接器用于与外设ai连接,以获取外设ai输出的四路信息。cn8连接器通过u12四位双向转换器与spi同步串行口数据互通,u12四位双向转换器用于转换四路信息,使主控芯片能够识别。

32.优选的,主控芯片连接有两条四路通信电路。为便于使用者确定四路通信电路是否投入使用,在主控芯片的spi1_mosi_gpio79端口和cpio2端口共同连接有第一指示电路,通过判断指示电路上的灯谁否亮起,确定两条四路通信电路是否正常使用。

33.如图4所示,第一指示电路包括有q28mos管和q27mos管,q28mos管的基栅极与主控芯片的spi1_mosi_gpio79端口连接,q27mos管的栅极与主控芯片的gpio2端口连接,q28mos管和q27mos管的源极均接地设置,q28mos管和q27mos管的漏极分别接有led8发光二极管和led9发光二极管的一端,另一端接均接vcc电源设置。每个发光二极管对应一条四路通信电路,当该四路通信电路导通后,主控芯片控制对应的mos管导通,使发光二极管亮起,行驶对应通信该道路处于正常使用状态。

34.主控芯片还包括有用于双路通信的i2c双线串口,i2c双线串口连接有若干双路通信电路。如图2所示,双路通信电路包括有u16双路电平转换器和cn11连接器,cn11连接器用于与外设ai连接,以接收外设ai发出的双路信号,n11连接器连接器通过u16双路电平转换器与i2c双线串口数据互通,u16双路电平转换器的功能与u12四位双向转换器的功能相同。

35.优选的,n11连接器包括有四个传输接口,四个传输接口可分别与两个u16双路电平转换器连接(图中为一个u16双路电平转换器和一个u19双路电平转换器),构成两条双路通信电路。主控芯片的int_out_gpio69端口和int_in_gpio1端口共同连接有第二指示电路,第二指示电路的结构与第一指示电路的结构完全相同,用于分别显示两条双路通信电路是否导通。

36.主控芯片包括有gpio单线串口,通过gpio单线串口连接有若干单路通信电路。如图3所示,单路通信电路包括有u14电平转换器和cn10连接器,cn10连接器用于与单路通信的外设ai连接,用于接收外设ai给出的单路信号,cn10连接器通过u14电平转换器与gpio单线串口数据互通,u14电平转换器的功能与u12四位双向转换器的功能相同。

37.优选的,u14电平转换器可为四位双向转换器,同时cn10连接器包括有四个传输接口,可同时构成四条双向单路通信电路。u14电平转换器包括有用于输入输出数据的四个a端口和四个b端口,为便于知道单路通信电路是否投入使用,在u14电平转换器的所有a端口分别连接有第三指示电路和第四指示电路,第三指示电路和第四指示电路的结构与第一指示电路的结构完全相同,用于分别显示每条单路通信电路是否导通。

38.如图5所示,主控芯片工作时间过长会导致芯片发热,为方便给主控芯片降温,主

控芯片通过pwm0端口和gpio73端口连接用于安装扇热风扇的cn5插针。cn5插针的1端口通过l6滤波电容与vcc电源连接,l6滤波电容并接有d18二极管,用于单向录波处理(对输入1端口的电流进行滤波处理,1端口输出端的电流不做滤波处理),保证稳定的给cn5插针的1端口供电。

39.cn5插针的4端口通过d20二极管与主控芯片的gpio73端口数据互通,d20二极管并接有r57电阻,用于给cn5插针的2端口单向输入高压电流,当电流反方向时d20二极管不导通,r57电阻作压降处理,可避免高压干扰gpio73端口,保证主控芯片的性能。

40.cn5插针的2端口连接有q1三极管的集电极,q1三极管的基极与主控芯片的pwm0端口连接,q1三极管的发射极与基极之间串接有d12二极管,用于控制q1三极管是否导通。主控芯片通过pwm0端口控制q1三极管导通,给cn5插针的2端口输入信号,以控制与cn5插针连接的风扇是否动作。

41.本实用新型的工作原理和工作过程如下:

42.给计算机主板供电,并查看需要连接的外设ai的接口类型,当外设ai的接口类型为单路传输时,将外设ai与cn10连接器连接,当为双路传输时,外设ai与cn11连接器连接,当为四路通信时,外设ai与u12四位双向转换器连接。

43.以四路通信电路为例,当外设ai通过四路通信电路与主控芯片连通后,主控芯片控制spi1_mosi_gpio79端口(或gpio2端口)的电压拉高,q27mos管导通,led8发光二极管亮起,表示该外设ai正常连接。

44.当主控芯片检测到有外设ai连接后改变pwm0端口的电压,q1三极管导通,cn5插针连接的风扇开始工作,给主控芯片降温。

45.以上对本实用新型的实施例进行了详细说明,但所述内容仅为本实用新型的较佳实施例,不能被认为用于限定本实用新型的实施范围。凡依本实用新型范围所作的均等变化与改进等,均应仍归属于本专利涵盖范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1