GPIO通信电路及板卡、电子设备的制作方法

gpio通信电路及板卡、电子设备

技术领域

1.本公开涉及计算机通信技术领域,具体涉及一种gpio通信电路及板卡、电子设备。

背景技术:

2.随着芯片技术的发展,芯片集成的功能也越来越多,目前芯片大多采用gpio(general-purpose input/output,通用型输入/输出接口)进行设备间通信。使用gpio可以利用软件模拟成熟的通信协议,例如i2c(inter-integrated circuit,同步串行总线)、uart(universal asynchronous receiver/transmitter,通用异步收发传输器)、spi(serial peripheral interface,串行外设接口)等协议。

3.但是,使用gpio通信时,在芯片非正常工作情况下,往往会出现各种非预期的效果,导致芯片间的通信管脚损伤,甚至导致芯片器件损毁。

技术实现要素:

4.为提高芯片非正常工作情况下的通信安全性和可靠性,本公开实施方式提供了一种gpio通信电路及板卡。

5.第一方面,本公开实施方式提供了一种gpio通信电路,包括:

6.处理芯片,包括gpio接口和目标信号输出接口;和

7.检测电路,包括第一端、第二端以及控制电路,所述第一端适于连接外部芯片电路,所述第二端连接所述处理芯片的所述gpio接口;

8.其中,所述控制电路连接所述处理芯片的所述目标信号输出接口,响应于接收到所述目标信号输出接口输出的目标信号,所述控制电路控制所述第一端和所述第二端导通;所述目标信号为周期性电平变化信号。

9.在一些实施方式中,所述检测电路包括缓冲器电路和所述控制电路,所述缓冲器电路包括所述第一端、所述第二端以及使能端,所述使能端与所述控制电路连接;所述检测电路根据所述使能端接收到的控制信号控制所述第一端和所述第二端导通。

10.在一些实施方式中,所述控制电路包括输入端和输出端,所述输入端连接所述处理芯片的所述目标信号输出接口,所述输出端连接所述缓冲器电路的所述使能端;所述控制电路响应于接收到所述目标信号,向所述缓冲器电路的所述使能端输出所述控制信号。

11.在一些实施方式中,所述控制电路包括看门狗芯片电路,所述看门狗芯片电路的输入端连接所述处理芯片的所述目标信号输出接口,所述看门狗芯片电路的输出端连接所述缓冲器电路的使能端;

12.所述看门狗芯片电路在一个定时周期内未接收到所述处理芯片发送的喂狗信号,向所述缓冲器电路输出低电平复位信号;所述看门狗芯片电路在一个定时周期内接收到所述处理芯片发送的喂狗信号,向所述缓冲器电路输出高电平控制信号。

13.在一些实施方式中,所述缓冲器电路的使能端接收到所述看门狗芯片发送的低电平复位信号时,控制所述第一端和所述第二端断开;所述缓冲器电路的使能端接收到所述

看门狗芯片发送的高电平控制信号时,控制所述第一端和所述第二端导通。

14.在一些实施方式中,所述控制电路包括可编程芯片电路,所述可编程芯片电路的输入端连接所述处理芯片的所述目标信号输出接口,所述可编程芯片电路的输出端连接所述缓冲器电路的使能端;

15.所述可编程芯片电路响应于未接收到所述处理芯片发送的所述目标信号,向所述缓冲器电路输出低电平信号;响应于接收到所述处理芯片发送的所述目标信号,向所述缓冲器电路输出高电平信号。

16.在一些实施方式中,所述缓冲器电路的使能端接收到所述可编程芯片电路发送的低电平信号时,控制所述第一端和所述第二端断开;所述缓冲器电路的使能端接收到所述可编程芯片电路发送的高电平信号时,控制所述第一端和所述第二端导通。

17.在一些实施方式中,所述可编程芯片电路包括cpld芯片电路或者fpga芯片电路。

18.在一些实施方式中,所述处理芯片包括soc、mcu、cpu中至少之一。

19.第二方面,本公开实施方式提供了一种板卡,包括:

20.根据第一方面任意实施方式所述的gpio通信电路;和

21.至少一个功能芯片,所述功能芯片与所述处理芯片的所述gpio接口连接。

22.第三方面,本公开实施方式提供了一种电子设备,包括:

23.根据第二方面任意实施方式所述的板卡。

24.本公开实施方式的gpio通信电路,包括处理芯片和检测电路,处理芯片包括gpio接口和目标信号输出接口,检测电路包括第一端、第二端及控制电路,第一端适于连接外部芯片电路,第二端连接处理芯片的gpio接口,控制电路连接处理芯片的目标信号输出接口,响应于接收到目标信号输出接口输出的目标信号,控制电路控制第一端和第二端导通,目标信号为周期性电平变化信号。本公开实施方式中,利用检测电路控制处理芯片与对端芯片的gpio通信的通断,在处理芯片非正常工作状态下,可以控制处理芯片与对端芯片实现gpio通信隔离,降低输出错误信号导致芯片工作错误或者管脚损坏的风险,提高芯片间gpio通信可靠性和安全性。

附图说明

25.为了更清楚地说明本公开具体实施方式或现有技术中的技术方案,下面将对具体实施方式或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本公开的一些实施方式,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

26.图1根据本公开一些实施方式中gpio通信电路的示意图。

27.图2根据本公开一些实施方式中gpio通信电路的示意图。

28.图3根据本公开一些实施方式中gpio通信电路的示意图。

29.图4根据本公开一些实施方式中gpio通信电路的示意图。

具体实施方式

30.下面将结合附图对本公开的技术方案进行清楚、完整地描述,显然,所描述的实施方式是本公开一部分实施方式,而不是全部的实施方式。基于本公开中的实施方式,本领域

普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施方式,都属于本公开保护的范围。此外,下面所描述的本公开不同实施方式中所涉及的技术特征只要彼此之间未构成冲突就可以相互结合。

31.随着芯片技术的发展,芯片集成的功能也越来越多,目前芯片大多采用gpio(general-purpose input/output,通用型输入/输出接口)进行设备间通信。使用gpio可以利用软件模拟成熟的通信协议,例如i2c(inter-integrated circuit,同步串行总线)、uart(universal asynchronous receiver/transmitter,通用异步收发传输器)、spi(serial peripheral interface,串行外设接口)等协议。

32.但是,使用gpio通信时,在芯片非正常工作情况下,往往会出现各种非预期的效果,导致芯片间的通信管脚损伤,甚至导致芯片器件损毁。

33.以soc(system on chip,系统级芯片)为例,soc可以通过gpio接口与对端芯片进行通信,例如soc的gpio接口可以模拟i2c协议与对端芯片实现i2c通信。在通信过程中,本案发明人研究发现,在soc刚上电尚未正常启动或者soc挂死时,gpio接口经常出现以下非预期效果:

34.挂死i2c总线;

35.预期为输入信号,但实际为输出信号,与对端芯片输出信号电平冲突,导致双方芯片管脚损伤;

36.预期为输出信号,但实际为输入信号,导致对端芯片无法接收信号,引起工作异常;

37.输出信号电平异常,导致soc实际输出非预期的电平或波形,对端芯片信号接收错误,引起工作异常。

38.由此可见,相关技术中,芯片采用gpio通信时,可能会导致本端芯片和对端芯片出现工作异常或者管脚损伤,严重时甚至造成芯片损毁。

39.基于上述缺陷,本公开实施方式提供了一种gpio通信电路以及具有该gpio通信电路的板卡,旨在提高芯片间利用gpio通信时的可靠性和安全性,降低出现非预期效果的风险。

40.第一方面,本公开实施方式提供了一种gpio通信电路,该电路可应用于任何具有gpio接口的处理芯片中,以此实现处理芯片与对端芯片gpio通信的可靠性。

41.在一些实施方式中,本公开实施方式的gpio通信电路包括处理芯片,处理芯片包括gpio接口和目标信号输出接口。

42.处理芯片可以包括例如cpu(central processing unit,中央处理器)、mcu((microcontroller unit,微控制单元)、soc等芯片,本公开对此不作限制。

43.处理芯片的一个或者多个管脚可以用作实现gpio接口,从而处理芯片可以通过这些gpio接口实现与外部芯片或器件的gpio通信。本公开实施方式中,将以一个gpio接口为例,对本公开通信电路的结构和原理进行说明,但是本领域技术人员可以理解,对于处理芯片的多个gpio接口,均可以利用本公开实施方式的电路结构实现高可靠性的gpio通信。

44.目标信号输出接口是指处理芯片用于输出高低电平变化的接口。可以理解,数据通信本质上即为高低电平按照预设时钟周期进行信号传输的过程。本公开实施方式中,目标信号即是指处理芯片产生的周期性的高低电平变化信号。

45.因此,目标信号输出接口并不局限于处理芯片的某一个固定的管脚,只要能够用于信号输出的管脚均可作为本公开所述的目标信号输出接口。例如一个示例中,同样可将处理芯片的某个gpio接口作为目标信号输出接口,当然,也可以将其他输出接口作为目标信号输出接口,例如i2c接口等,本领域技术人员对此可以理解,本公开不再赘述。

46.另外,值得说明的是,处理芯片只有在正常工作的情况下,才会输出符合预期的周期性变化的高低电平信号。处理芯片的非正常工作状态,可以分为处理芯片刚上电至正常启动的启动阶段,以及处理芯片挂死的挂死阶段。

47.在启动阶段,处理芯片首先需要上电,电源为芯片提供工作时钟信号(clk),然后reset信号解复位,芯片从存储器中加载软件文件,根据软件文件初始化各个接口,直至初始化完成完成启动,开始正常工作。

48.在此过程中,处理芯片的输出接口无法输出周期性变化的高低电平信号,甚至gpio接口可能会输出错误的信号,如前述所言,可能会导致处理芯片或者对端芯片工作异常或者管脚损伤。

49.处理芯片在挂死阶段同理,处理芯片在工作过程中由于某些原因导致进入挂死状态,从而导致总线电平一直被拉高或拉低,总线无法被释放,导致整个总线上的通讯被暂停。在此阶段,处理芯片的输出接口也无法输出周期性变化的高低电平信号。

50.从而本公开实施方式中,可以为处理芯片与对端芯片的gpio通信链路设计一个检测电路,该检测电路可以检测目标信号输出接口输出的目标信号,目标信号即为处理芯片输出的周期性变化的高低电平信号。当检测电路接收到该目标信号时,表示当前处理芯片处于正常工作状态,此时gpio通信不会出现异常,即可控制处理芯片与对端芯片的gpio通信链路导通。反之,当检测电路接收不到该目标信号时,表示当前处理芯片尚未正确启动或者处于挂死状态,此时若是gpio通信链路保持通信,可能会造成工作错误或者双方芯片管脚损伤,因此可以控制处理芯片与对端芯片的gpio通信链路断开。

51.具体而言,本公开实施方式的检测电路包括第一端、第二端以及控制电路。检测电路的第二端连接处理芯片的gpio接口,第一端可用于连接外部芯片电路,这样,当检测电路的第一端与第二端导通时,处理芯片即可与外部芯片实现gpio通信,反之,当检测电路的第一端与第二端断开时,处理芯片与外部芯片的gpio通信中断。

52.控制电路连接处理芯片的目标信号输出接口,控制电路可根据目标信号输出接口输出的目标信号来控制检测电路的第一端和第二端的通断。具体来说,当控制电路检测到处理芯片的目标信号输出接口输出目标信号时,表示处理芯片当前处于正常工作状态,控制电路控制检测电路的第一端和第二端导通,从而处理芯片与外部芯片通过gpio接口实现通信。反之,当控制电路检测到处理芯片的目标信号输出接口未输出目标信号时,目标信号为周期性电平变化信号,若处理芯片未输出目标信号,表示处理芯片当前处于非正常状态,例如处理芯片尚未正确启动,或者处理芯片挂死等,此时控制电路控制检测电路的第一端和第二端断开,从而处理芯片与外部芯片的gpio通信链路中断。

53.通过上述可知,本公开实施方式中,利用检测电路控制处理芯片与对端芯片的gpio通信的通断,在处理芯片非正常工作状态下,可以控制处理芯片与对端芯片实现gpio通信隔离,降低输出错误信号导致芯片工作错误或者管脚损坏的风险,提高芯片间gpio通信可靠性和安全性。

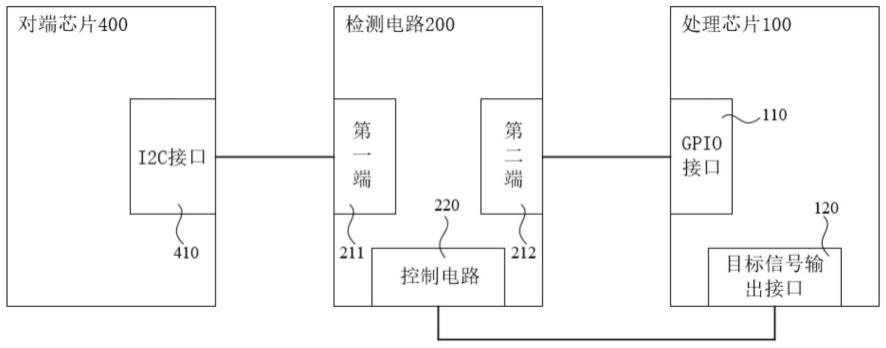

54.图1示出了本公开一些实施方式中gpio通信电路的电路结构图,下面结合图1进行说明。

55.在图1示例中,利用本公开实施方式的gpio通信电路实现处理芯片100与对端芯片400的gpio通信,并且,本示例中以处理芯片100的gpio接口110模拟i2c接口与对端芯片400的i2c接口410进行通信为例进行说明。

56.当然,本领域技术人员可以理解,本公开实施方式中,处理芯片100的gpio接口110也可以模拟其他任何适于实施的通信接口,例如uart、spi等,本公开对此不作限制。

57.如图1所示,通信电路包括处理芯片100、检测电路200以及对端芯片400。

58.对端芯片400包括i2c接口410,对端芯片400可以通过i2c接口410与其他器件建立i2c协议的通信连接。本公开实施方式中,正是利用处理芯片100的gpio接口110来模拟i2c接口,与对端芯片400的i2c接口410实现i2c通信连接。

59.处理芯片100包括至少一个gpio接口110,gipo接口110可以通过软件来模拟各种通信协议,例如本示例中,可以利用gpio接口110模拟i2c通信协议,与对端芯片400的i2c接口410建立i2c通信连接。

60.处理芯片100还包括目标信号输出接口120,目标信号输出接口120用于输出电平信号,在处理芯片100正常工作时,目标信号输出接口120可以输出周期性变化的高低电平信号。

61.可以理解,目标信号输出接口120可以是处理芯片100任意类型的输出接口,例如一个示例中,目标信号输出接口120同样可以是gpio接口,只不过该gpio接口输出的信号不再作为数据通信,而是作为目标信号发送至控制电路220。当然,目标信号输出接口120也可以是其他输出接口,本公开对此不作限制。

62.检测电路200包括第一端211、第二端212以及控制电路220。第一端211与对端芯片400的i2c接口410连接,第二端212与处理芯片100的gpio接口110连接。控制电路220与处理芯片100的目标信号输出接口120连接,控制电路220可以根据目标信号输出接口120输出的目标信号控制检测电路200的第一端211与第二端212的通断。

63.例如一个示例中,控制电路220在接收到目标信号时,可以控制第一端211与第二端212导通,此时处理芯片100即可通过gpio接口110与对端芯片400的i2c接口410建立通信连接。反之,控制电路220在未接收到目标信号时,可以控制第一端211与第二端212断开,此时处理芯片100的gpio接口110与对端芯片400的i2c接口410的通信中断。

64.在一些实施方式中,检测电路200还可以包括缓冲器电路,缓冲器也叫缓冲寄存器(buffer),其多用在总线上,可以起到隔离前后级的作用,因此,本公开一些实施方式中,即可利用缓冲器电路(buffer)实现对端芯片400和处理芯片100的隔离,下面结合图2进行说明。

65.如图2所示,在一些实施方式中,检测电路200包括缓冲器电路210和控制电路220。

66.在本示例中,缓冲器电路210也即i2c buffer,其包括第一端211、第二端212以及使能端213。使能端213用于接口控制信号,从而根据控制信号的高低电平来控制第一端211和第二端212的通断。

67.控制电路220包括输入端221和输出端222,输入端221与处理芯片100的目标信号输出接口120连接,输出端222与缓冲器电路210的使能端213连接。

68.本公开实施方式中,控制电路220的输入端221在接收到处理芯片100发送的目标信号时,可通过输出端222向缓冲器电路210的使能端213发送高电平的控制信号,缓冲器电路210根据控制信号控制第一端211和第二端212导通。反之,控制电路220的输入端221未接收到处理芯片100发送的目标信号时,可通过输出端222向缓冲器电路210的使能端213发送低电平信号,从而缓冲器电路210不使能,第一端211与第二端212断开。

69.在一些实施方式中,控制电路220可以通过看门狗芯片实现,看门狗芯片作为监控芯片,其结构简单成本低。在另一些实施方式中,控制电路220也可以通过例如cpld(complex programmable logic device,复杂可编程逻辑器件)、fpga(field programmable gate array,现场可编程逻辑门阵列)等可编程芯片电路实现,可以根据场景需求对控制电路220进行对应编程,适应性更强。本公开下文实施方式中分别对其进行说明。

70.图3示出了本公开通信电路的一些实施方式,在图3示例中,控制电路220利用看门狗芯片电路实现,下面结合图3进行说明。

71.如图3所示,在本示例中,看门狗芯片电路包括输入端wdi以及输出端reset。看门狗芯片电路本质上是一个定时器电路,在每个定时周期wdt内需要有喂狗信号输入,若程序在某种意外情况下跑飞,看门狗芯片电路在一个定时周期内无法接到喂狗信号,则输出端输出复位信号,将芯片进行复位。

72.基于此原理,看门狗芯片电路应用至本公开实施方式的通信电路中时,即可将看门狗芯片电路的输入端wdi与处理芯片100的目标信号输出接口120连接,目标信号本身即为周期性变化的高低电平信号,从而通过调整目标信号的周期小于看门狗芯片电路的定时周期,目标信号即可作为喂狗信号,每隔预设周期,目标信号输出接口120即可向看门狗芯片电路的输入端wdi发送一个喂狗信号。

73.本公开实施方式中,在处理芯片100正常工作的情况下,处理芯片100的目标信号输出接口120即可周期性输出喂狗信号,看门狗芯片电路的输入端wdi在每个定时周期内均会接收到一个喂狗信号,从而输出端即可输出高电平控制信号。缓冲器电路210的使能端213接收到高电平控制信号,即可使能控制第一端211和第二端212导通,此时,处理芯片100的gpio接口110即可与对端芯片400的i2c接口410通信连接。

74.在处理芯片100非正常工作(例如处理芯片100挂死或者未正确启动)的情况下,处理芯片100的目标信号输出接口120无法稳定输出周期性的喂狗信号,在某个定时周期内,若看门狗芯片电路的输入端wdi无法接收到喂狗信号,从而输出端即可输出低电平复位信号。缓冲器电路210的使能端213由于接收到的是低电平复位信号,从而不使能,第一端211和第二端212即断开,此时,处理芯片100的gpio接口110与对端芯片400的i2c接口410的通信断开。

75.在一些实施方式中,看门狗芯片电路可以选择例如max706、sp706等看门狗芯片实现。

76.通过上述可知,本公开实施方式中,利用检测电路控制处理芯片与对端芯片的gpio通信的通断,在处理芯片非正常工作状态下,可以控制处理芯片与对端芯片实现gpio通信隔离,降低输出错误信号导致芯片工作错误或者管脚损坏的风险,提高芯片间gpio通信可靠性和安全性。并且,看门狗芯片结构简单成本低,降低部署成本。

77.图4示出了本公开通信电路的一些实施方式中,在图4示例中,控制电路220利用cpld或者fpga等可编程芯片电路实现,下面结合图4进行说明。

78.如图4所示,在本示例中,可编程芯片电路包括输入端221和输出端222,输入端221与处理芯片100的目标信号输出接口120连接,输出端222与缓冲器电路210的使能端213连接。

79.本公开实施方式中,可编程芯片电路可以检测目标信号输出接口120输出的信号是否为周期性变化的高低电平信号,也即本公开所述的目标信号。

80.在处理芯片100正常工作的情况下,处理芯片100的目标信号输出接口120即可输出周期性变化的高低电平信号,也即目标信号,可编程芯片电路检测到该目标信号,输出端222即可向缓冲器电路210的使能端213发送高电平信号。缓冲器电路210的使能端213接收到高电平信号,即可使能控制第一端211和第二端212导通,此时,处理芯片100的gpio接口110即可与对端芯片400的i2c接口410通信连接。

81.在处理芯片100非正常工作(例如处理芯片100挂死或者未正确启动)的情况下,处理芯片100的目标信号输出接口120无法稳定输出周期性变化的高低电平信号,也即可编程芯片电路无法检测到目标信号,输出端222即可向缓冲器电路210的使能端213发送低电平信号。缓冲器电路210的使能端213由于接收到的是低电平信号,从而不使能,第一端211和第二端212即断开,此时,处理芯片100的gpio接口110与对端芯片400的i2c接口410的通信断开。

82.在一些实施方式中,可编程芯片电路可包括例如cpld(complex programmable logic device,复杂可编程逻辑器件)、fpga(field programmable gate array,现场可编程逻辑门阵列)等,本公开对此不作限制。

83.通过上述可知,本公开实施方式中,利用检测电路控制处理芯片与对端芯片的gpio通信的通断,在处理芯片非正常工作状态下,可以控制处理芯片与对端芯片实现gpio通信隔离,降低输出错误信号导致芯片工作错误或者管脚损坏的风险,提高芯片间gpio通信可靠性和安全性。并且,可编程芯片电路功能更为丰富,通信电路适应性更强。

84.另外,值得说明的是,上述以gpio接口模拟i2c通信为例进行了说明,事实上,本公开实施方式的gpio通信电路并不局限于模拟i2c通信,还可以是例如uart、spi通信等。

85.在一些实施方式中,当利用gpio接口模拟i2c等双向通信接口时,缓冲器电路210可以采用例如tca9801、pca9615、pca9515等i2c带使能端的双向buffer/repeator。当利用gpio接口模拟uart等单向通信信号时,缓冲器电路210可以采用例如sn74auc1g126、74hc1g126等带使能端的单向buffer。本领域技术人员对此可以理解,本公开不再赘述。

86.第二方面,本公开实施方式提供了一种板卡,该板卡包括前述任意实施方式的gpio通信电路,以及至少一个功能芯片。本公开实施方式中,功能芯片即可为上述实施方式中的对端芯片400,对此不再赘述。

87.可以理解,本公开实施方式中,对板卡的具体类型不作限制,其可以是任何适于实施的板卡类型,例如pcie(peripheral component interconnect express,高速串行计算机扩展总线)板卡等。

88.第三方面,本公开实施例提供了一种电子设备,包括前述任意实施例提供的板卡。

89.通过上述可知,本公开实施方式中,板卡的各个芯片之间利用检测电路控制gpio

通信的通断,在本端芯片非正常工作状态下,可以控制本端芯片与对端芯片实现gpio通信隔离,降低输出错误信号导致芯片工作错误或者管脚损坏的风险,提高芯片间gpio通信可靠性和安全性。

90.显然,上述实施方式仅仅是为清楚地说明所作的举例,而并非对实施方式的限定。对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式的变化或变动。这里无需也无法对所有的实施方式予以穷举。而由此所引伸出的显而易见的变化或变动仍处于本公开创造的保护范围之中。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1