存储器系统中的冷数据检测器的制作方法

背景技术:

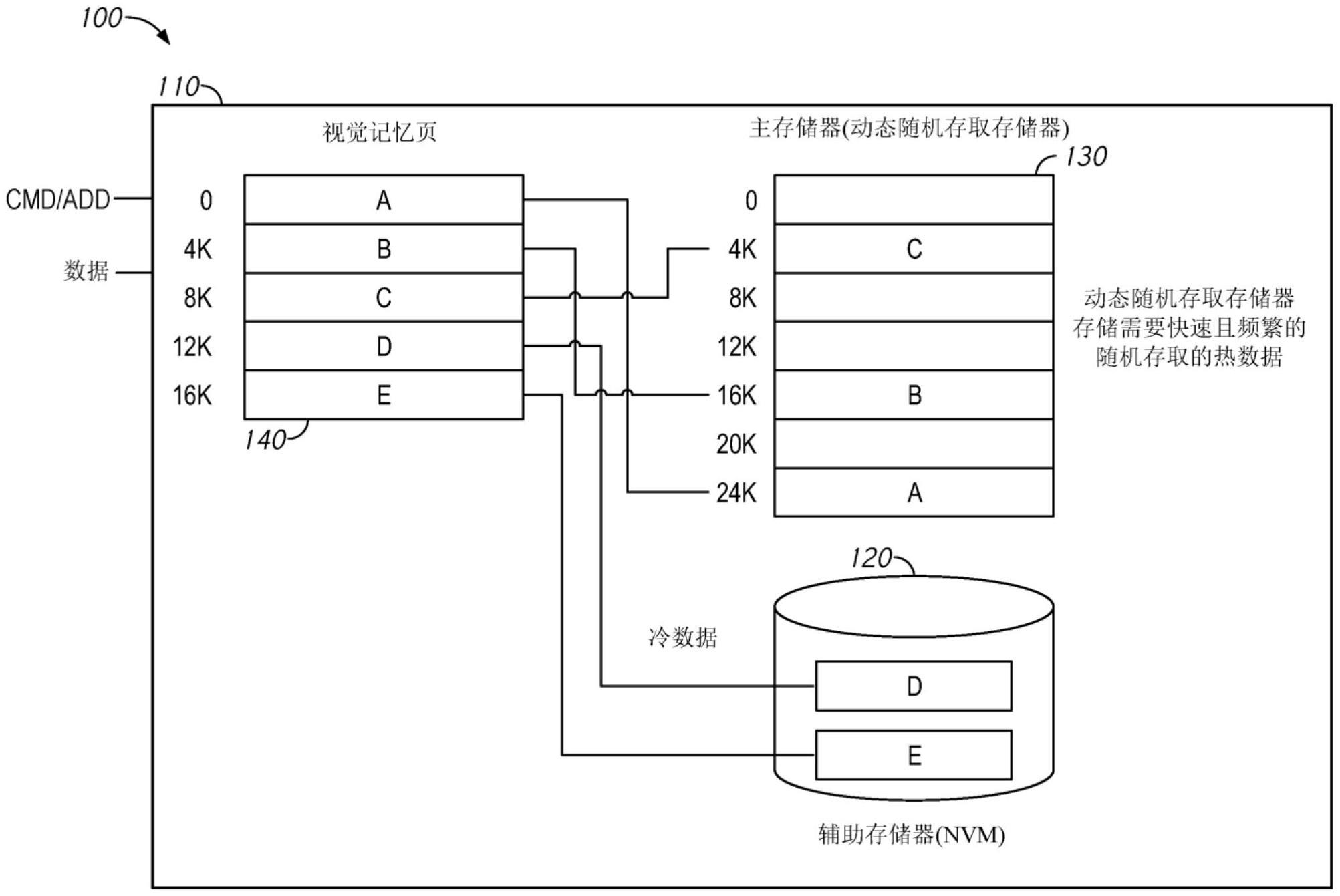

1、混合存储器系统可将频繁存取的数据存储在较低时延存储器中,并且可随着较低时延存储器内的可用存储空间减小而将较不频繁存取的数据(例如,冷数据)移动到较高时延存储器中。然而,较低时延存储器中用于检测冷数据的计数器和其它电路系统可消耗裸片上的额外功率和空间,这可减少存储容量且降低低时延存储器的性能。

技术实现思路

1、本文中描述了示例设备。一种示例设备可包含:存储器单元阵列,其包括多个排组,其中多个排组中的排组包含相应多个片段,所述相应多个片段各自与相应片段地址相关联;以及冷数据检测器电路,其对应于多个排组中的排组且包括寄存器,所述寄存器具有被配置成存储所接收片段地址的多个时隙。响应于检测到排组的相应多个片段中的每一个已经受至少一个存取操作,冷数据检测器电路可被配置成将来自寄存器的最长所存储片段地址提供到输出作为冷地址。另外或替代地,在与相应多个片段中的目标片段相关联的存取操作期间,在寄存器的多个时隙中指示为空的特定时隙之前的多个时隙中的每一时隙移位一个时隙以填充特定时隙,使得多个时隙中的第一末端时隙可用于接收与目标片段相关联的相应目标片段地址。另外或替代地,在特定时隙之后的多个时隙中的每一时隙保持现有相应片段地址。另外或替代地,在与相应多个片段中的目标片段相关联的存取操作期间,冷数据检测器电路被配置成将存储在寄存器处的相应片段地址与相应目标片段地址进行比较,并且响应于确定存储在寄存器处的相应片段地址中的一个与相应目标片段地址匹配,冷数据检测器电路被配置成使存储在寄存器处的相应片段地址中的所述一个无效且将相应目标片段地址存储在寄存器处。另外或替代地,所述示例设备可包含冷数据读出电路,所述冷数据读出电路具有被配置成存储冷地址为特定位置的移位寄存器。另外或替代地,存储器单元阵列进一步包含对应于多个排组中的第二排组的第二冷数据检测器电路,并且第二冷数据检测器电路包含第二寄存器,所述第二寄存器具有被配置成存储与第二排组的相应多个片段相关联的所接收片段地址的第二多个时隙。响应于检测到第二排组的相应多个片段中的每一个已经受至少一个存取操作,第二冷数据检测器电路被配置成将来自第二寄存器的最长所存储片段地址提供到输出作为第二冷地址。另外或替代地,所述示例设备可包含多个冷数据检测器电路,其包含所述冷数据检测器电路,所述多个冷数据检测器电路各自对应于多个排组中的相应排组,其中响应于检测到相应排组的相应多个片段中的每一个已经受至少一个存取操作,并且多个冷数据检测器电路中的每一个可被配置成提供来自相应寄存器的相应最长所存储片段地址作为相应冷地址。另外或替代地,所述示例设备可进一步包含冷数据读出电路,所述冷数据读出电路具有移位寄存器,所述移位寄存器具有多个时隙,所述多个时隙各自被配置成存储来自多个冷数据检测器电路中的特定一个的相应冷地址,并且冷数据读出电路可被配置成响应于从多个冷数据检测器中的每一个接收到排组填满信号而起始冷数据从存储器单元阵列到另一存储器的传送。另外或替代地,冷数据读出电路可进一步被配置成响应于冷数据从存储器单元阵列传送到另一存储器而更新模式寄存器。另外或替代地,存储器单元阵列可包含易失性存储器单元。另外或替代地,另一存储器可包含非易失性存储器。

2、一种第二示例设备可包含:第一存储器,其具有第一存取时延,以及第二存储器,其具有小于第一存取时延的第二存取时延。第二存储器可包含存储器单元阵列,所述存储器单元阵列包含多个排组,并且多个排组中的每一个可包含相应多个片段,所述相应多个片段各自与相应片段地址相关联。第二存储器可进一步包含多个冷数据检测器电路,所述多个冷数据检测器电路各自对应于多个排组中的相应一个且各自包括相应寄存器。相应寄存器中的每一个可被配置成存储片段地址,并且响应于检测到特定排组的每一片段已作为至少一个存取操作目标,多个冷数据检测器中的相应冷数据检测器被配置成将来自相应寄存器的相应最长所存储片段地址提供到冷数据读出电路。冷数据读出电路可响应于从多个冷数据检测器中的每一个接收到相应最长所存储片段地址而提供将冷数据从第一存储器传送到第二存储器的指示。另外或替代地,多个冷数据检测器中的一个的相应寄存器的深度小于对应于多个冷数据检测器中的所述一个的多个排组中的排组中的相应多个片段的计数。另外或替代地,冷数据读出电路包括移位寄存器,所述移位寄存器具有多个时隙,所述多个时隙各自被配置成存储来自多个冷数据检测器中的特定一个的相应最长所存储片段地址。另外或替代地,第一存储器和第二存储器是存储器模块或芯片上系统的部分。另外或替代地,第一存储器是非易失性存储器,并且第二存储器是易失性存储器。

3、本文中描述了示例方法。一种示例方法包含在与存储器单元阵列的具有多个片段的排组相关联的存取操作期间,将片段地址存储在冷数据检测器电路的寄存器处。片段地址可各自与多个片段中的相应片段相关联。所述示例方法进一步包含响应于检测到排组的多个片段中的每一个已被存取,将最长所存储片段地址传送到冷数据读出电路作为冷地址。另外或替代地,所述方法进一步包含在与多个片段中的目标片段相关联的存取操作期间,在寄存器的多个时隙中指示为空的特定时隙之前的多个时隙中的每一时隙移位一个时隙以填充特定时隙,使得多个时隙中的第一末端时隙可用于接收与目标片段相关联的相应目标片段地址。另外或替代地,所述方法进一步包含在与多个片段中的目标片段相关联的存取操作期间,将存储在寄存器处的相应片段地址与相应目标片段地址进行比较;以及响应于确定存储在寄存器处的相应片段地址中的一个与相应目标片段地址匹配,使存储在寄存器处的相应片段地址中的一个无效,并且将相应目标片段地址存储在寄存器处。另外或替代地,所述方法进一步包含响应于检测到排组的多个片段中的每一个已被存取,提供存储在寄存器的最后时隙中的相应片段地址作为最长所存储片段地址。另外或替代地,所述方法进一步包含响应于从对应于存储器单元阵列的多个排组的多个寄存器中的每一个接收到最长所存储片段地址,起始冷数据从存储器单元阵列到另一存储器的传送。另外或替代地,存储器单元阵列包含非易失性存储器单元,并且另一存储器包含非易失性存储器。

技术特征:

1.一种设备,其包括:

2.根据权利要求1所述的设备,其中在与所述相应多个片段中的目标片段相关联的存取操作期间,在所述寄存器的所述多个时隙中指示为空的特定时隙之前的多个时隙中的每一时隙移位一个时隙以填充所述特定时隙,使得所述多个时隙中的第一末端时隙可用于接收与所述目标片段相关联的相应目标片段地址。

3.根据权利要求2所述的设备,其中在所述特定时隙之后的所述多个时隙中的每一时隙保持现有相应片段地址。

4.根据权利要求2所述的设备,其中在与所述相应多个片段中的所述目标片段相关联的所述存取操作期间,所述冷数据检测器电路被配置成将存储在寄存器处的所述相应片段地址与所述相应目标片段地址进行比较,其中响应于确定存储在寄存器处的所述相应片段地址中的一个与所述相应目标片段地址匹配,所述冷数据检测器电路被配置成使存储在寄存器处的所述相应片段地址中的所述一个无效且将所述相应目标片段地址存储在所述寄存器处。

5.根据权利要求1所述的设备,其进一步包括冷数据读出电路,所述冷数据读出电路具有被配置成存储所述冷地址为特定位置的移位寄存器。

6.根据权利要求1所述的设备,其中所述存储器单元阵列进一步包含对应于所述多个排组中的第二排组的第二冷数据检测器电路,其中所述第二冷数据检测器电路包含第二寄存器,所述第二寄存器具有被配置成存储与所述第二排组的相应多个片段相关联的所接收片段地址的第二多个时隙,其中响应于检测到所述第二排组的所述相应多个片段中的每一个已经受至少一个存取操作,所述第二冷数据检测器电路被配置成将来自所述第二寄存器的最长所存储片段地址提供到输出作为第二冷地址。

7.根据权利要求1所述的设备,其进一步包括:

8.根据权利要求7所述的设备,其中所述冷数据读出电路进一步被配置成响应于所述冷数据从所述存储器单元阵列传送到另一存储器而更新模式寄存器。

9.根据权利要求7所述的设备,其中所述存储器单元阵列包含易失性存储器单元。

10.根据权利要求7所述的设备,其中所述另一存储器包含非易失性存储器。

11.一种设备,其包括:

12.根据权利要求11所述的设备,其中所述多个冷数据检测器中的一个的所述相应寄存器的深度小于对应于所述多个冷数据检测器中的所述一个的所述多个排组中的排组中的所述相应多个片段的计数。

13.根据权利要求11所述的设备,其中所述冷数据读出电路包括移位寄存器,所述移位寄存器具有多个时隙,所述多个时隙各自被配置成存储来自所述多个冷数据检测器中的特定一个的所述相应最长所存储片段地址。

14.根据权利要求11所述的设备,其中所述第一存储器和所述第二存储器是存储器模块或芯片上系统的部分。

15.根据权利要求11所述的设备,其中所述第一存储器是非易失性存储器,并且所述第二存储器是易失性存储器。

16.一种方法,其包括:

17.根据权利要求16所述的方法,其进一步包括在与所述多个片段中的目标片段相关联的存取操作期间,在所述寄存器的所述多个时隙中指示为空的特定时隙之前的多个时隙中的每一时隙移位一个时隙以填充所述特定时隙,使得所述多个时隙中的第一末端时隙可用于接收与所述目标片段相关联的相应目标片段地址。

18.根据权利要求17所述的方法,其进一步包括在与所述多个片段中的所述目标片段相关联的所述存取操作期间:

19.根据权利要求16所述的方法,其进一步包括响应于所述检测到所述排组的所述多个片段中的每一个已被存取,提供存储在所述寄存器的最后时隙中的所述相应片段地址作为所述最长所存储片段地址。

20.根据权利要求16所述的方法,其进一步包括响应于从对应于所述存储器单元阵列的多个排组的多个寄存器中的每一个接收到最长所存储片段地址,起始冷数据从所述存储器单元阵列到另一存储器的所述传送。

21.根据权利要求20所述的方法,其中所述存储器单元阵列包含非易失性存储器单元,并且所述另一存储器包含非易失性存储器。

技术总结

一种冷数据检测器电路包含气泡破裂寄存器,所述气泡破裂寄存器被配置成检测包含主存储器和辅助存储器的存储器系统中的冷数据。所述气泡破裂寄存器选择性地移位所接收片段地址以填充空时隙,而不必等到所述空时隙被移出末端时隙,并且可响应于所述寄存器的每个时隙填充有不同的相应片段地址而提供冷数据的指示。

技术研发人员:何源,外山大吾

受保护的技术使用者:美光科技公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!