用于多队列存储器控制器的信用方案的制作方法

背景技术:

1、计算机系统通常使用廉价且高密度的动态随机存取存储器(dram)芯片作为主存储器。现今销售的大多数dram芯片与由联合电子设备工程委员会(jedec)发布的各种双倍数据速率(ddr)dram标准兼容。ddr dram使用具有高速访问电路的常规dram存储器单元阵列来实现高传输率并且提高存储器总线的利用。ddr存储器控制器可以与多个ddr通道介接以便容纳更多dram模块,并且比使用单个通道更快地与存储器交换数据。例如,一些存储器控制器包括两个或四个ddr存储器通道。

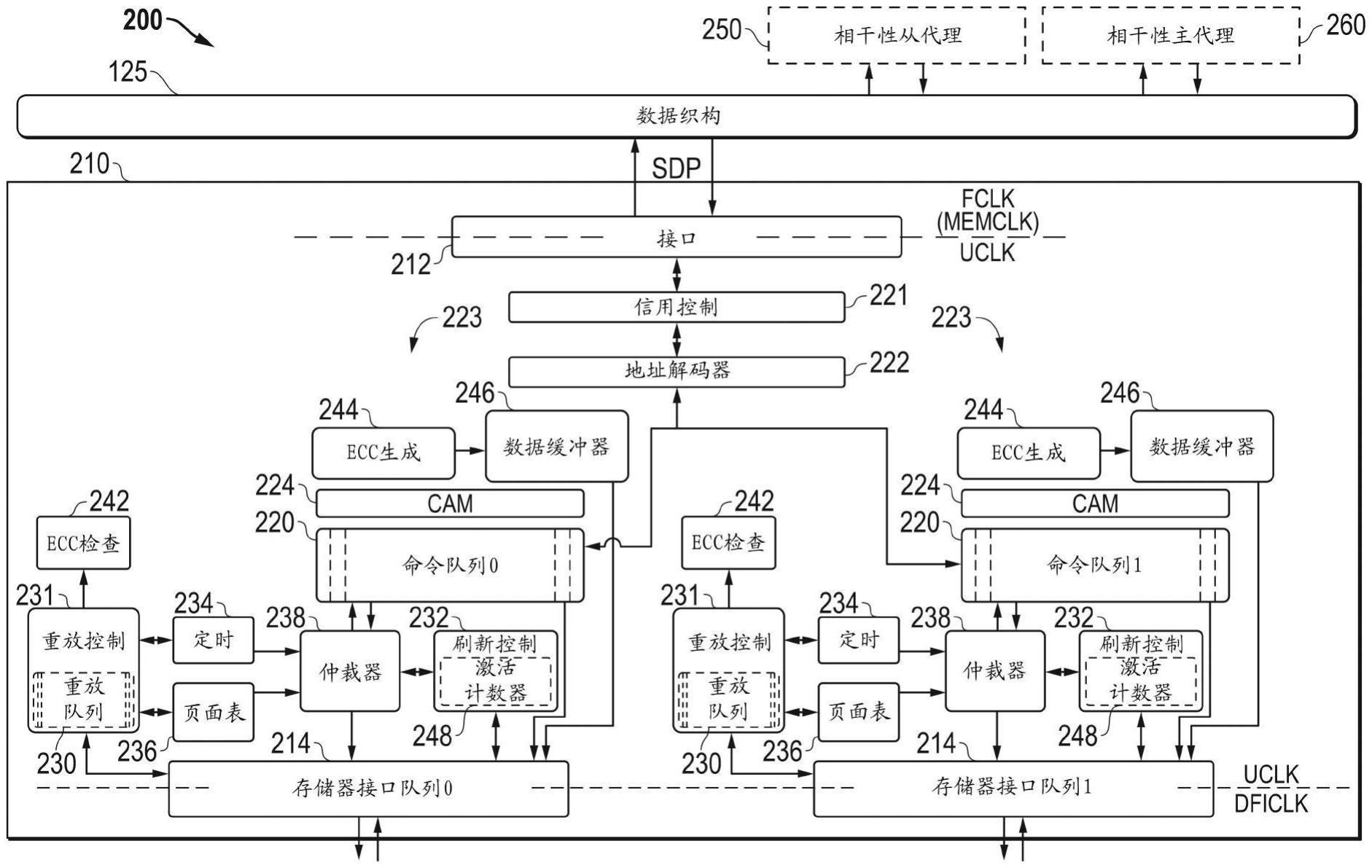

2、现代ddr存储器控制器维持队列以存储未决的存储器访问请求,从而允许这些控制器根据这些访问请求的生成或存储顺序来乱序地选取未决的存储器访问请求,以提高效率。为了防止存储器访问请求由于特定队列已满而被拒绝,存储器控制器的数据接口使用信用控制方案来控制存储器访问请求的流,在该信用控制方案中,将请求信用提供到主机系统的各个部分(诸如其数据接口织构),从而允许其发送用于进入命令队列中的存储器请求。存储器控制器还需要足够灵活,使得其可被配置用于不同存储器类型、密度和存储器通道拓扑,但这样做不需要为了支持这些不同模式而将增加芯片成本的大量附加电路面积。

技术实现思路

技术特征:

1.一种存储器控制器,包括:

2.根据权利要求1所述的存储器控制器,其中基于所述第一命令队列和所述第二命令队列的可用条目的数量来发出信用请求还包括:在未完成的请求信用的数量低于所述第一命令队列和所述第二命令队列的可用条目的最小数量的情形下,发出信用请求。

3.根据权利要求1所述的存储器控制器,其中所述请求信用控制电路耦接到数据处理单元的数据织构,并且可操作以通过所述数据织构向存储器访问代理发出请求信用。

4.根据权利要求1所述的存储器控制器,其中在接收到被分配到所述第一命令队列和所述第二命令队列中具有最高数量的可用条目的一者的存储器访问请求的情形下,所述请求信用控制电路可操作以发出请求信用,而不从所述第一命令队列或所述第二命令队列进行对应的解除分配。

5.根据权利要求1所述的存储器控制器,其中所述请求信用控制电路可操作以:响应于存储器访问请求从所述第一命令队列和所述第二命令队列中的一者解除分配,所述解除分配导致所述第一命令队列和所述第二命令队列具有相等数量的可用条目,在未完成的请求信用的所述数量低于所述相等数量的可用条目的情形下,则发出请求信用,并且在不低于的情形下,不响应于所述存储器访问请求被解除分配而发出请求信用。

6.根据权利要求1所述的存储器控制器,其中指定事件是存储器访问请求从所述第一命令队列和所述第二命令队列中的一者解除分配。

7.根据权利要求1所述的存储器控制器,还包括:

8.根据权利要求1所述的存储器控制器,其中所述地址解码器可操作以基于所述存储器访问请求的目标地址来将每个存储器访问请求引导到所述第一命令队列或所述第二命令队列。

9.根据权利要求1所述的存储器控制器,其中所述第一命令队列具有与所述第二命令队列不同的大小。

10.根据权利要求1所述的存储器控制器,还包括至少一个附加命令队列和耦接到所述附加命令队列的至少一个附加仲裁器,其中所述请求信用控制电路可操作以:响应于存储器访问请求从所述命令队列中的任何命令队列解除分配,在未完成的请求信用的数量低于所有所述命令队列当中的可用条目的最小数量的情形下,则发出请求信用,并且在不低于的情形下,不响应于所述存储器访问请求被解除分配而发出请求信用。

11.一种方法,包括:

12.根据权利要求11所述的方法,其中基于所述第一命令队列和所述第二命令队列的可用条目的数量来发出信用请求还包括:在未完成的请求信用的数量低于所述第一命令队列和所述第二命令队列的可用条目的最小数量的情形下,发出信用请求。

13.根据权利要求12所述的方法,还包括:在接收到被分配到所述第一命令队列和所述第二命令队列中具有最高数量的可用条目的一者的存储器访问请求的情形下,使得请求信用被发出,而不从所述第一命令队列或所述第二命令队列进行对应的解除分配。

14.根据权利要求12所述的方法,还包括:响应于存储器访问请求从所述第一命令队列和所述第二命令队列中的一者解除分配,所述解除分配导致所述第一命令队列和所述第二命令队列具有相等数量的可用条目,在未完成的请求信用的所述数量低于所述相等数量的可用条目的情形下,则使得存储器访问信用被发出,并且在不低于的情形下,不响应于所述存储器访问请求被解除分配而发出请求信用。

15.根据权利要求11所述的方法,其中所述指定事件是存储器访问请求从所述第一命令队列和所述第二命令队列中的一者解除分配。

16.根据权利要求11所述的方法,还包括:

17.根据权利要求11所述的方法,还包括基于所述存储器访问请求的目标地址来将每个存储器访问请求引导到所述第一命令队列或所述第二命令队列。

18.一种数据处理系统,包括:

19.根据权利要求18所述的数据处理系统,其中基于所述第一命令队列和所述第二命令队列的可用条目的数量来发出信用请求还包括:在未完成的请求信用的数量低于所述第一命令队列和所述第二命令队列的可用条目的最小数量的情形下,发出信用请求。

20.根据权利要求18所述的数据处理系统,其中基于所述第一命令队列和所述第二命令队列的可用条目的数量来发出信用请求还包括:在未完成的请求信用的数量低于所述第一命令队列和所述第二命令队列的可用条目的最小数量的情形下,发出信用请求。

21.根据权利要求18所述的数据处理系统,其中所述请求信用控制电路耦接到所述数据织构,并且可操作以通过所述数据织构向存储器访问代理发出请求信用。

22.根据权利要求18所述的数据处理系统,其中在接收到被分配到所述第一命令队列和所述第二命令队列中具有最高数量的可用条目的一者的存储器访问请求的情形下,所述请求信用控制电路可操作以发出请求信用,而不从所述第一命令队列或所述第二命令队列进行对应的解除分配。

23.根据权利要求18所述的数据处理系统,其中所述请求信用控制电路可操作以:响应于存储器访问请求从所述第一命令队列和所述第二命令队列中的一者解除分配,所述解除分配导致所述第一命令队列和所述第二命令队列具有相等数量的可用条目,在未完成的请求信用的所述数量低于所述相等数量的可用条目的情形下,则发出请求信用。

24.根据权利要求18所述的数据处理系统,还包括队列占用电路,所述队列占用电路可操作以计算所述请求信用控制电路的每个命令队列中的可用命令条目的当前数量。

25.根据权利要求18所述的数据处理系统,还包括:

26.根据权利要求18所述的数据处理系统,其中所述地址解码器可操作以基于所述存储器访问请求的目标地址来将每个存储器访问请求引导到所述第一命令队列或所述第二命令队列。

27.根据权利要求18所述的数据处理系统,其中所述存储器访问引擎是耦接到所述数据织构的相干性存储器从控制器,以用于实现来自至少一个数据处理单元的存储器访问请求。

28.根据权利要求18所述的数据处理系统,其中所述存储器访问引擎是耦接到所述数据织构的相干性存储器主控制器,以用于实现来自至少一个数据处理单元的存储器访问请求。

技术总结

本发明公开了一种存储器控制器,该存储器控制器包括地址解码器、耦接到该地址解码器的第一输出用于接收针对第一存储器通道的存储器访问请求的第一命令队列以及耦接到该地址解码器的第二输出用于接收针对第二存储器通道的存储器访问请求的第二命令队列。请求信用控制电路耦接到该第一命令队列和该第二命令队列,并且操作以跟踪未完成的请求信用的数量。该请求信用控制电路响应于指定事件,基于该第一命令队列和该第二命令队列的可用条目的数量来发出请求信用。

技术研发人员:凯达尔纳特·巴拉克里斯南,施瑞拉姆·拉维钱德兰

受保护的技术使用者:超威半导体公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!