数据织构时钟切换的制作方法

背景技术:

1、计算机系统通常使用廉价且高密度的动态随机存取存储器(dram)芯片作为主存储器。现今销售的大多数dram芯片与由联合电子设备工程委员会(jedec)发布的各种双倍数据速率(ddr)dram标准兼容。

2、存储器控制器是管理通过存储器总线去往和来自dram的数据流的数字电路。已知的存储器控制器从主机系统接收存储器访问请求,将其存储在队列中,并且以由仲裁器选择的次序将其分派给dram。存储器控制器通常用于根据一组定义的功率状态而改变其功率状态,以便满足计算机系统的存储器使用需求,同时在可能的情况下节省功率。通常,根据规范(诸如高级配置和电源接口(acpi)规范)来控制功率状态,该规范是用于计算机(诸如个人计算机(pc)和服务器)的功率管理和配置标准。acpi允许计算机操作系统通过从可以包括不同的操作频率、不同的电源电压和不同的操作模式的有限的一组模式当中改变设备的操作模式来管理在各个设备处消耗的功率。

技术实现思路

技术特征:

1.一种存储器控制器,包括:

2.根据权利要求1所述的存储器控制器,其中与所述第一时钟域的仅第一时钟信号的新频率同步的所述请求包括功率状态覆写信号和后续功率状态命令,所述功率状态覆写信号使得所述功率控制器当响应于与所述第一时钟域的改变相关联的后续功率状态命令时禁用所选择的存储器控制器时钟域状态改变电路和存储器时钟域状态改变电路。

3.根据权利要求2所述的存储器控制器,其中所述功率控制器还能够操作为:

4.根据权利要求2所述的存储器控制器,其中所述功率控制器还能够操作为:

5.根据权利要求4所述的存储器控制器,其中所述phy上的所述多组功率状态控制寄存器各自对应于连接至所述phy并且与所述存储器控制器相关联的动态随机存取存储器(dram)的所支持的功率状态。

6.根据权利要求1所述的存储器控制器,还包括锁相环路(pll),所述pll向所述第二时钟域供给时钟信号并且耦接至所述功率控制器。

7.一种方法,包括:

8.根据权利要求7所述的方法,其中使所述存储器控制器重新同步的所述请求包括功率状态覆写信号和后续功率状态命令,所述方法还包括当响应于与所述数据织构时钟域的改变相关联的后续功率状态命令时禁用所选择的存储器控制器时钟域状态改变电路和存储器时钟域状态改变电路。

9.根据权利要求7所述的方法,还包括:

10.根据权利要求7所述的方法,还包括:

11.根据权利要求10所述的方法,其中所述phy上的所述多组功率状态控制寄存器各自对应于连接至所述phy并且与所述存储器控制器相关联的动态随机存取存储器(dram)的所支持的功率状态。

12.根据权利要求7所述的方法,还包括:在没有先前功率状态命令覆写信号的情况下响应于功率状态命令而调整向所述存储器控制器时钟域供给时钟信号的锁相环路(pll)。

13.根据权利要求7所述的方法,还包括:在系统管理单元控制器处确定所述数据织构时钟域应当改变其操作频率,然后向所述存储器控制器发送所述功率状态命令覆写信号,使得所述数据织构时钟域改变其操作频率,以及向所述存储器控制器发送所述后续功率状态命令。

14.根据权利要求13所述的方法,其中所述后续功率状态命令包括功率状态数据,所述功率状态数据指示当前存储器控制器时钟域操作频率、当前存储器时钟域操作频率和经调节的数据织构时钟域操作频率。

15.一种数据处理系统,包括:

16.根据权利要求15所述的数据处理系统,其中使所述时钟接口电路与所述数据织构时钟域的仅第一时钟信号的新频率同步的所述请求包括功率状态覆写信号和后续功率状态命令,所述功率状态覆写信号使得所述功率控制器当响应于与所述数据织构时钟域的改变相关联的后续功率状态命令时禁用所选择的存储器控制器时钟域状态改变电路和存储器时钟域状态改变电路。

17.根据权利要求16所述的数据处理系统,其中所述功率控制器还能够操作为:

18.根据权利要求16所述的数据处理系统,其中所述功率控制器还能够操作为:

19.根据权利要求18所述的数据处理系统,其中所述phy上的所述多组功率状态控制寄存器各自对应于连接至所述phy并且与所述存储器控制器相关联的动态随机存取存储器(dram)的所支持的功率状态。

20.根据权利要求15所述的数据处理系统,还包括锁相环路(pll),所述pll向所述存储器控制器时钟域供给时钟信号并且耦接至所述功率控制器。

21.根据权利要求15所述的数据处理系统,还包括系统管理单元,所述系统管理单元耦接至所述数据织构并且能够操作为向所述存储器控制器发送所述功率状态命令和所述功率状态命令覆写信号。

22.根据权利要求21所述的数据处理系统,其中所述系统管理单元还能够操作为控制所述数据织构时钟域的操作频率。

技术总结

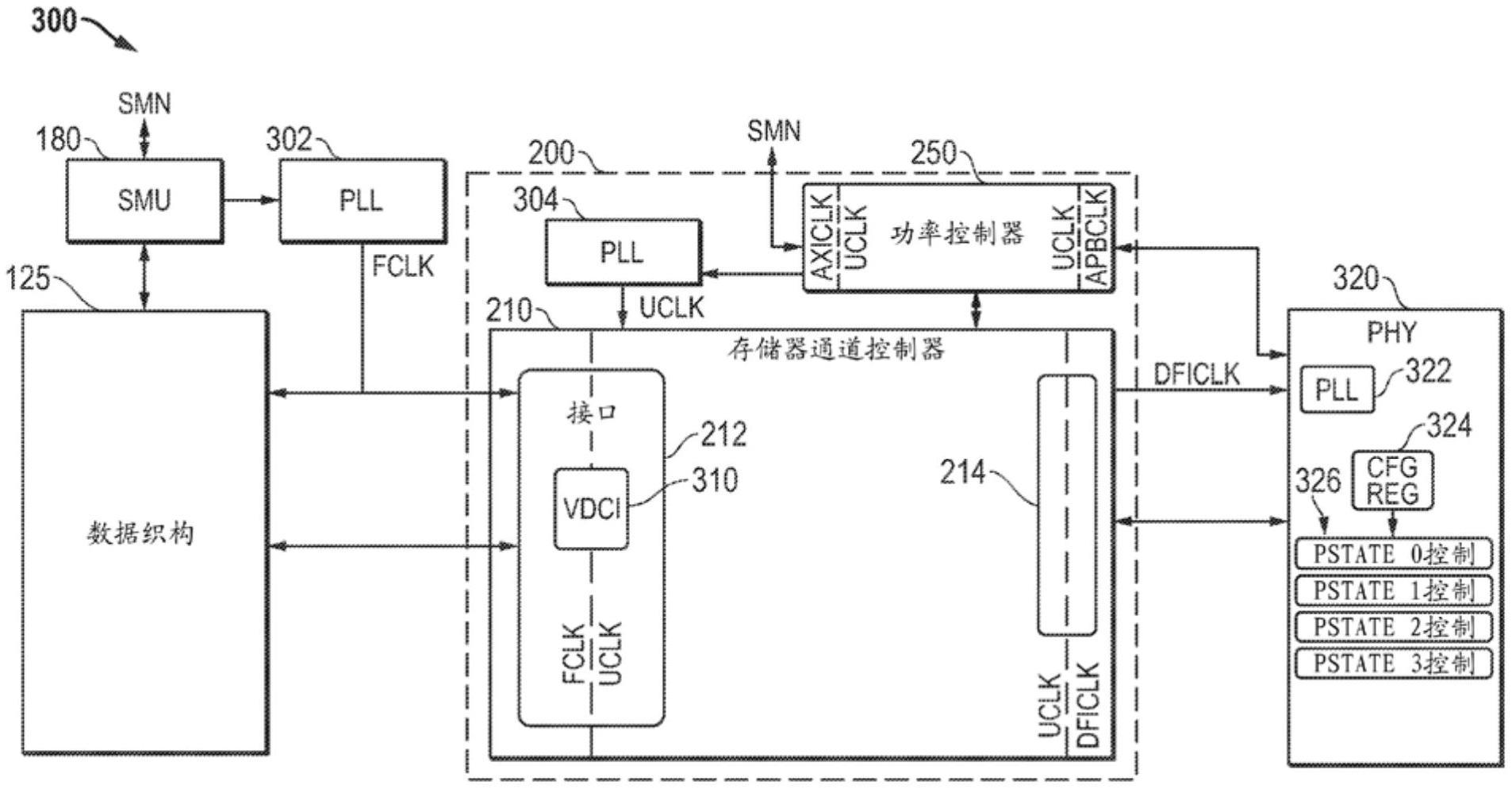

本发明公开了一种存储器控制器,该存储器控制器耦接至数据织构时钟域并且耦接至物理层接口电路PHY时钟域。第一接口电路调节该数据织构时钟域(FCLK)与存储器控制器时钟域之间的传送,并且第二接口电路将该存储器控制器耦接至该PHY时钟域。功率控制器通过将命令发送到该第二接口电路以改变存储器系统的参数来响应于功率状态改变请求,并且用于根据多个功率状态中的所选择的功率状态而更新该存储器控制器的一组定时参数。该功率控制器还通过改变该时钟接口电路的一组定时参数而不改变该存储器系统的一组定时参数或所选择的功率状态来响应于与该FCLK域上的新频率同步的请求。

技术研发人员:詹姆斯·R·马格罗,克里斯多夫·韦弗,阿布希克·库马尔·维尔马

受保护的技术使用者:超威半导体公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!