主机至宾客机通知的制作方法

背景技术:

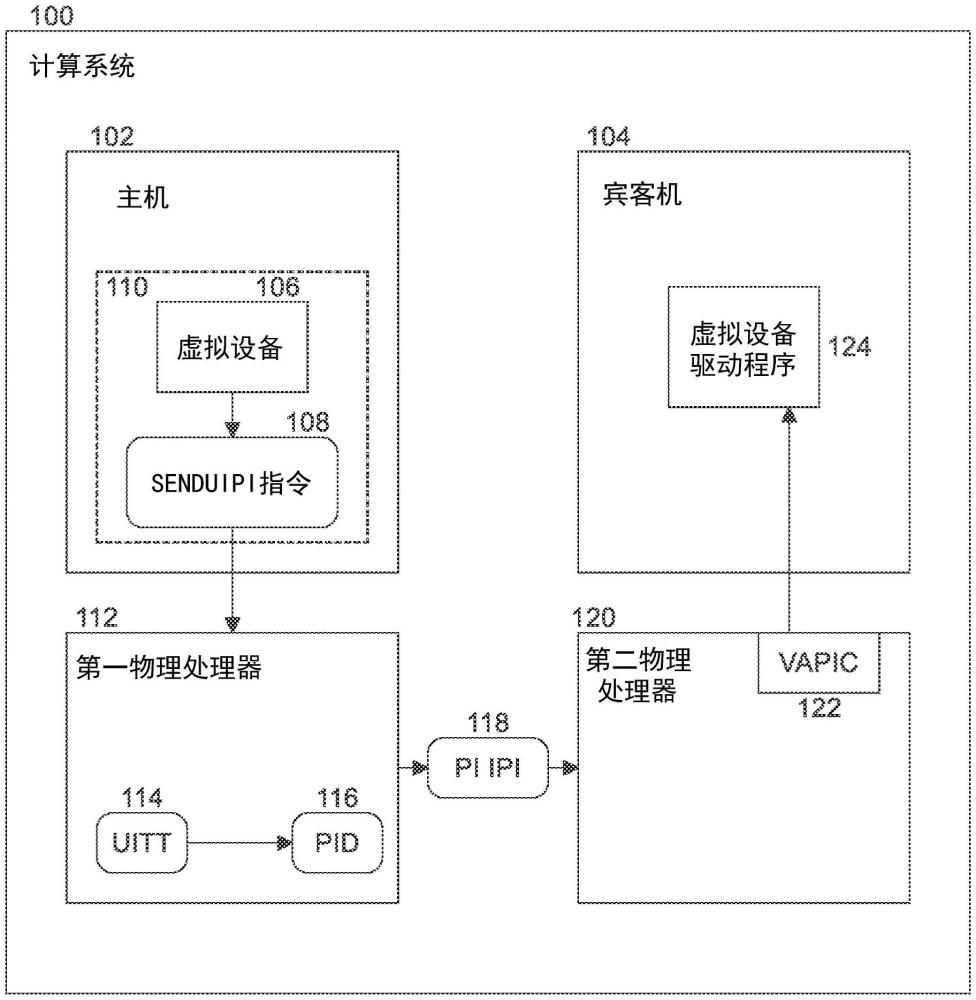

1、虚拟化数据中心被广泛用于提供数字服务,包括网络托管、流媒体服务、远程计算等。虚拟化数据中心具有高度可扩展性。虚拟化允许从单个物理硬件系统创建多个模拟环境、操作系统(operating system,os)或专用资源。虚拟化是使用软件实现的,诸如虚拟机管理器(virtual machine manager,vmm),其有时也称为管理程序,用于管理称为“宾客机”或虚拟机(vm)的软件。虚拟机是一种软件,其在适当的硬件上执行时,创建允许对实际物理计算机系统进行抽象的环境,也称为“主机(host或host machine)”。换言之,虚拟机是模拟物理计算机系统的软件。单个主机上可以运行多个虚拟机。与物理计算机系统类似,每个虚拟机都可以运行其自己的宾客操作系统(os)和应用,以及与外围设备(诸如外围组件互连快速(peripheral component interconnect express,pcie)设备)进行交互。

2、主机至宾客机(host to guest,h2g)通知是虚拟化环境中常见且频繁的操作。虚拟设备(例如,virtio-net设备)通常在主机环境上被仿真,并且虚拟设备驱动程序(例如,virtio-net驱动程序)在宾客机中运行。虚拟设备通常需要通知虚拟设备驱动程序来处理请求(例如,接收网络分组)。

技术实现思路

技术特征:

1.一种第一物理处理器,包括:

2.如权利要求1所述的第一物理处理器,其中,所述执行处理资源用于将通告中断(pi)处理器间通告中断(ipi)作为所述h2g通知发送至在所述宾客机中的所述虚拟处理器上运行所述虚拟设备驱动程序的所述第二物理处理器。

3.如权利要求1所述的第一物理处理器,其中,所述虚拟设备是所述第一物理处理器上的主机用户空间线程。

4.如权利要求1所述的第一物理处理器,其中,所述单个指令包括发送用户处理器间中断指令,并且在所述主机中运行的所述虚拟设备在所述第一物理处理器上执行所述senduipi指令。

5.如权利要求4所述的第一物理处理器,其中,所述执行处理资源用于从用户中断目标表(uitt)获得由所述发送用户处理器间中断指令的操作对象索引的条目,并且配置与所述uitt条目相关联的通告中断描述符(pid)。

6.如权利要求5所述的第一物理处理器,其中,被索引的uitt条目的pid类型字段指示所述被索引的uitt条目中的地址指向所述主机的通告中断描述符(pid)存储器中的pid格式的存储器位置。

7.一种方法,包括:

8.如权利要求7所述的方法,其中,包括将通告中断(pi)处理器间通告中断(ipi)作为所述h2g通知发送至在所述宾客机中的所述虚拟处理器上运行所述虚拟设备驱动程序的所述第二物理处理器。

9.如权利要求8所述的方法,其中,包括所述第二物理处理器响应于接收到所述pi ipi而通知所述虚拟设备驱动程序。

10.如权利要求7所述的方法,其中,所述虚拟设备是所述第一物理处理器上的主机用户空间线程。

11.如权利要求7所述的方法,其中,所述单个指令包括发送用户处理器间中断指令,并且在所述主机中运行的所述虚拟设备在所述第一物理处理器上执行所述发送用户处理器间中断指令。

12.如权利要求11所述的方法,其中,包括从用户中断目标表(uitt)获得由所述发送用户处理器间中断指令的操作对象索引的条目,并且配置与所述uitt条目相关联的通告中断描述符(pid)。

13.如权利要求12所述的方法,其中,被索引的uitt条目的pid类型字段指示所述被索引的uitt条目中的地址指向所述主机的通告中断描述符(pid)存储器中的pid格式的存储器位置。

14.一种系统,包括:

15.如权利要求14所述的系统,其中,所述执行处理资源用于将通告中断(pi)处理器间通告中断(ipi)作为所述h2g通知发送至在所述宾客机中的所述虚拟处理器上运行所述虚拟设备驱动程序的所述第二物理处理器核心。

16.如权利要求14所述的系统,其中,所述虚拟设备是所述第一物理处理器核心上的主机用户空间线程。

17.如权利要求14所述的系统,其中,所述单个指令包括发送用户处理器间中断指令,并且在所述主机中运行的所述虚拟设备在所述第一物理处理器核心上执行所述发送用户处理器间中断指令。

18.如权利要求17所述的系统,其中,所述执行处理资源用于从用户中断目标表(uitt)获得由所述发送用户处理器间中断指令的操作对象索引的条目,并且配置与所述uitt条目相关联的通告中断描述符(pid)。

19.如权利要求18所述的系统,其中,被索引的uitt条目的pid类型字段指示所述被索引的uitt条目中的地址指向所述主机的通告中断描述符(pid)存储器中的pid格式的存储器位置。

技术总结

公开了主机至宾客机(H2G)通知的方法和系统。H2G是经由指令提供的。指令是发送用户处理器间中断指令。示例性处理器包括:解码器电路,用于对单个指令解码,并且至少根据操作码执行经解码的单个指令,以引起从在第一物理处理器上的主机中运行的虚拟设备到在第二物理处理器上的宾客机中的虚拟处理器上运行的虚拟设备驱动程序的主机至宾客机通知。

技术研发人员:汪伟,田坤,曾光,G·尼格,R·桑卡兰,A·玛里克,J-S·蔡,J·J·潘,M·厄金

受保护的技术使用者:英特尔公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!