基于生成器模块化的加速器设计方法

本发明属于电子信息,涉及模块集成和加速器设计技术,尤其涉及一种基于生成器的模块化与设计空间探索的加速器设计方法。

背景技术:

1、生成器是一种采用高级且简单的工具描述以自动生成低级和详细的目标硬件,参数化ip、高层次综合hls和硬件构造语言(如chisel)都包含在生成器设计技术中。

2、在现有方法中,创建芯片生成器要创建定制的异构设计,最好从灵活的同构架构开始,因为它可以使验证和软件更容易。为了能够进行定制,必须从高度参数化和可扩展的模块构建架构的内部结构,以便应用程序设计人员可以轻松地塑造组件,创建适合特定应用程序需求的异构系统。最初创建这些灵活、可定制的模块也就是生成器的设计技术。

3、在生成器设计中,设计空间探索在优化和权衡中起着重要作用,其中性能建模是设计空间探索和不同应用关注不同指标的关键要素。基于模块化的设计方法包括三个阶段:模块分解、模块实现和模块集成。模块抽象包括模块接口和模块的信息描述,时序和加载的数据,以及寄存的输入和输出。随着自动化模块实现的发展,这些概念已经转变为接口定义、性能模型和内存管理。

4、然而,现有的加速器集成技术只能集成符合标准接口的ip,只能进行简单的集成;没有统一的性能模型指导集成的优化目标,也无法处理复杂的内存系统集成。

5、现有的加速器设计技术的缺陷在于:1、大多采用手动描述方法,缺乏一个准确的模块性能模型。而且生成器之间的性能模型不统一,大多数被设计为单独工作的模式;2、对于模块之间的接口,有一些标准和拓展可以用来描述集成ip的信息,但是没有可用的接口可以将生成器生成的模块进行紧密耦合3、内存管理:通常采用手动设计内存系统,但是由于内存系统是与生成模块同时生成的,这可能导致全局共享的内存系统和本地私有内存的层次结构之间发生冲突,在内存受限的应用场景下影响加速器性能。因此,现有的加速器设计技术由于性能模型不统一,且模块间不能紧密耦合导致有效性较低、生成的加速器由于内存受限导致性能不高。

技术实现思路

1、为了克服上述现有技术的不足,本发明提供一种基于生成器模块化的加速器设计方法(本发明命名为weave),包括显式定义接口和建立统一内存管理和性能模型,通过集成构建生成器模块来开发加速器,使得加速器具有高通信效率,模块化设计具有灵活性和高生产率,可促进特定领域加速器的敏捷设计的效率和性能。

2、常见领域的加速器可以分为两种架构,基于指令的加速器和基于数据流的加速器。基于指令的加速器的性能由包括数据依赖和分支控制在内的指令决定,而由基于数据流的加速器中的数据消耗和产生的速率决定。本发明中,模块化抽象设计的模块包括生成器的接口、内存访问模型、时序模型和资源模型。生成器模块化设计方法即通过将接口和性能分析模型与模块化抽象统一来消除加速器不同架构的差异,从而支持不同架构加速器的设计生成。

3、本发明提供的技术方案是:

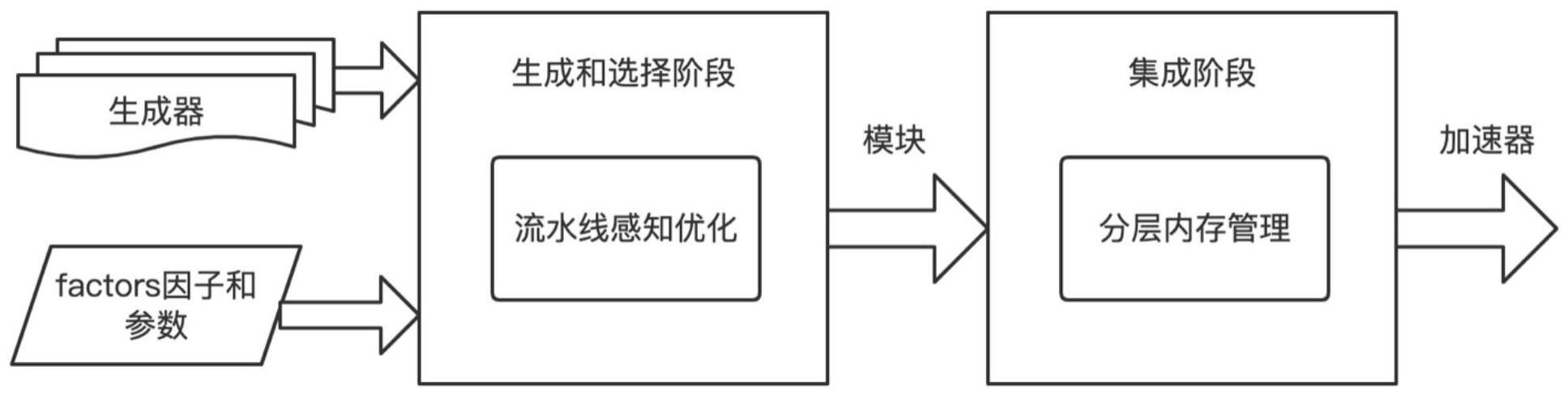

4、一种基于生成器模块化的加速器设计方法,通过建立一个两阶段流程(weave)实现。首先对生成器生成需要的模块进行预选,并且获取生成器生成需要的因子和参数,以指定优化的函数和约束。weave两阶段流程包括生成和选择阶段、集成阶段;将weave两阶段集成流程用于进行加速器的设计,包括基于指令的加速器和基于数据流的加速器。weave两阶段集成流程包括如下步骤:

5、1)在生成和选择阶段,通过设计流水线感知优化方法,得到待设计的目标加速器的设计架构即目标加速器的最优模块集;

6、在生成和选择阶段,设计流水线感知优化算法,协调加速器的设计空间和加速器系统性能(模型)之间的矛盾,使得保留尽可能多的可选模块以及通过避免过大的设计空间探索而导致开发时间过长;流水线感知优化算法用于决定加速器的有效的子设计空间并迭代的探索空间,得到加速器设计的最优模块集。

7、生成器设计方法是由设计者指定生成可选模块并根据优化函数和资源限制选择最佳组合,从而进行加速器的设计。一方面,对于系统性的考虑,有必要保留尽可能多的可选模块从而尽可能避免错过最佳选择,另一方面,保留尽可能多的可选模块这一点可能会导致过大的加速器设计空间探索,而导致加速器开发时间过长。因此,设计了流水线感知优化算法来解决这个问题。

8、流水线感知优化算法包括如下步骤:

9、2)在集成阶段,设计分层内存管理方法,对步骤1)生成的多个加速器最优模块的内存进行分组,并管理芯片的集成电路全局的片内和片外数据访问,从而完成目标加速器的设计;分层内存管理方法包括如下步骤:

10、21)定义目标加速器的接口;包括目标加速器的接口类型和接口协议;

11、22)对步骤1)生成的多个加速器最优模块的内存进行分组;

12、23)管理芯片的集成电路全局的片内和片外数据访问;

13、经过生成和选择阶段进行优化后得到目标加速器设计的架构。采用设计的架构作为目标加速器的主要框架。接口是模块集成中用于互连的关键元素,在生成模块的模块化抽象中定义目标加速器的接口。根据加速器设计采用的接口类型以及协议相互连接,为了适当连接模块,我们用加速器设计采用的接口的控制信号(信息)和数据传输对接口进行分类,即包括控制信号接口和数据传输接口。其中,接口类型即连接方式类型,接口协议(如axi-4协议)即数据传输的模式。对于紧密耦合的加速器的架构,将内存子系统保持在一个和谐的结构中,因为会影响不同模块之间存在冲突时的性能。此外,统一的全局内存访问模块会减少管理全局的开发成本。因此基于抽象的接口和内存访问,我们提出了分层内存管理方法以减少集成模块时对加速器性能的影响。

14、本发明从三个层次上设计内存管理:

15、加速器级别:本发明在加速器级别处理片上和片外之间的内存访问,将整个加速器当成通用dma模块。这个级别的关键设计是不同种类功能模块的dma模块的集成。保留来自于生成器的不同访问模式的支持,实现通用dma模块并为数据缓存提供全局内存部分。

16、模块间级别:当实现了一个独立的全局dma模块和全局内存,之后替换原有的dma模块并与全局内存访问连接。除此之外,还有模块之间多种模式的数据传输请求。本发明通过设计模块间级别的适合的内存管理方法,实现了合适的内存模块来缓存和重组数据,例如bram(block random-access memory,块随机存取存储器)用于基于模块化抽象的内存信息的批处理,fifo用于基于模块化抽象的内存信息的流处理。

17、内部模块级别:本发明不改变模块内部的本地内存,并且将其作为原始的私有类型。

18、分层内存管理方法包括如下步骤:

19、a)在加速器级别处理片上和片外之间的内存访问,将整个加速器当成通用直接存储器访问(direct memory access)dma模块。

20、b)在模块间级别处理多种模式的数据传输请求,设计模块间级别的适合的内存管理方法用于缓存和重组数据,实现合适的内存模块来缓存和重组排列数据。

21、c)在内部模块级别,不改变本地内存,并将其保留为原始的private类型。

22、通过上述步骤,实现基于生成器模块化的加速器设计方法,用于加速器的敏捷设计。

23、与现有技术相比,本发明的有益效果:

24、本发明提供一种基于生成器模块化的加速器设计方法,通过集成生成的模块来开发加速器,生成的加速器提高了通信效率,提升了加速器组成模块的灵活性,节省了加速器设计时间,有效促进了应用领域加速器的敏捷设计。

- 还没有人留言评论。精彩留言会获得点赞!