非易失性存储器标准NVMe指令的处理方法及相关装置与流程

本技术涉及存储,具体涉及一种非易失性存储器标准nvme指令的处理方法及相关装置。

背景技术:

1、虚拟化技术是云计算时代中最关键的技术之一。通过虚拟化技术,服务器主机可以向不同的租户提供所需的存储服务,从而提高了设备的利用率。延迟敏感型应用通常数据量较小,但需要设备提供较低的延迟,然而不同租户因为共享同一台服务器存储带宽,会出现其他租户和延迟敏感型应用程序相互竞争的问题,因为其他租户所产生的流量导致延迟敏感型应用程序性能降低问题。

技术实现思路

1、本技术实施例提供了一种非易失性存储器标准nvme指令的处理方法及相关装置,能够根据nvme请求指令中的低延迟标签和当前第一dma队列中缓存指令数,决定将第二dma指令发送到低延迟dma队列池还是第二dma队列,低延迟dma队列池和第二dma队列中dma指令采用不同的数据处理通道搬运应用程序的数据,使延迟敏感型应用的低延迟数据能够及时搬运到模拟磁盘,有利于提高延迟敏感型应用的运行性能。

2、第一方面,本技术实施例提供了一种非易失性存储器标准nvme指令的处理方法,应用于嵌入式虚拟化系统中的驱动模块,所述嵌入式虚拟化系统包括fpga控制器和所述驱动模块,所述fpga控制器分别与目标服务器和所述驱动模块连接,所述嵌入式虚拟化系统用于为所述目标服务器提供模拟nvme磁盘,所述fpga控制器用于接收所述目标服务器发送的nvme请求指令,并将所述nvme请求指令发送到所述驱动模块,所述驱动模块包括第一发送队列、第一dma队列、第一回收队列和所述模拟nvme磁盘,所述fpga控制器包括第二发送队列、第二dma队列、第二回收队列和低延迟dma队列池,所述低延迟dma队列池包括多个低延迟dma队列,所述第二dma队列与第一数据处理通道相对应,所述低延迟dma队列池与低延迟数据处理通道相对应,所述第二发送队列用于缓存所述fpga控制器接收到的所述nvme请求指令,所述第一发送队列用于缓存所述驱动模块接收到的所述nvme请求指令,所述方法包括:

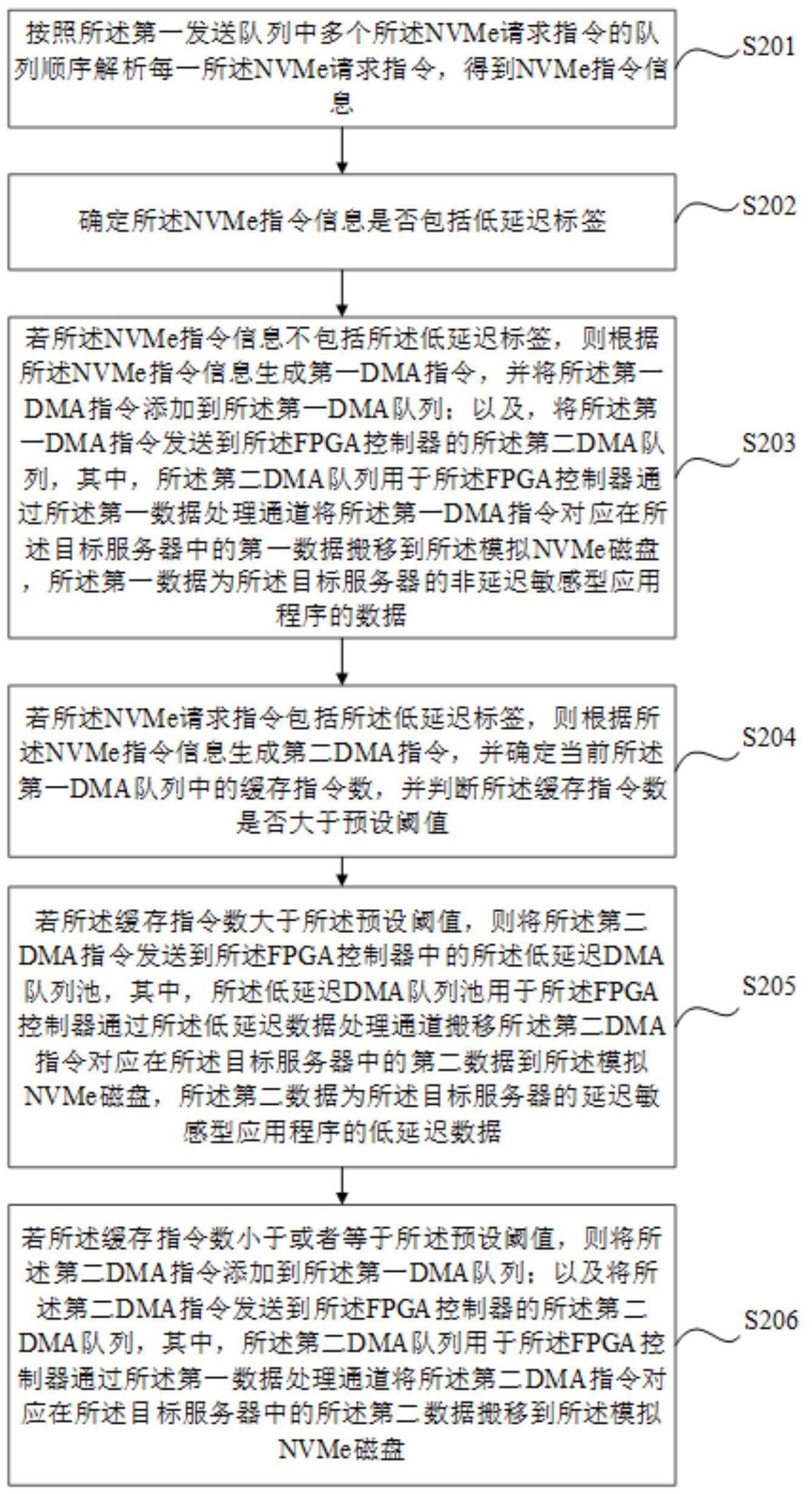

3、按照所述第一发送队列中多个所述nvme请求指令的队列顺序解析每一所述nvme请求指令,得到nvme指令信息;

4、确定所述nvme指令信息是否包括低延迟标签;

5、若所述nvme指令信息不包括所述低延迟标签,则根据所述nvme指令信息生成第一dma指令,并将所述第一dma指令添加到所述第一dma队列;以及,将所述第一dma指令发送到所述fpga控制器的所述第二dma队列,其中,所述第二dma队列用于所述fpga控制器通过所述第一数据处理通道将所述第一dma指令对应在所述目标服务器中的第一数据搬移到所述模拟nvme磁盘,所述第一数据为所述目标服务器的非延迟敏感型应用程序的数据;

6、若所述nvme请求指令包括所述低延迟标签,则根据所述nvme指令信息生成第二dma指令,并确定当前所述第一dma队列中的缓存指令数,并判断所述缓存指令数是否大于预设阈值;

7、若所述缓存指令数大于所述预设阈值,则将所述第二dma指令发送到所述fpga控制器中的所述低延迟dma队列池,其中,所述低延迟dma队列池用于所述fpga控制器通过所述低延迟数据处理通道搬移所述第二dma指令对应在所述目标服务器中的第二数据到所述模拟nvme磁盘,所述第二数据为所述目标服务器的延迟敏感型应用程序的低延迟数据;

8、若所述缓存指令数小于或者等于所述预设阈值,则将所述第二dma指令添加到所述第一dma队列;以及将所述第二dma指令发送到所述fpga控制器的所述第二dma队列,其中,所述第二dma队列用于所述fpga控制器通过所述第一数据处理通道将所述第二dma指令对应在所述目标服务器中的所述第二数据搬移到所述模拟nvme磁盘。

9、第二方面,本技术实施例提供了一种非易失性存储器标准nvme指令的处理方法,应用于目标服务器,所述目标服务器与嵌入式虚拟化系统中的fpga控制器连接,所述嵌入式虚拟化系统包括所述fpga控制器和驱动模块,所述fpga控制器分别与所述目标服务器和所述驱动模块连接,所述嵌入式虚拟化系统用于为所述目标服务器提供模拟nvme磁盘,所述fpga控制器用于接收所述目标服务器发送的nvme请求指令,并将所述nvme指令发送到所述驱动模块,所述驱动模块包括第一发送队列、第一dma队列、第一回收队列和所述模拟nvme磁盘,所述fpga控制器包括第二发送队列、第二dma队列、第二回收队列和低延迟dma队列池,所述低延迟dma队列池包括多个低延迟dma队列,所述第二dma队列与第一数据处理通道相对应,所述低延迟dma队列池与低延迟数据处理通道相对应,所述第二发送队列用于缓存所述fpga控制器接收到的所述nvme请求指令,所述第一发送队列用于缓存所述驱动模块接收到的所述nvme请求指令,所述fpga控制器还用于通过所述第一数据处理通道将所述第一dma指令对应在所述目标服务器中的第一数据搬移到所述模拟nvme磁盘、通过所述低延迟数据处理通道搬移所述第二dma指令对应在所述目标服务器中的第二数据到所述模拟nvme磁盘,以及通过所述第一数据处理通道搬移所述第二dma指令对应在所述目标服务器中的所述第二数据到所述模拟nvme磁盘,所述方法包括:

10、确定目标应用程序是否为延迟敏感型应用程序;

11、若所述目标应用程序为所述延迟敏感型应用程序,在发送所述目标应用程序对应的所述nvme请求指令到所述fpga控制器时,在所述nvme请求指令上添加低延迟标签;

12、接收所述fpga控制器发送的第一完成指令或者第二完成指令;

13、根据所述第一完成指令生成第一回收成功信号或者根据所述第二完成指令生成第二回收成功信号,并将所述第一回收成功信号或者所述第二回收成功信号通过所述fpga控制器发送到所述驱动模块。

14、第三方面,本技术实施例提供了一种非易失性存储器标准nvme指令的处理装置,应用于嵌入式虚拟化系统中的驱动模块,所述嵌入式虚拟化系统包括fpga控制器和所述驱动模块,所述fpga控制器分别与目标服务器和所述驱动模块连接,所述嵌入式虚拟化系统用于为所述目标服务器提供模拟nvme磁盘,所述fpga控制器用于接收所述目标服务器发送的nvme请求指令,并将所述nvme请求指令发送到所述驱动模块,所述驱动模块包括第一发送队列、第一dma队列、第一回收队列和所述模拟nvme磁盘,所述fpga控制器包括第二发送队列、第二dma队列、第二回收队列和低延迟dma队列池,所述低延迟dma队列池包括多个低延迟dma队列,所述第二dma队列与第一数据处理通道相对应,所述低延迟dma队列池与低延迟数据处理通道相对应,所述第二发送队列用于缓存所述fpga控制器接收到的所述nvme请求指令,所述第一发送队列用于缓存所述驱动模块接收到的所述nvme请求指令,所述装置包括:解析单元、确定单元、发送单元和判断单元,其中,

15、所述解析单元,用于按照所述第一发送队列中多个所述nvme请求指令的队列顺序解析每一所述nvme请求指令,得到nvme指令信息;

16、所述确定单元,用于确定所述nvme指令信息是否包括低延迟标签;

17、所述发送单元,用于若所述nvme指令信息不包括所述低延迟标签,则根据所述nvme指令信息生成第一dma指令,并将所述第一dma指令添加到所述第一dma队列;以及,将所述第一dma指令发送到所述fpga控制器的所述第二dma队列,其中,所述第二dma队列用于所述fpga控制器通过所述第一数据处理通道将所述第一dma指令对应在所述目标服务器中的第一数据搬移到所述模拟nvme磁盘,所述第一数据为所述目标服务器的非延迟敏感型应用程序的数据;

18、所述判断单元,用于若所述nvme请求指令包括所述低延迟标签,则根据所述nvme指令信息生成第二dma指令,并确定当前所述第一dma队列中的缓存指令数,并判断所述缓存指令数是否大于预设阈值;

19、所述发送单元,还用于若所述缓存指令数大于所述预设阈值,则将所述第二dma指令发送到所述fpga控制器中的所述低延迟dma队列池,其中,所述低延迟dma队列池用于所述fpga控制器通过所述低延迟数据处理通道搬移所述第二dma指令对应在所述目标服务器中的第二数据到所述模拟nvme磁盘,所述第二数据为所述目标服务器的延迟敏感型应用程序的低延迟数据;

20、所述发送单元,还用于若所述缓存指令数小于或者等于所述预设阈值,则将所述第二dma指令添加到所述第一dma队列;以及,将所述第二dma指令发送到所述fpga控制器的所述第二dma队列,其中,所述第二dma队列用于所述fpga控制器通过所述第一数据处理通道将所述第二dma指令对应在所述目标服务器中的所述第二数据搬移到所述模拟nvme磁盘。

21、第四方面,本技术实施例提供了一种非易失性存储器标准nvme指令的处理装置,应用于目标服务器,所述目标服务器与嵌入式虚拟化系统中的fpga控制器连接,所述嵌入式虚拟化系统包括所述fpga控制器和驱动模块,所述fpga控制器分别与所述目标服务器和所述驱动模块连接,所述嵌入式虚拟化系统用于为所述目标服务器提供模拟nvme磁盘,所述fpga控制器用于接收所述目标服务器发送的nvme请求指令,并将所述nvme请求指令发送到所述驱动模块,所述驱动模块包括第一发送队列、第一dma队列、第一回收队列和所述模拟nvme磁盘,所述fpga控制器包括第二发送队列、第二dma队列、第二回收队列和低延迟dma队列池,所述低延迟dma队列池包括多个低延迟dma队列,所述第二dma队列与第一数据处理通道相对应,所述低延迟dma队列池与低延迟数据处理通道相对应,所述第二发送队列用于缓存所述fpga控制器接收到的所述nvme请求指令,所述第一发送队列用于缓存所述驱动模块接收到的所述nvme请求指令,所述fpga控制器还用于通过所述第一数据处理通道将第一dma指令对应在所述目标服务器中的第一数据搬移到所述模拟nvme磁盘、通过所述低延迟数据处理通道搬移第二dma指令对应在所述目标服务器中的第二数据到所述模拟nvme磁盘,以及通过所述第一数据处理通道搬移所述第二dma指令对应在所述目标服务器中的所述第二数据到所述模拟nvme磁盘,所述装置包括:确定单元、添加单元、接收单元和发送单元,其中,

22、所述确定单元,用于确定目标应用程序是否为延迟敏感型应用程序;

23、所述添加单元,用于若所述目标应用程序为所述延迟敏感型应用程序,在发送所述目标应用程序对应的所述nvme请求指令到所述fpga控制器时,在所述nvme请求指令上添加低延迟标签;

24、所述接收单元,用于接收所述fpga控制器发送的第一完成指令或者第二完成指令;

25、所述发送单元,用于根据所述第一完成指令生成第一回收成功信号或者根据所述第二完成指令生成第二回收成功信号,并将所述第一回收成功信号或者所述第二回收成功信号通过所述fpga控制器发送到所述驱动模块。

26、第五方面,本技术实施例提供了一种电子设备,包括处理器、存储器、通信接口,以及一个或多个程序,所述一个或多个程序被存储在所述存储器中,并且被配置由所述处理器执行,所述程序包括用于执行如本技术实施例第一方面或者第二方面任一方法中所描述的部分或全部步骤。

27、第六方面,本技术实施例提供了一种计算机可读存储介质,其中,上述计算机可读存储介质存储用于电子数据交换的计算机程序,其中,上述计算机程序使得计算机执行如本技术实施例第一方面或者第二方面任一方法中所描述的部分或全部步骤。

28、第七方面,本技术实施例提供了一种计算机程序产品,其中,上述计算机程序产品包括存储了计算机程序的非瞬时性计算机可读存储介质,上述计算机程序可操作来使计算机执行如本技术实施例第一方面任一方法中所描述的部分或全部步骤。该计算机程序产品可以为一个软件安装包。

29、可以看出,本技术实施例中,嵌入式虚拟化系统中的驱动模块可按照第一发送队列中多个nvme请求指令的队列顺序解析每一nvme请求指令,得到nvme指令信息,接着确定nvme指令信息是否包括低延迟标签,若nvme指令信息不包括低延迟标签,则根据nvme指令信息生成第一dma指令,并将第一dma指令添加到第一dma队列,以及将第一dma指令发送到fpga控制器的第二dma队列,其中,第二dma队列用于fpga控制器通过第一数据处理通道将第一dma指令对应在目标服务器中的第一数据搬移到模拟nvme磁盘,第一数据为目标服务器的延迟敏感型应用程序的低延迟数据,而若nvme请求指令包括低延迟标签,则根据nvme指令信息生成第二dma指令,并确定当前第一dma队列中的缓存指令数,并判断缓存指令数是否大于预设阈值,进一步若缓存指令数大于预设阈值,则将第二dma指令发送到fpga控制器中的低延迟dma队列池,其中,低延迟dma队列池用于fpga控制器通过低延迟数据处理通道搬移第二dma指令对应在目标服务器中的第二数据到模拟nvme磁盘;若缓存指令数小于或者等于预设阈值,则将第二dma指令添加到第一dma队列,以及将第二dma指令发送到fpga控制器的第二dma队列,其中,第二dma队列用于fpga控制器通过第一数据处理通道将第二dma指令对应在目标服务器中的第二数据搬移到模拟nvme磁盘,第二数据为目标服务器的非延迟敏感型应用程序的数据。如此,实现了根据nvme指令中的低延迟标签和当前第一dma队列中缓存指令数,决定将第二dma指令发送到低延迟dma队列池还是第二dma队列,低延迟dma队列池和第二dma队列中dma指令采用不同的数据处理通道搬运应用程序的数据,使延迟敏感型应用的低延迟数据能够得到及时处理,搬运到对应的模拟磁盘,有利于提高延迟敏感型应用的运行性能。

- 还没有人留言评论。精彩留言会获得点赞!