基于有效时钟路径的集成电路时序分析方法、系统及介质

本发明属于超大规模集成电路物理设计领域,涉及物理设计中静态时序分析(static timing analysis,sta)技术,具体涉及一种基于有效时钟路径的集成电路时序分析方法、系统及介质。

背景技术:

1、自cmos集成电路技术问世以来,集成电路设计日趋复杂,芯片的集成度与复杂度呈指数上升,其中的时序路径数量与时序分析复杂性也指数增长。与此同时,随着工艺尺寸的持续缩减,先进工艺下的ocv(on-chip variation,片上变化)日益复杂,不仅需要更加先进的ocv模型(如aocv、pocv模型等)来度量工艺的波动,也需要新增更多的工艺波动类型来描述实际的时序。工艺波动类型(process:p)、电压波动类型(voltage:v)、以及温度波动类型(temperature:t)构成的各pvt组合被称为工艺角。先进工艺下由于工艺波动类型的增长使得工艺角度数量不断增长,如平面工艺演进为第一代finfet工艺后,工艺波动类型typical演变为typical_ccworst以及typical_ccbest两种类型,先进工艺下工艺角数量不断增长,使得sta(static timing analysis,静态时序分析)工作量变大并变慢。

2、为了提升先进工艺下时序分析工作效率,需要更多的服务器资源与更先进的时序分析eda软件,这需要庞大的经费支持。事实上,不同的工艺角存在不同程度的相关性,有的具有相同的温度波动类型,有的具有相同的电压波动类型、有的具有相同的工艺波动类型,因而不同工艺角下的路径延迟也存在相关性。kahng等人于2019年在设计、自动化和测试欧洲会议(design automation&test in europe conference&exhibition:date)上发表的论文《unobserved corner prediction:reducing timing analysis effort for fasterdesign convergence in advanced-node design》已指出不同工艺角下的路径延迟呈现出线性相关性。因此,如何利用机器学习技术来发掘不同工艺角之间路径延迟的线性关系,基于部分工艺角下的路径延迟预测其它工艺角下的路径延迟,进而计算出其它工艺角下的时序违反值情况。这种方式的难点在于如何以尽可能少的工艺角运行传统的sta,再基于这些工艺角的时序信息来实现精度可接受的其余工艺角的时序信息,从而大幅度减少sta工作量并达到快速时序分析的目的。

技术实现思路

1、本发明要解决的技术问题:针对现有技术的上述问题,提供一种基于有效时钟路径的集成电路时序分析方法、系统及介质,本发明能够实现目标工艺角集下有效时钟路径延迟与数据路径的预测、目标工艺角集下时序违反值的计算,从而实现快速时序分析,减少先进工艺下日益增长的sta工作量带来的设计周期开销。

2、为了解决上述技术问题,本发明采用的技术方案为:

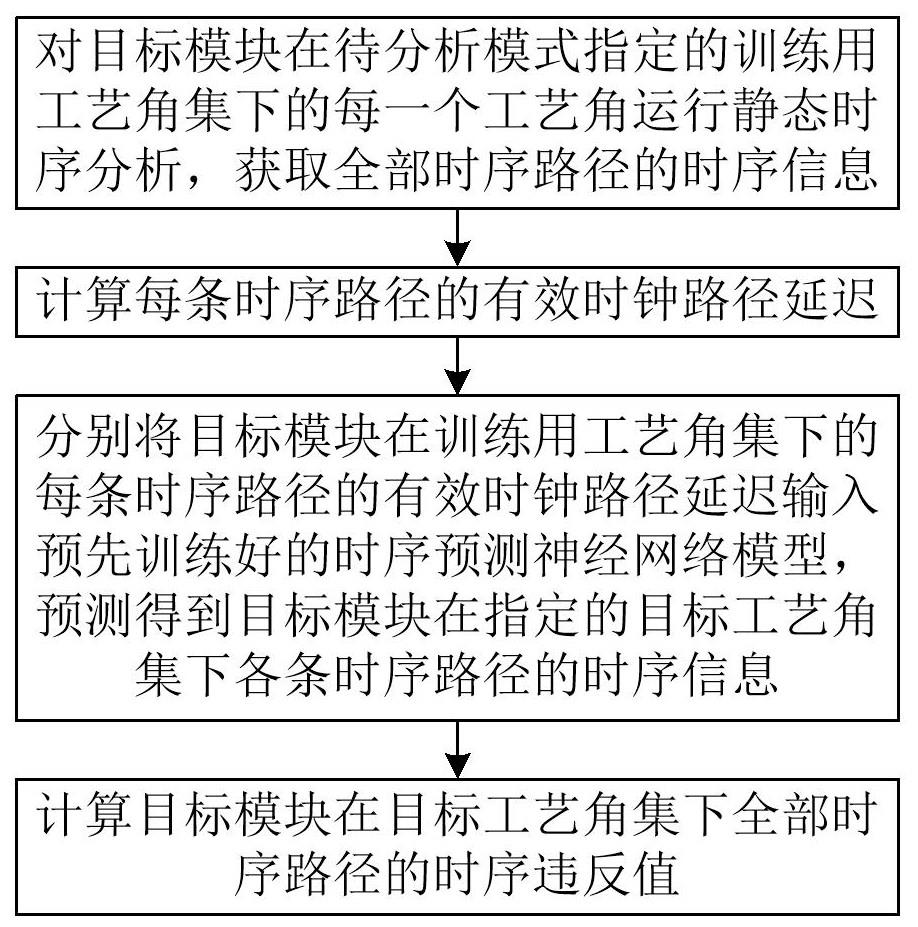

3、一种基于有效时钟路径的集成电路时序分析方法,包括:

4、s101,对目标模块在待分析模式指定的训练用工艺角集下的每一个工艺角运行静态时序分析,获取全部时序路径的时序信息,并计算每条时序路径的有效时钟路径延迟;

5、s102,分别将目标模块在训练用工艺角集下的每条时序路径的有效时钟路径延迟输入预先训练好的时序预测神经网络模型,预测得到目标模块在指定的目标工艺角集下各条时序路径的时序信息,并计算目标模块在目标工艺角集下全部时序路径的时序违反值。

6、可选地,步骤s101中全部时序路径的时序信息包括建立时序路径的时序信息和保持时序路径的时序信息,所述建立时序路径的时序信息包括发射时钟路径的延迟、数据路径的延迟、捕获时钟路径的延迟、时序违反值松弛值、发射时钟路径各级的延迟、时钟汇聚悲观补偿值crpr、crpr级数、捕获寄存器的建立值或恢复值;保持时序路径的时序信息包括发射时钟路径的延迟、数据路径的延迟、捕获时钟路径的延迟、时序违反值松弛值、发射时钟路径各级的延迟、时钟汇聚悲观补偿值crpr、crpr级数、捕获寄存器的保持值或消除值。

7、可选地,步骤s101中获取全部时序路径的时序信息包括:

8、s201,分别对目标模块在待分析模式指定的训练用工艺角集下的num_train_corner个工艺角抽取寄生参数,得到相应的标准寄生提取格式文件;

9、s202,基于标准寄生提取格式文件对num_train_corner个工艺角运行静态时序分析;

10、s203,从静态时序分析结果中选取指定数量num_path_1条时序违反值最差的时序路径,做并集运算得到包含num_path条时序路径的时序路径集合path_colls;

11、s204,对每个工艺角,获取时序路径集合path_colls中每条时序路径的建立时序路径的时序信息和保持时序路径的时序信息,得到每个工艺角下2×num_path条时序路径的时序信息。

12、可选地,步骤s101中计算每条时序路径的有效时钟路径延迟时,每条时序路径的有效时钟路径延迟包括有效发射时钟路径的延迟和有效捕获时钟路径的延迟,其中有效发射时钟路径的延迟由crpr级数之前的发射时钟路径各级的延迟累加而得,有效捕获时钟路径的延迟由有效发射时钟路径的延迟减去时钟汇聚悲观补偿值crpr得到。

13、可选地,步骤s102之前还包括训练时序预测神经网络模型:

14、s301,针对目标模块在待分析模式的包含num_total个工艺角的全部工艺角集,分别计算任意两个工艺角之间的关联度;

15、s302,依据关联度由小至大的顺序,挑选指定数量num_train_corner个工艺角组成训练用工艺角集corners_trained,并从剩余的工艺角中选择工艺角组成目标工艺角集corners_object;选取训练用工艺角集corners_trained下的num_train_path条时序路径的时序信息按类型构建成训练集,将目标工艺角集下对应num_train_path条时序路径的时序信息按类型构建成目标集,并目标集在目标工艺角集下全部时序路径的时序违反值;

16、s303,分别计算训练集中每条时序路径的有效时钟路径延迟,将训练集中每条时序路径的有效时钟路径延迟通过时序预测神经网络模型预测得到训练集的各条时序路径的时序信息,并计算训练集目标工艺角集下全部时序路径的时序违反值;计算训练集目标工艺角集下全部时序路径的时序违反值、目标集在目标工艺角集下全部时序路径的时序违反值之间的统计指标,若统计指标达标则判定时序预测神经网络模型训练完毕,保存训练好的时序预测神经网络模型,以及得到的训练用工艺角集corners_trained和目标工艺角集corners_object,结束并退出;否则,跳转步骤s302。

17、可选地,步骤s301中计算任意两个工艺角之间的关联度是指分别确定两个工艺角下时序违反值松弛值最差的指定数量num_worst条时序路径的时序信息,并根据两者的指定数量num_worst条时序路径的时序信息计算两个工艺角之间的关联度。

18、可选地,所述计算两个工艺角之间的关联度的函数表示为:

19、ratio=common_num_worst / num_worst

20、上式中,ratio为两个工艺角之间的关联度,common_num_worst为两者的指定数量num_worst条时序路径的时序信息中相同的时序路径数量,num_worst为确定两个工艺角下时序违反值松弛值最差的时序路径数量。

21、可选地,步骤s302中依据关联度由小至大的顺序,挑选指定数量num_train_corner个工艺角组成训练用工艺角集corners_trained,并从剩余的工艺角中选择工艺角组成目标工艺角集corners_object包括:若当前为从步骤s301进入,则将工艺角之间的关联度按照自小至大的排序,得到顺序自小到大的关联度序列list_corners,其中含有num_total× (num_total-1) / 2个元素,取第一个元素对应的两个工艺角初始化当前的训练用工艺角集corners_trained,当前的训练用工艺角集corners_trained中元素个数为num_train_corner,去除关联度序列list_corners中的第一个元素并更新关联度序列list_corners,其余工艺角初始化当前的目标工艺角集corners_object;若当前为从步骤s303进入,选取关联度序列list_corners中的第一个元素,选取其中不属于当前的训练用工艺角集corners_trained的任意一个工艺角corner_a加入当前的训练用工艺角集corners_trained,在关联度序列list_corners中去除工艺角corner_a与当前的训练用工艺角集corners_trained其它元素的关联度,并更新关联度序列list_corners,其中当前的训练用工艺角集corners_trained中的元素个数为num_train_corner。

22、此外,本发明还提供一种基于有效时钟路径的集成电路时序分析系统,包括相互连接的微处理器和存储器,所述微处理器被编程或配置以执行所述基于有效时钟路径的集成电路时序分析方法。

23、此外,本发明还提供一种计算机可读存储介质,所述计算机可读存储介质中存储有计算机程序,所述计算机程序用于被微处理器编程或配置以执行所述基于有效时钟路径的集成电路时序分析方法。

24、和现有技术相比,本发明主要具有下述优点:

25、1、本发明基于有效时钟路径的集成电路时序分析方法提出了一套规范化的设计流程,通过有效时钟路径延迟的计算,提升了机器学习方法的时序预测精度,达到了基于少量工艺角时序信息精确预测其它工艺角度时序信息的目标,从而减少了传统的静态时序分析工作量,提升了集成电路物理设计迭代速度,缩短了集成电路物理设计周期。

26、2、本发明方法相对传统时序分析方法而言显著提升了时序分析效率,相对于传统机器学习方法而言不仅提升了时序分析效率也改善了时序预测精度,这对提升集成电路设计迭代效率并缩短集成电路设计周期大有裨益,能够在现行商用电子设计自动化(eda)工具的基础上缓解其耗时耗资源、设计迭代周期长的缺点,能克服现行机器学习方法无法精确预测各工艺角下的时钟汇聚悲观补偿值的不足,提升时序预测精度。

- 还没有人留言评论。精彩留言会获得点赞!