去相关性随机比特流的生成方法及系统

本发明属于新型存储与计算,具体涉及一种去相关性随机比特流的生成方法、系统、电子设备以及存储介质。

背景技术:

1、随着器件尺寸继续向纳米尺度微缩,电路可靠性将成为一个越来越严重的问题。

2、随机计算(stochastic computing,sc)是一种基于由0/1组成的随机比特流序列的新型计算方式,具有电路简单、功耗低、高容错等优点,近年来受到了广泛的关注。与二进制编码不同,随机比特流中每一位比特所占权重相等,任意位上的比特翻转引起的误差相等,因此随机计算具有较高的容错率。同时,由于其独特的数据编码方式,利用简单的门电路就可实现复杂的算数运算,如通过仅通过一个与门就可实现乘法计算。

3、随机计算的精度取决于两个方面:一是由随机比特流长度决定的数值量化精度,即数据在经过由二进制转化为随机比特流后将产生一定的误差;二是受随机比特流之间的相关性影响的计算精度。通过延长随机比特流的长度可以一定程度上降低数据编码过程中的量化误差。为了提高计算精度,需要使用不同的产生相关性强/弱的随机比特流产生电路。

4、随机比特流在通过与门进行乘法计算时要求输入的随机比特流具有相互独立的特性,即输入的随机比特流之间的相关性越弱,计算精度越高。而具有强相关性的输入随机比特流可通过简单的门电路实现一些特定的计算,如通过与门可实现最小值,通过或门可实现最大值,通过异或门可实现绝对值相减计算等。

5、在传统的基于cmos的随机计算电路中需要引入额外的去相关或增强相关性的电路,以产生相互独立的随机比特流或具有相关性的比特流,进一步增加了电路开销与功耗,且针对不同的计算任务,电路难以重构。基于新型存储器件如阻变式随机存取存储器(rram)、阈值开关选择器件等设计的随机比特流产生器虽然可降低功耗和电路开销,但目前尚未有在基于此类新型存储器件中控制产生比特流相关性的技术公开。

6、因此,亟需一种在新型存储器件中实现比特流相关性的控制与产生的技术。

技术实现思路

1、本发明提供一种基于新型阻变存储器件的去相关性随机比特流的生成方法、系统、电子设备以及存储介质,用以克服现有技术中存在的至少一个技术问题。

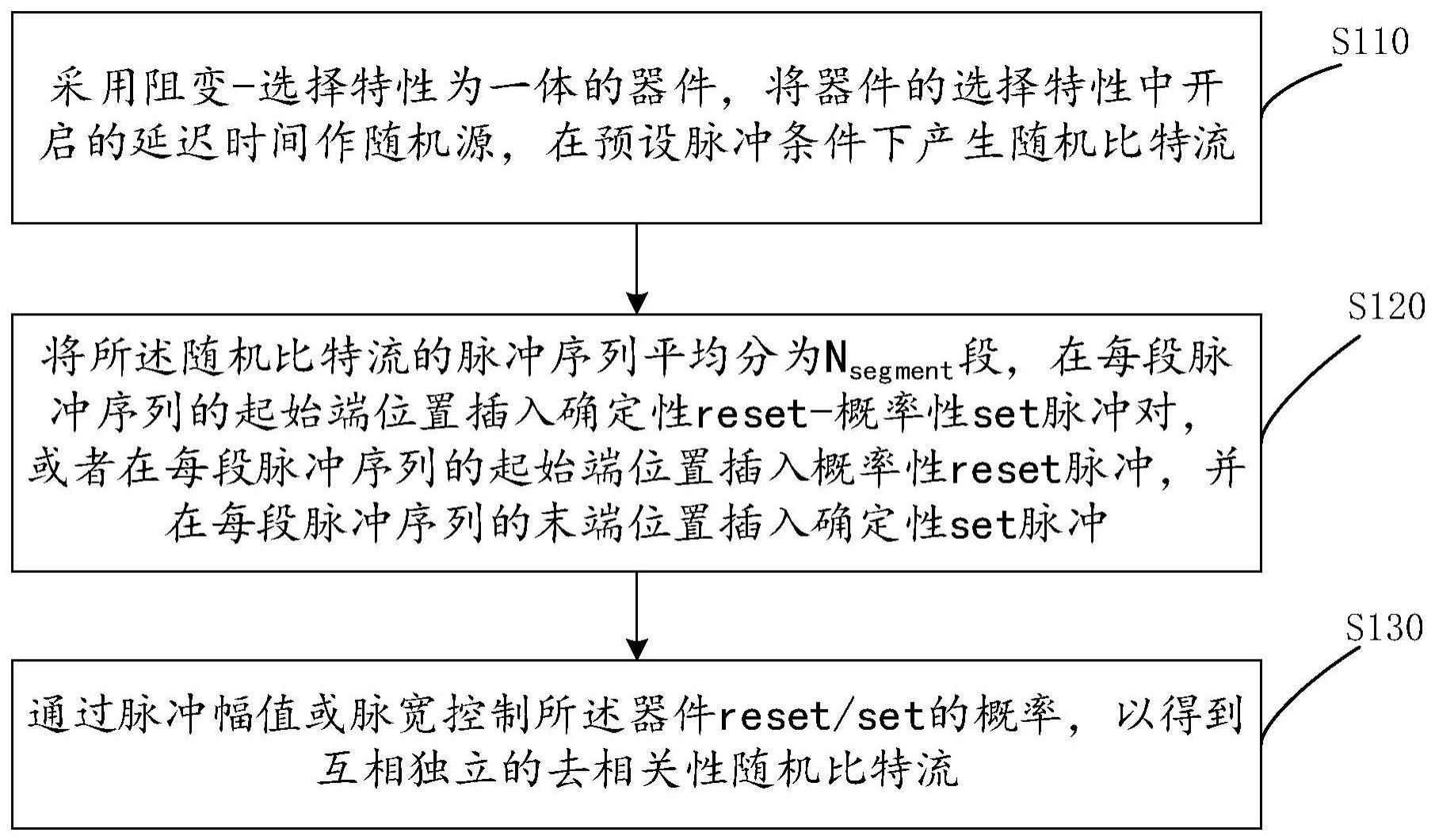

2、为实现上述目的,本发明提供一种去相关性随机比特流的生成方法,包括:

3、采用阻变-选择特性为一体的器件,将所述器件的选择特性中开启的延迟时间作随机源,在预设脉冲条件下产生随机比特流;其中,所述随机比特流中“1”的概率为基准概率;

4、将所述随机比特流的脉冲序列平均分为nsegment段,在每段脉冲序列的起始端位置插入确定性reset-概率性set脉冲对;或在每段脉冲序列的起始端位置插入概率性reset脉冲,并在每段脉冲序列的末端位置插入确定性set脉冲;

5、利用所述器件产生随机比特流,通过脉冲幅值或脉宽控制器件set/reset的概率,以得到互相独立的去相关性随机比特流。

6、为了解决上述问题,本发明还提供一种去相关性随机比特流的生成系统,包括:

7、初始随机比特流产生单元,用于采用阻变-选择特性为一体的器件,将所述器件的选择特性中开启的延迟时间作随机源,在预设脉冲条件下产生随机比特流;其中,所述随机比特流中“1”的概率为基准概率;

8、脉冲序列处理单元,用于将所述随机比特流的脉冲序列平均分为nsegment段,在每段脉冲序列的起始端位置插入确定性reset-概率性set脉冲对;或在每段脉冲序列的起始端位置插入概率性reset脉冲,并在每段脉冲序列的末端位置插入确定性set脉冲;

9、脉冲调控单元,用于利用所述器件产生随机比特流,通过脉冲幅值或脉宽控制器件set/reset的概率,以得到互相独立的去相关性随机比特流。

10、为了解决上述问题,本发明还提供一种电子设备,电子设备包括至少一个处理器;以及,与所述至少一个处理器通信连接的存储器;其中,

11、所述存储器存储有可被所述至少一个处理器执行的指令,所述指令被所述至少一个处理器执行,以使所述至少一个处理器能够执行如前所述的去相关性随机比特流的生成方法中的步骤。

12、为了解决上述问题,本发明还提供一种计算机可读存储介质,计算机可读存储介质中存储有至少一个指令,至少一个指令被电子设备中的处理器执行时实现上述的去相关性随机比特流的生成方法。

13、本发明提供的去相关性随机比特流的生成方法、系统、电子设备以及存储介质,具有以下有益效果:

14、1)本发明与传统的cmos电路中控制比特流相关性的电路相比,可在新型阻变器件中实现去相关性随机比特流的生成,不需要引入额外的相关性控制电路,降低了电路开销与功耗;

15、2)本发明可通过控制器件插入概率性set脉冲或概率性reset脉冲的幅值,实现随机比特流的概率调节;

16、3)本发明可在固定比特流长度下,通过控制分段数,调节去相关性随机比特流的计算精度;

17、4)本发明可以在较短比特流长度下,通过增大分段数,实现较高的计算精度,进一步降低延迟。

技术特征:

1.一种去相关性随机比特流的生成方法,其特征在于,包括:

2.根据权利要求1所述的去相关性随机比特流的生成方法,其特征在于,所述阻变-选择特性一体的器件为采用阻变层与相变层叠加的两端器件结构或三端场效应晶体管结构。

3.根据权利要求2所述的去相关性随机比特流的生成方法,其特征在于,当所述阻变-选择特性一体的器件为采用阻变层与相变层叠加的两端器件结构时,所述阻变层采用具有阻变特性的金属氧化物形成,所述相变层采用具有绝缘体-金属-转变特性的相变材料形成。

4.根据权利要求3所述的去相关性随机比特流的生成方法,其特征在于,

5.根据权利要求1至4中任一项所述的去相关性随机比特流的生成方法,其特征在于,在每段脉冲序列的起始端位置插入确定性reset-概率性set脉冲对,或在每段脉冲序列的起始端位置插入概率性reset脉冲,并在每段脉冲序列的末端位置插入确定性set脉冲之后,

6.根据权利要求1至4中任一项所述的去相关性随机比特流的生成方法,其特征在于,利用所述器件产生随机比特流,包括:

7.根据权利要求6所述的去相关性随机比特流的生成方法,其特征在于,所述预设脉冲条件,为一连串固定幅值和脉宽的脉冲序列;

8.一种去相关性随机比特流的生成系统,其特征在于,包括:

9.一种电子设备,其特征在于,所述电子设备包括至少一个处理器;以及,与所述至少一个处理器通信连接的存储器;其中,

10.一种计算机可读存储介质,存储有至少一个指令,其特征在于,所述至少一个指令被电子设备中的处理器执行时实现如权利要求1至7中任一所述的去相关性随机比特流的生成方法。

技术总结

本发明提供一种去相关性随机比特流的生成方法及系统,属于存储与计算技术领域,本发明利用器件在非易失阻变模式下的概率性set/reset切换,调节脉冲幅值或脉宽,将reset‑set脉冲对设置为概率性切换,将产生基准概率的脉冲平均分为N<subgt;segment</subgt;段,并在每一段脉冲序列的起始端位置插入确定性reset‑概率性set脉冲对,或在每段脉冲序列的起始位置插入概率性reset脉冲,并在每段脉冲序列的末端位置插入确定性set脉冲,由此固定脉冲条件,鉴于器件在非易失阻变模式下可随机reset/set,每一段脉冲序列对应产生的随机比特流将被随机置0,由此可产生互相独立且互不相关的且概率可调的随机比特流。

技术研发人员:蔡一茂,秦雅博,王宗巍,黄如

受保护的技术使用者:北京大学

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!