一种近存计算系统以及近存计算方法、装置、介质及设备与流程

本说明书涉及数据处理,尤其涉及一种近存计算系统以及近存计算方法、装置、介质及设备。

背景技术:

1、三维架构近存计算系统可将常规计算芯片与动态随机存取内存(dynamic randomaccess memory,dram)芯片进行3维堆叠,并使用硅通孔(through silicon via,tsv)或混合键合(hybrid bonding,hb)技术连接上下信号端口,以实现计算芯片与dram芯片的数据交互。相比于传统处理器/存储器结构,近存计算系统可极大缩短计算单元与存储单元之间的距离,减少访存延时,同时使用tsv/hb技术可不通过dram芯片的系统总线提取数据,极大提高访存带宽。近存计算系统可有效缓解内存墙问题,以提高处理器系统性能,具有极大发展潜力。

2、然而目前上述近存计算系统通常采用通用型处理器核,则实现功能时需从处理器核缓存或dram中读取程序。核缓存即静态随机存取存储器(static random-accessmemory,sram)。由于常规设计中sram、dram均为易失性存储器,近存计算系统断电后易失性存储器存储的内容将丢失,故每次上电时均需从外部重新烧入程序与数据,所需时间较长,可造成不必要的性能与能效损耗。

技术实现思路

1、本说明书提供一种近存计算系统以及近存计算方法、装置、介质及设备,以至少部分的解决上述存在的问题。

2、本说明书采用下述技术方案:

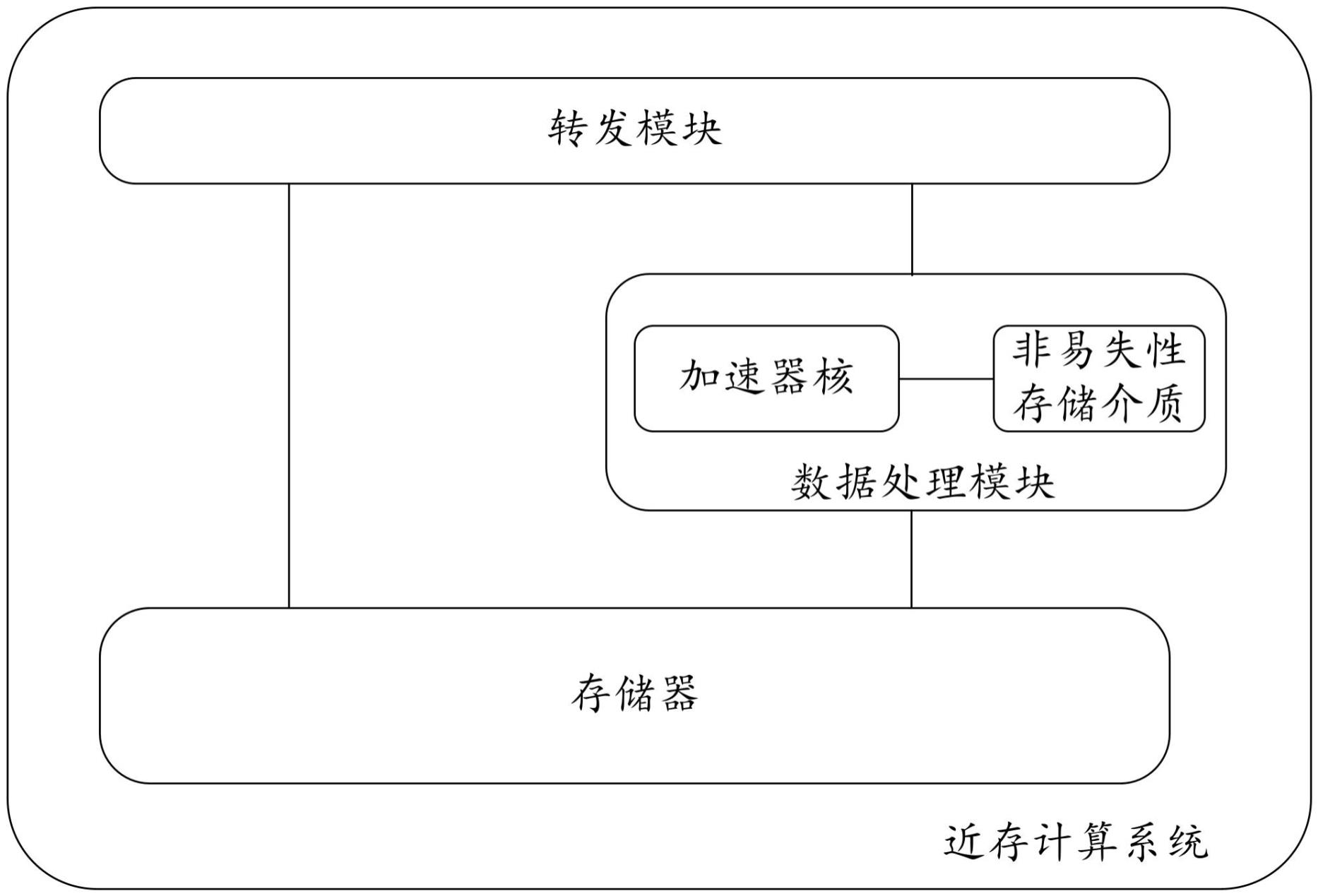

3、本说明书提供了一种近存计算系统,所述系统包括:转发模块、数据处理模块以及存储器;所述数据处理模块包括加速器核以及非易失性存储介质;其中:

4、所述转发模块,用于接收控制设备发送的第一写入指令,将所述第一写入指令携带的待处理数据写入所述存储器;接收所述控制设备在所述待处理数据写入所述存储器后发送的激活指令,并发送至所述加速器核;

5、所述加速器核,用于接收所述激活指令,并从所述非易失性存储介质获取待执行程序,以及从所述存储器获取所述待处理数据,并执行所述待执行程序以对所述待处理数据进行计算,得到计算结果。

6、可选地,所述近存计算系统还包括:存储控制器;

7、所述转发模块,具体用于将所述第一写入指令发送至所述存储控制器;

8、所述存储控制器,用于接收所述第一写入指令,并将所述第一写入指令携带的待处理数据写入所述存储器。

9、可选地,所述转发模块,具体用于将所述待处理数据的写入结果发送至所述控制设备;接收所述控制设备发送的所述加速器核的状态查询指令,并确定所述加速器核的状态查询结果返回所述控制设备;接收所述控制设备在所述状态查询结果为空闲时发送的激活指令,并发送至所述加速器核。

10、可选地,所述近存计算系统还包括:状态寄存器;

11、所述转发模块,具体用于接收所述控制设备发送的所述加速器核的状态查询指令,并转发至所述状态寄存器;接收所述状态寄存器确定的状态查询结果;

12、所述状态寄存器,用于接收所述转发模块发送的状态查询指令,并向所述转发模块返回状态查询结果。

13、可选地,所述数据处理模块为多个。

14、可选地,所述转发模块,具体用于接收所述控制设备在所述待处理数据写入所述存储器后发送的携带加速器核的标识的激活指令,根据所述加速器核的标识从各数据处理模块的加速器核中确定目标加速器核,并将所述激活指令发送至所述目标加速器核。

15、可选地,所述转发模块,还用于接收所述控制设备发送的携带待执行程序以及目标地址区间的第二写入指令,将所述第二写入指令携带的所述待执行程序写入所述存储器中的所述目标地址区间;

16、其中,所述第二写入指令为所述控制设备在确定所述非易失性存储介质中未存储所述待执行程序时发送的。

17、可选地,所述数据处理模块还包括:直接数据访问器;不同加速器核对应所述存储器中的不同地址区间;

18、所述转发模块,还用于接收所述控制设备在所述待执行程序写入所述存储器后发送的携带目标加速器核的标识的程序更新指令,并转发至所述目标加速器核对应的直接数据访问器;

19、所述目标加速器核对应的直接数据访问器,用于接收所述程序更新指令,根据所述目标加速器核的标识,从所述存储器的地址区间中,确定目标地址区间,并从所述存储器的所述目标地址区间获取所述待执行程序,并将所述待执行程序存储至所述目标加速器核对应的非易失性存储介质。

20、本说明书提供了一种近存计算方法,应用于近存计算系统,所述近存计算系统包括非易失性存储介质;所述近存计算方法包括:

21、接收控制设备发送的第一写入指令,存储所述第一写入指令携带的待处理数据;

22、接收所述控制设备发送的激活指令;

23、根据所述激活指令,从所述非易失性存储介质中获取待执行程序;

24、执行所述待执行程序以对所述待处理数据进行计算,得到计算结果。

25、可选地,所述第一写入指令为所述控制设备在确定所述非易失性存储介质中已存储所述待执行程序时发送的;

26、所述方法还包括:

27、接收所述控制设备发送的第二写入指令;

28、存储所述第二写入指令携带的待执行程序,并向所述控制设备发送写入结果;

29、其中,所述第二写入指令为所述控制设备在确定所述非易失性存储介质中未存储所述待执行程序时发送的。

30、本说明书提供了一种近存计算装置,应用于近存计算系统,所述近存计算系统包括非易失性存储介质;所述近存计算装置包括:

31、第一接收模块,用于接收控制设备发送的第一写入指令,存储所述第一写入指令携带的待处理数据;

32、第二接收模块,用于接收所述控制设备发送的激活指令;

33、获取模块,用于根据所述激活指令,从所述非易失性存储介质中获取待执行程序;

34、计算模块,用于执行所述待执行程序以对所述待处理数据进行计算,得到计算结果。

35、本说明书提供了一种计算机可读存储介质,所述存储介质存储有计算机程序,所述计算机程序被处理器执行时实现上述近存计算方法。

36、本说明书提供了一种电子设备,包括存储器、上述任一项所述的近存计算系统及存储在存储器上并可在所述近存计算系统上运行的计算机程序。

37、本说明书采用的上述至少一个技术方案能够达到以下有益效果:近存计算系统包括转发模块、数据处理模块及存储器。数据处理模块包括加速器核及非易失性存储介质。其中:转发模块用于接收控制设备发送的第一写入指令,将第一写入指令携带的待处理数据写入存储器,接收控制设备在待处理数据写入存储器后发送的激活指令,并发送至加速器核。该加速器核用于接收激活指令,并从该非易失性存储介质获取待执行程序,以及从该存储器获取待处理数据,并执行该待执行程序以对该待处理数据进行计算得到计算结果。能够基于非易失性存储介质对程序进行存储,系统断电后无需重新加载程序,可避免不必要的性能与能效损耗,提升数据处理效率。

- 还没有人留言评论。精彩留言会获得点赞!