一种功能安全芯片及其数据通路保护方法与流程

本发明涉及芯片设计领域,具体是涉及一种功能安全芯片及其数据通路保护方法。

背景技术:

1、随着全球汽车行业智能化和车联网的发展,新能源汽车的销量爆发式增长,与此同时也带来车规级芯片的大量需求。不同于消费级芯片与工业级芯片,车规级芯片往往对安全性、可靠性以及稳定性都有更高的要求,因为在汽车领域,与功能安全相关的软件或硬件出现任意的失效,都有可能给人员、设备及环境带来严重的后果。汽车制造厂商面临的一大问题是如何在产品设计阶段规避潜在的安全风险,所以,在汽车芯片的设计阶段,基于功能安全的设计非常重要。

2、目前,车规级芯片中常见的安全机制包括:

3、(1)锁步技术(lockstep)

4、采用该技术的架构采用两套相同的处理器、存储器、比较逻辑、总线/背板接口,通过设定逻辑控制两套总线进行比较之后输出,该设计方式能够有效提高处理器对于指令错误的检测能力。

5、(2)内存保护模块(mpu)

6、该技术对内存进行分区并赋予不同的管理权限,若出现超越当前权限的内存访问,则产生异常信号上报cpu。

7、(3)看门狗(watchdog)

8、该技术用于检测系统基于时间的错误,如死循环,从而可以让系统重启。

9、上述安全机制在数据通路上没有进行保护,或者只是部分通路进行保护,整个芯片的覆盖率较低,错误检测和上报机制不够健全。若采用锁步技术,则需要双份硬件,成本较高。

技术实现思路

1、本发明的第一目的是提供一种数据通路保护覆盖全面的功能安全芯片。

2、本发明的第二目的是提供一种上述功能安全芯片的数据通路保护方法。

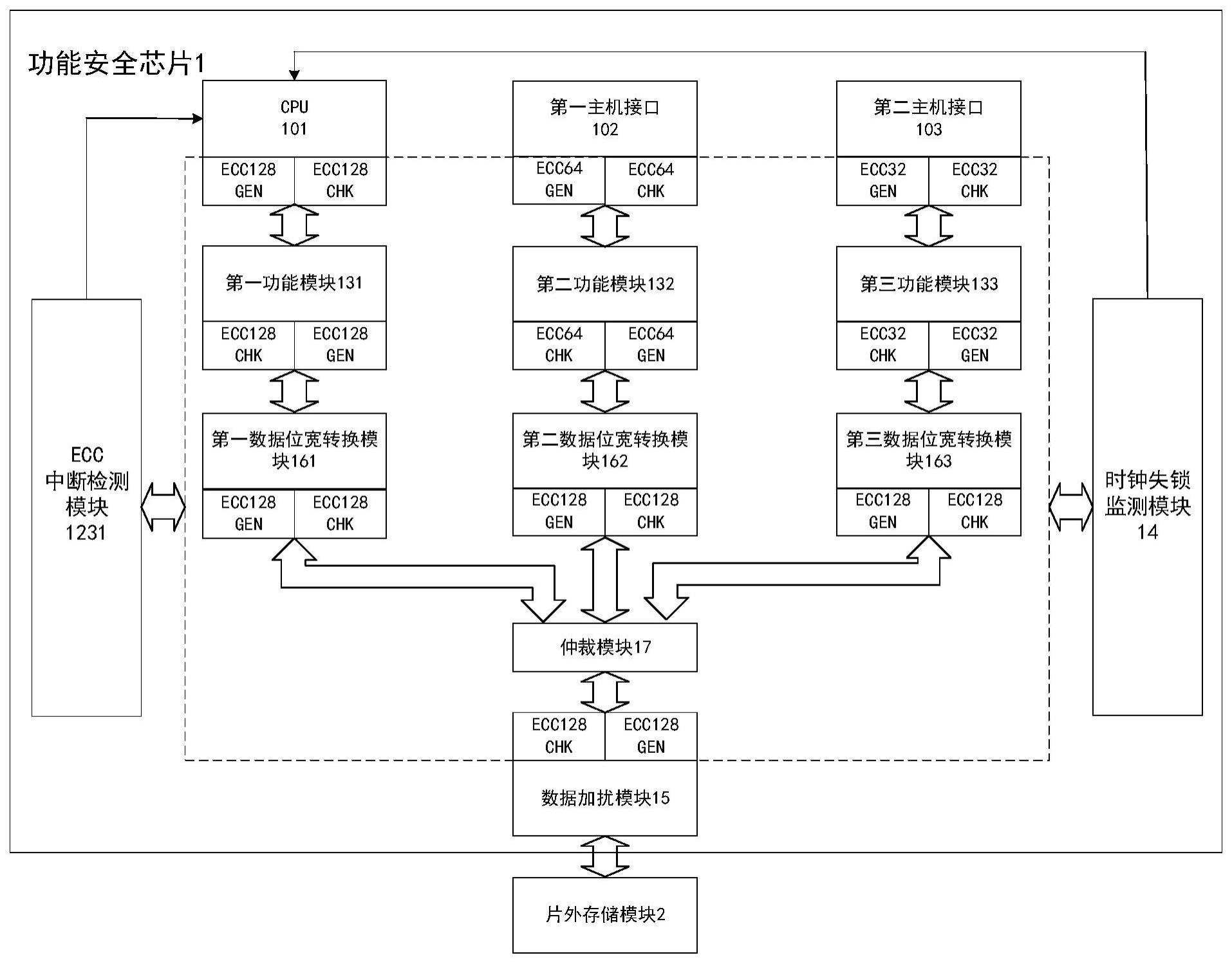

3、为了实现上述的第一目的,本发明提供的一种功能安全芯片,其中,包括:时钟失锁监测模块、数据校验模块、数据加扰模块、处理器模块、功能模块,数据校验模块包括校验码产生模块、校验码检验模块、校验中断检测模块;时钟失锁监测模块连接处理器模块与功能模块,校验码产生模块分别连接处理器模块、功能模块、数据加扰模块,校验码检验模块分别连接处理器模块、功能模块、数据加扰模块,校验码检验模块连接校验中断检测模块,校验中断检测模块连接处理器模块,功能模块连接数据加扰模块,数据加扰模块连接片外存储模块;时钟失锁监测模块用于检测处理器模块与片外存储模块之间的第一数据通路时钟信号是否异常,并在第一数据通路时钟信号异常时输出第一中断信号至处理器模块;校验码产生模块与校验码检验模块用于检测处理器模块与功能模块之间的数据传输以及检测功能模块与数据加扰模块之间的数据传输是否出错,当处理器模块与功能模块之间的数据传输和/或功能模块与数据加扰模块之间的数据传输出错时,校验中断检测模块上传第二中断信号至处理器模块;数据加扰模块用于根据预设规则对数据加扰模块与片外存储模块之间的数据传输进行加解密操作。

4、由上述方案可见,本发明的功能安全芯片通过时钟失锁监测模块保障数据通路时钟的功能安全,通过数据校验模块提高数据传输的安全性,通过数据加扰模块使得功能安全芯片访问片外存储模块时避免明文数据被截获,本发明通过上述的时钟失锁监测模块、数据校验模块以及数据加扰模块相互配合保障数据传输的安全性,覆盖的数据通路范围广,增加的数据失锁检测模块和数据校验模块大部分是组合逻辑电路,占用芯片面积小,消耗资源少。

5、进一步的方案是,功能安全芯片还包括主机接口,主机接口连接功能模块;时钟失锁监测模块还用于检测主机接口与片外存储模块之间的第二数据通路时钟信号是否异常,并在第二数据通路时钟信号异常时输出第三中断信号至处理器模块。

6、由此可见,可以设置不同的主机接口,拓展功能安全芯片访问片外片外存储模块的能力。

7、进一步的方案是,功能安全芯片还包括数据位宽转换模块,数据位宽转换模块连接功能模块、数据加扰模块、数据校验模块、时钟失锁监测模块;数据位宽转换模块用于将功能模块输出的第一数据转换为预设位宽的第二数据,并输出第二数据至数据加扰模块,数据位宽转换模块还用于将从数据加扰模块接收的第三数据转换为预设位宽的第四数据,并输出第四数据至功能模块。

8、由此可见,可以将不同数据位宽的数据重新整合打包成总线下游可以统一识别的格式。

9、进一步的方案是,数据校验模块为ecc数据校验模块,校验码产生模块为ecc校验码产生模块,校验码检验模块为ecc校验码检验模块。

10、由此可见,基于ecc校验的特性,可以在数据校验的过程中对需要校验的数据进行一定程度的修正,具体是1位数据位错误时可以主动纠正,当出现2位错误时,可以上报给校验中断检测模块。

11、进一步的方案是,功能模块与数据加扰模块之间设置有仲裁模块,仲裁模块连接时钟失锁监测模块。

12、进一步的方案是,时钟失锁监测模块包括锁相环、失锁检测模块、中断触发模块,锁相环连接失锁检测模块,失锁检测模块连接中断触发模块,中断触发模块连接处理器模块,失锁检测模块用于接收参考时钟信号与锁相环的鉴频鉴相器输出的信号,中断触发模块根据失锁检测模块的输出信号输出第一中断信号至处理器模块,锁相环用于输出第一数据通路时钟信号。

13、为了实现上述的第二目的,本发明提供的一种实现上述功能安全芯片的数据通路的保护方法,中,包括以下步骤:时钟失锁监测模块检测处理器模块与片外存储模块之间的第一数据通路时钟信号是否异常,并在第一数据通路时钟信号异常时输出第一中断信号至处理器模块;校验码产生模块与校验码检验模块检测处理器模块与功能模块之间的数据传输以及检测功能模块与数据加扰模块之间的数据传输是否出错,当处理器模块与功能模块之间的数据传输和/或功能模块与数据加扰模块之间的数据传输出错时,校验中断检测模块可上传第二中断信号至处理器模块;数据加扰模块根据预设规则对数据加扰模块与片外存储模块之间的数据传输进行加解密操作。

14、由上述方案可见,本发明通过结合时钟失锁监测机制、芯片数据通路的校验机制、访问片外存储模块的数据加扰机制,可以从数据的发送方到数据的接收方进行全局的保护。

15、进一步的方案是,数据加扰模块根据预设规则对数据加扰模块与片外存储模块之间的数据传输进行加解密操作时,根据目标待写地址对数据加扰模块与片外存储模块之间的数据传输进行加密操作,并根据目标待读地址对数据加扰模块与片外存储模块之间的数据传输进行解密操作。

16、由此可见,本发明通过目标待写地址与需要传输的数据进行加扰,通过目标待写地址与需要传输的数据进行解扰,机制简单,避免需要传输的数据被直接读取功能安全芯片的io口截获。

17、进一步的方案是,数据校验模块为ecc数据校验模块,校验码产生模块为ecc校验码产生模块,校验码检验模块为ecc校验码检验模块;ecc校验码产生模块对处理器模块与功能模块之间的传输的数据每8位生成1个ecc校验码。

18、由此可见,可以在后续发生数据位宽转化时无需重新生成ecc校验码,提高功能安全芯片处理速度。

- 还没有人留言评论。精彩留言会获得点赞!