一种多比特全数字存内计算电路、方法及存储器与流程

本发明涉及人工智能,尤其涉及一种多比特全数字存内计算电路、方法及存储器。

背景技术:

1、在人工智能发展迅猛的今天,神经网络中的数据搬运成为了影响其性能的最主要问题。其中存在的存储墙和功耗墙的问题更是使冯诺依曼结构达到了瓶颈。而存内计算结构则能够很好的解决这一问题,并且开始迅猛发展。

2、但是在存内计算结构中也存在或多或少的问题。在存内计算发展的初期,模拟域的存内计算结构占据了主流地位。但是由于模拟信号固有的特征,收到pvt干扰较大,导致其本身就不能用于高精度的网络中。后期的数字域存内计算则不能达到较高的理论吞吐量。

技术实现思路

1、本发明的目的在于提供一种多比特全数字存内计算电路、方法及存储器,提高计算精度以及存储模块的吞吐量。

2、为解决上述技术问题,本发明采用如下技术方案:

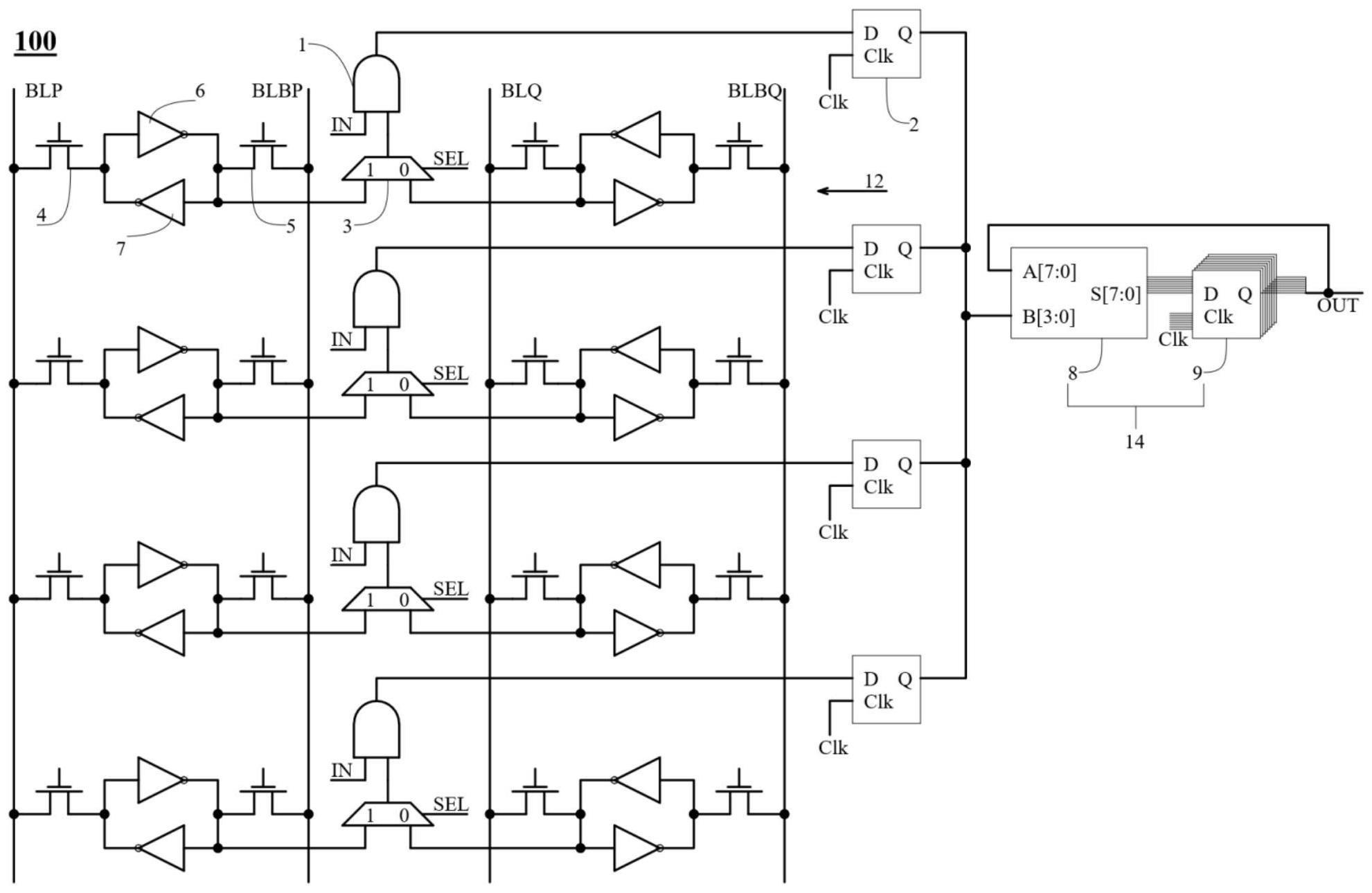

3、本发明实施例的一方面提供了一种多比特全数字存内计算电路,所述存内计算电路包括移位加法模块、至少两个存储模块以及与所述至少两个存储模块数量一致的至少两个乘法电路,所述至少两个乘法电路连接所述至少两个存储模块和所述移位加法模块,所述至少两个存储模块包括第一存储模块,所述至少两个乘法电路包括第一乘法电路,所述第一乘法电路包括:第一与门,所述第一与门的第一输入端用于接收待计算的二进制数字信号的单个电平信号,所述第一与门的第二输入端与所述第一存储模块的输出端连接;第一开关,所述第一开关的输入端与所述第一与门的输出端连接,所述第一开关的输出端与所述移位加法模块的第一输入端连接,所述移位加法模块的输出端输出乘累加结果,并与所述移位加法模块的第二输入端连接。

4、在一些实施例中,所述第一存储模块包括第一存储电路、第二存储电路和选择器,所述选择器的第一输入端连接所述第一存储电路的输出端,所述选择器的第二输入端连接所述第二存储电路的输出端,所述选择器的输出端连接所述第一与门的第二输入端,所述选择器的控制端接收控制信号,以用于控制选择器选择第一存储电路或第二存储电路的权重数据输出。

5、在一些实施例中,所述第一存储电路和第二存储电路结构相同,所述第一存储电路包括第一存储开关、第二存储开关、第一非门和第二非门,所述第一存储开关的一端连接第一非门的输入端和第二非门的输出端,所述第一非门的输出端连接所述第二非门的输入端、第二存储开关的一端和选择器的第一输入端,所述第一存储开关的另一端连接第一位线,所述第二存储开关的另一端连接第二位线。

6、在一些实施例中,所述移位加法模块包括移位加法器,所述移位加法器的输出端连接有八个第二开关,所述第一开关的输出端与所述移位加法器的第一输入端连接,所述八个第二开关的输出端相互连接,所述移位加法器的输出端通过所述八个第二开关输出乘累加结果,所述移位加法器的输出端通过所述八个第二开关连接所述移位加法器的第二输入端。

7、在一些实施例中,所述第一存储开关和第二存储开关均采用nmos管,所述第一开关和所述第二开关均采用触发器。

8、在一些实施例中,所述至少两个存储模块还包括第二存储模块、第三存储模块和第四存储模块,所述第二存储模块、第三存储模块和第四存储模块的结构与所述第一存储模块的结构一致;所述至少两个乘法电路包括第二乘法电路、第三乘法电路和第四乘法电路,所述第二乘法电路、第三乘法电路和第四乘法电路的结构与所述第一乘法电路的结构一致;所述第二乘法电路连接所述第二存储模块和所述移位加法器的第一输入端,所述第三乘法电路连接所述第三存储模块和所述移位加法器的第一输入端,所述第四乘法电路连接所述第四存储模块和所述移位加法器的第一输入端。

9、在一些实施例中,多个所述第一开关和所述第二开关的控制端均接收同一个时钟信号,以用于通过所述时钟信号控制所述第一开关和所述第二开关的开断。

10、本发明实施例的一方面提供了一种多比特全数字存内计算方法,应用于如上所述的存内计算电路,所述存内计算方法包括:第一乘法电路接收第一二进制数字信号的第一个电平信号以及第一存储模块中的第一存储电路输出的权重数据,以计算出第一乘结果的第一个输出值;第二乘法电路接收第一二进制数字信号的第二个电平信号以及第二存储模块中的第一存储电路输出的权重数据,以计算出第一乘结果的第二个输出值;第三乘法电路接收第一二进制数字信号的第三个电平信号以及第三存储模块中的第一存储电路输出的权重数据,以计算出第一乘结果的第三个输出值;第四乘法电路接收第一二进制数字信号的第四个电平信号以及第四存储模块中的第一存储电路输出的权重数据,以计算出第一乘结果的第四个输出值;所述移位加法模块的第一输入端接收第一乘结果的第一个输出值、第二个输出值、第三个输出值和第四个输出值,所述移位加法模块将第一乘结果与初始移位值相加后得到第一乘累加结果;所述移位加法模块将所述第一乘累加结果左移位后得到第一移位值;第一乘法电路接收第二二进制数字信号的第一个电平信号以及第一存储模块中的第二存储电路输出的权重数据,以计算出第二乘结果的第一个输出值;第二乘法电路接收第二二进制数字信号的第二个电平信号以及第二存储模块中的第二存储电路输出的权重数据,以计算出第二乘结果的第二个输出值;第三乘法电路接收第二二进制数字信号的第三个电平信号以及第三存储模块中的第二存储电路输出的权重数据,以计算出第二乘结果的第三个输出值;第四乘法电路接收第二二进制数字信号的第四个电平信号以及第四存储模块中的第二存储电路输出的权重数据,以计算出第二乘结果的第四个输出值;所述移位加法模块的第一输入端接收第二乘结果的第一个输出值、第二个输出值、第三个输出值和第四个输出值,所述移位加法模块将第二乘结果与第一移位值相加后得到第二乘累加结果;所述移位加法模块将所述第二乘累加结果左移位后得到第二移位值,所述第二移位值用于计算第三乘累加结果。

11、在一些实施例中,所述存内计算方法还包括:在所述第一存储模块中的第一存储电路、第二存储模块中的第一存储电路、第三存储模块中的第一存储电路和第四存储模块中的第一存储电路做计算时,则所述第一存储模块中的第二存储电路、第二存储模块中的第二存储电路、第三存储模块中的第二存储电路和第四存储模块中的第二存储电路做权重数据的存储或更新;在所述第一存储模块中的第二存储电路、第二存储模块中的第二存储电路、第三存储模块中的第二存储电路和第四存储模块中的第二存储电路做计算时,则所述第一存储模块中的第一存储电路、第二存储模块中的第一存储电路、第三存储模块中的第一存储电路和第四存储模块中的第一存储电路做权重数据的存储或更新。

12、本发明实施例的一方面提供了一种存储器,所述存储器包括如上所述的存内计算电路。

13、根据本发明实施例的一种多比特全数字存内计算电路、方法及存储器,至少具有如下有益效果:本技术相对于模拟域的存内计算、数字域的存内计算结构输出结果都为准确值,因此在大规模和高精度的领域中的使用具有优势;本技术在计算时依然可以完成存储操作,即权重数据的更新不受影响,同时也提高了存储模块的吞吐率。

14、应当理解的是,以上的一般描述和后文的细节描述仅是示例性的,并不能限制本公开。

- 还没有人留言评论。精彩留言会获得点赞!