时序仿真验证方法、验证装置、电子设备和可读存储介质与流程

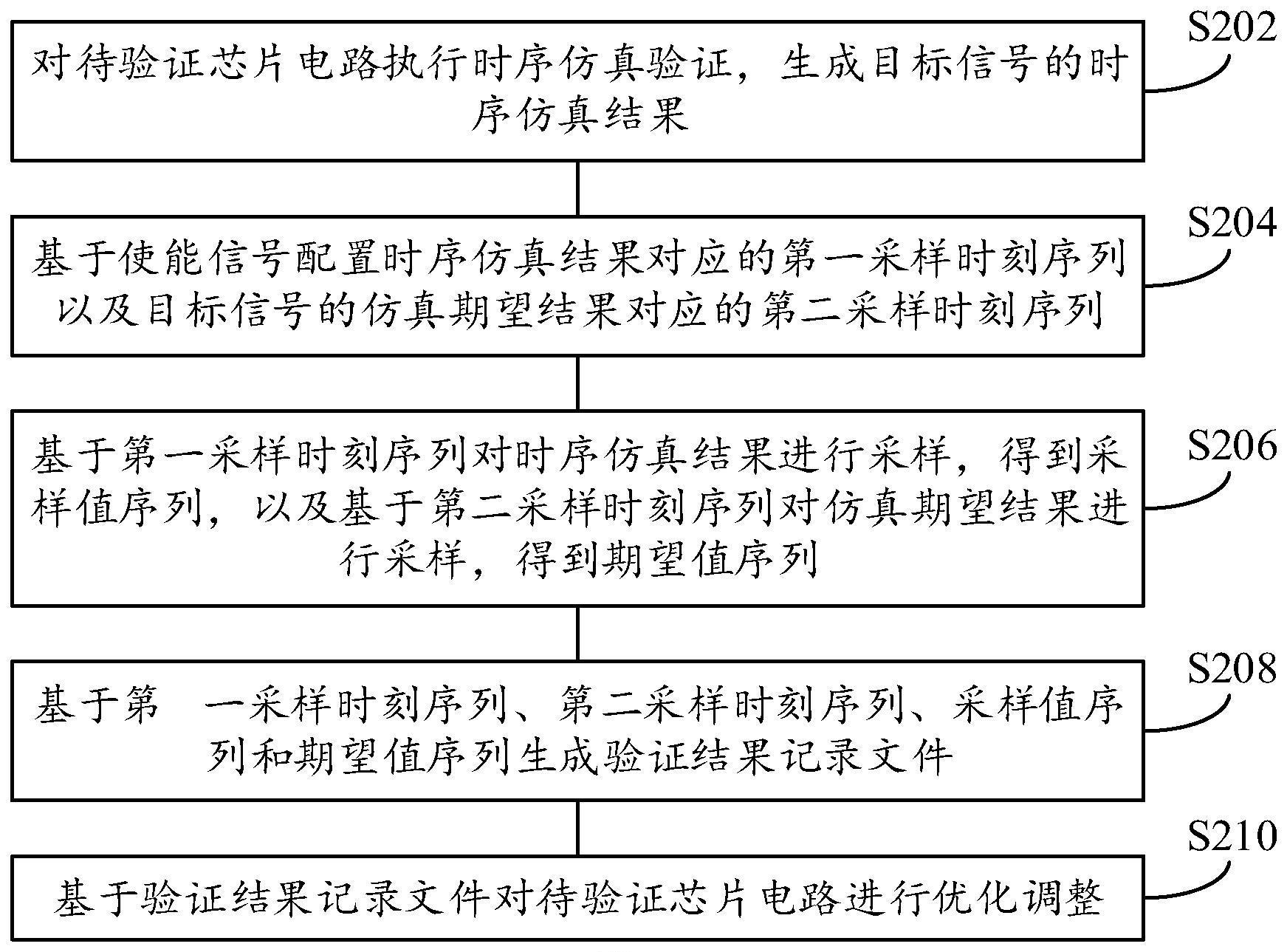

所属的技术人员能够理解,本发明的各个方面可以实现为系统、方法或程序产品。因此,本发明的各个方面可以具体实现为以下形式,即:完全的硬件实施方式、完全的软件实施方式(包括固件、微代码等),或硬件和软件方面结合的实施方式,这里可以统称为“电路”、“模块”或“系统”。下面参照图11来描述根据本发明的这种实施方式的时序仿真验证装置1100。图11所示的时序仿真验证装置1100仅仅是一个示例,不应对本发明实施例的功能和使用范围带来任何限制。时序仿真验证装置1100以硬件模块的形式表现。时序仿真验证装置1100的组件可以包括但不限于:仿真模块1102,用于对待验证芯片电路执行时序仿真验证,生成目标信号的时序仿真结果;配置模块1104,用于基于使能信号配置时序仿真结果对应的第一采样时刻序列以及目标信号的仿真期望结果对应的第二采样时刻序列;采样模块1106,用于基于第一采样时刻序列对时序仿真结果进行采样,得到采样值序列,以及基于第二采样时刻序列对仿真期望结果进行采样,得到期望值序列;验证模块1108,用于基于第一采样时刻序列、第二采样时刻序列、采样值序列和期望值序列生成验证结果记录文件;优化模块1110,用于基于验证结果记录文件对待验证芯片电路进行优化调整。下面参考图12,其示出了适于用来实现本公开实施例的电子设备的计算机系统1200的结构示意图。图12示出的电子设备的计算机系统1200仅是一个示例,不应对本公开实施例的功能和使用范围带来任何限制。如图12所示,计算机系统1200包括中央处理单元(cpu)1201,其可以根据存储在只读存储器(rom)1202中的程序或者从存储部分1208加载到随机访问存储器(ram)1203中的程序而执行各种适当的动作和处理。在ram 1203中,还存储有系统操作所需的各种程序和数据。cpu 1201、rom 1202以及ram 1203通过总线1204彼此相连。输入/输出(i/o)接口1209也连接至总线1204。以下部件连接至i/o接口1205:包括键盘、鼠标等的输入部分1206;包括诸如阴极射线管(crt)、液晶显示器(lcd)等以及扬声器等的输出部分1207;包括硬盘等的存储部分1208;以及包括诸如lan卡、调制解调器等的网络接口卡的通信部分1209。通信部分1209经由诸如因特网的网络执行通信处理。驱动器1210也根据需要连接至i/o接口1205。可拆卸介质1211,诸如磁盘、光盘、磁光盘、半导体存储器等等,根据需要安装在驱动器1210上,以便于从其上读出的计算机程序根据需要被安装入存储部分1208。作为另一方面,本技术还提供了一种计算机可读介质,该计算机可读介质可以是上述实施例中描述的电子设备中所包含的;也可以是单独存在,而未装配入该电子设备中。上述计算机可读介质承载有一个或者多个程序,当上述一个或者多个程序被一个该电子设备执行时,使得该电子设备实现如上述实施例中的仿真验证方法。例如,电子设备可以实现如图2中所示的:步骤s202,对待验证芯片电路执行时序仿真验证,生成目标信号的时序仿真结果;步骤s204,基于使能信号配置时序仿真结果对应的第一采样时刻序列以及目标信号的仿真期望结果对应的第二采样时刻序列;步骤s206,基于第一采样时刻序列对时序仿真结果进行采样,得到采样值序列,以及基于第二采样时刻序列对仿真期望结果进行采样,得到期望值序列;步骤s208,基于第一采样时刻序列、第二采样时刻序列、采样值序列和期望值序列生成验证结果记录文件;步骤s210,基于验证结果记录文件对待验证芯片电路进行优化调整。特别地,根据本公开的实施例,上文参考流程图描述的过程可以被实现为计算机软件程序。例如,本公开的实施例包括一种计算机程序产品,其包括承载在计算机可读介质上的计算机程序,该计算机程序包含用于执行流程图所示的方法的程序代码。在这样的实施例中,该计算机程序可以通过通信部分从网络上被下载和安装,和/或从可拆卸介质被安装。在该计算机程序被中央处理单元(cpu)执行时,执行本技术的系统中限定的上述功能。需要说明的是,本公开所示的计算机可读介质可以是计算机可读信号介质或者计算机可读存储介质或者是上述两者的任意组合。计算机可读存储介质例如可以是——但不限于——电、磁、光、电磁、红外线、或半导体的系统、装置或器件,或者任意以上的组合。计算机可读存储介质的更具体的例子可以包括但不限于:具有一个或多个导线的电连接、便携式计算机磁盘、硬盘、随机访问存储器(ram)、只读存储器(rom)、可擦式可编程只读存储器(eprom或闪存)、光纤、便携式紧凑磁盘只读存储器(cd-rom)、光存储器件、磁存储器件、或者上述的任意合适的组合。在本公开中,计算机可读存储介质可以是任何包含或存储程序的有形介质,该程序可以被指令执行系统、装置或者器件使用或者与其结合使用。而在本公开中,计算机可读的信号介质可以包括在基带中或者作为载波一部分传播的数据信号,其中承载了计算机可读的程序代码。这种传播的数据信号可以采用多种形式,包括但不限于电磁信号、光信号或上述的任意合适的组合。计算机可读的信号介质还可以是计算机可读存储介质以外的任何计算机可读介质,该计算机可读介质可以发送、传播或者传输用于由指令执行系统、装置或者器件使用或者与其结合使用的程序。计算机可读介质上包含的程序代码可以用任何适当的介质传输,包括但不限于:无线、电线、光缆、rf等等,或者上述的任意合适的组合。附图中的流程图和框图,图示了按照本公开各种实施例的系统、方法和计算机程序产品的可能实现的体系架构、功能和操作。在这点上,流程图或框图中的每个方框可以代表一个模块、程序段、或代码的一部分,上述模块、程序段、或代码的一部分包含一个或多个用于实现规定的逻辑功能的可执行指令。也应当注意,在有些作为替换的实现中,方框中所标注的功能也可以以不同于附图中所标注的顺序发生。例如,两个接连地表示的方框实际上可以基本并行地执行,它们有时也可以按相反的顺序执行,这依所涉及的功能而定。也要注意的是,框图或流程图中的每个方框、以及框图或流程图中的方框的组合,可以用执行规定的功能或操作的专用的基于硬件的系统来实现,或者可以用专用硬件与计算机指令的组合来实现。描述于本公开实施例中所涉及到的单元可以通过软件的方式实现,也可以通过硬件的方式来实现,所描述的单元也可以设置在处理器中。其中,这些单元的名称在某种情况下并不构成对该单元本身的限定。应当注意,尽管在上文详细描述中提及了用于动作执行的设备的若干模块或者单元,但是这种划分并非强制性的。实际上,根据本公开的实施方式,上文描述的两个或更多模块或者单元的特征和功能可以在一个模块或者单元中具体化。反之,上文描述的一个模块或者单元的特征和功能可以进一步划分为由多个模块或者单元来具体化。此外,尽管在附图中以特定顺序描述了本公开中方法的各个步骤,但是,这并非要求或者暗示必须按照该特定顺序来执行这些步骤,或是必须执行全部所示的步骤才能实现期望的结果。附加的或备选的,可以省略某些步骤,将多个步骤合并为一个步骤执行,以及/或者将一个步骤分解为多个步骤执行等。通过以上的实施方式的描述,本领域的技术人员易于理解,这里描述的示例实施方式可以通过软件实现,也可以通过软件结合必要的硬件的方式来实现。因此,根据本公开实施方式的技术方案可以以软件产品的形式体现出来,该软件产品可以存储在一个非易失性存储介质(可以是cd-rom,u盘,移动硬盘等)中或网络上,包括若干指令以使得一台计算设备(可以是个人计算机、服务器、移动终端、或者网络设备等)执行根据本公开实施方式的方法。本领域技术人员在考虑说明书及实践这里公开的发明后,将容易想到本公开的其它实施方案。本技术旨在涵盖本公开的任何变型、用途或者适应性变化,这些变型、用途或者适应性变化遵循本公开的一般性原理并包括本公开未公开的本中的公知常识或惯用技术手段。说明书和实施例仅被视为示例性的,本公开的真正范围和精神由所附的权利要求指出。

背景技术:

1、在使用fine-sim等仿真软件进行存储器芯片时序仿真验证过程中,存储器芯片的内存控制器能够将大量的测试用例转化为仿真激励,将激励输入到存储器芯片的待验证电路dut(design under test),并捕捉dut输出的响应,通过将捕捉到的响应电平数据与标准模型golden model输出的预期电平数据进行比较,从而能够基于比较结果得到仿真验证结果,但是由于仿真激励会引入外部时钟信号,因此数据能检测到的范围也会受到外部时钟信号的限制,导致影响验证效果。

2、需要说明的是,在上述背景技术部分公开的信息仅用于加强对本公开的背景的理解,因此可以包括不构成对本领域普通技术人员已知的现有技术的信息。

技术实现思路

1、本公开的目的在于提供一种时序仿真验证方法、验证装置、电子设备和可读存储介质,至少在一定程度上克服由于相关技术中仿真验证受到外部时钟信号限制而影响时序仿真验证效果的问题。

2、本公开的其他特性和优点将通过下面的详细描述变得显然,或部分地通过本公开的实践而习得。

3、根据本公开的一个方面,提供一种时序仿真验证方法,包括:对待验证芯片电路执行时序仿真验证,生成目标信号的时序仿真结果;基于使能信号配置所述时序仿真结果对应的第一采样时刻序列以及所述目标信号的仿真期望结果对应的第二采样时刻序列;基于所述第一采样时刻序列对所述时序仿真结果进行采样,得到采样值序列,以及基于所述第二采样时刻序列对所述仿真期望结果进行采样,得到期望值序列;基于所述第一采样时刻序列、所述第二采样时刻序列、所述采样值序列和所述期望值序列生成验证结果记录文件;基于所述验证结果记录文件对所述待验证芯片电路进行优化调整。

4、在本公开的一个实施例中,所述基于所述第一采样时刻序列对所述时序仿真结果进行采样,得到采样值序列,以及基于所述第二采样时刻序列对所述仿真期望结果进行采样,得到期望值序列,包括:基于所述第一采样时刻序列对所述时序仿真结果进行采样,得到仿真采样结果;基于所述第二采样时刻序列对所述仿真期望结果进行采样,得到所述期望值序列;基于待验证芯片的仿真参数确定高低电平分界值;基于所述高低电平分界值确定与所述仿真采样结果对应的所述采样值序列。

5、在本公开的一个实施例中,所述目标信号包括待验证芯片的数据选通引脚输出的数据选通信号dqs,所述第一采样时刻序列包括第一dqs采样时刻序列,所述第二采样时刻序列包括第二dqs采样时刻序列,所述基于使能信号配置所述时序仿真结果对应的第一采样时刻序列以及所述目标信号的仿真期望结果对应的第二采样时刻序列,包括:基于所述使能信号的上升沿确定采样触发点;基于所述高低电平分界值确定所述时序仿真结果中与所述采样触发点最接近的第一个下降沿,将所述第一个下降沿确定为第一采样参考点,以及基于所述采样触发点确定第二采样参考点;基于所述第一采样参考点、所述第二采样参考点和所述待验证芯片的工作频率配置所述第一dqs采样时刻序列和所述第二dqs采样时刻序列。

6、在本公开的一个实施例中,所述基于所述第一采样参考点、所述第二采样参考点和所述待验证芯片的工作频率配置所述第一dqs采样时刻序列和所述第二dqs采样时刻序列,包括:基于所述第一采样参考点和所述工作频率确定对所述时序仿真结果执行采样操作的第一采样起点和采样周期;基于所述采样触发点和所述工作频率确定对所述仿真期望结果执行采样操作的第二采样起点和所述采样周期;其中,所述采样周期为所述第一dqs采样时刻序列中多个采样时刻之间的间隔以及所述第二dqs采样时刻序列中多个采样时刻之间的间隔,所述第一采样起点为所述第一dqs采样时刻序列中的第一个第一采样时刻,所述第二采样起点为所述第二dqs采样时刻序列中的第一个第二采样时刻。

7、在本公开的一个实施例中,所述目标信号还包括所述待验证芯片的数据输出端口输出的读出数据信号dq,所述第一采样时刻序列还包括第一dq采样时刻序列,所述第二采样时刻序列还包括第二dq采样时刻序列,所述基于使能信号配置所述时序仿真结果对应的第一采样时刻序列以及所述目标信号的仿真期望结果对应的第二采样时刻序列,还包括:基于所述第一dqs采样时刻序列配置所述第一dq采样时刻序列;基于所述第二dqs采样时刻序列配置所述第二dq采样时刻序列。

8、在本公开的一个实施例中,所述基于所述第一采样时刻序列、所述第二采样时刻序列、所述采样值序列和所述期望值序列生成验证结果记录文件,包括:基于所述第一采样时刻序列和所述第二采样时刻序列确定所述待验证芯片电路的时序偏移量;检测所述时序偏移量是否处于时序延迟范围内;检测到所述时序偏移量处于所述时序延迟范围内,获取所述采样值序列和所述期望值序列的比较结果;基于所述比较结果生成验证结果记录文件,其中,所述时序延迟范围基于所述待验证芯片电路的标准规范文件确定。

9、在本公开的一个实施例中,所述获取所述采样值序列和所述期望值序列的比较结果,包括:确定所述第一采样时刻序列中的每个第一采样时刻和所述第二采样时刻序列中对应的第二采样时刻,所述第一采样时刻和所述第二采样时刻具有相同的采样序列号;比较每个所述第一采样时刻下的采样值和对应的所述第二采样时刻下的期望值是否一致;若比较结果一致,在所述验证结果记录文件中记录验证通过;若比较结果不一致,在所述验证结果记录文件中记录验证失败。

10、根据本公开的另一个方面,提供一种时序仿真验证装置,包括:仿真模块,用于对待验证芯片电路执行时序仿真验证,生成目标信号的时序仿真结果;配置模块,用于基于使能信号配置所述时序仿真结果对应的第一采样时刻序列以及所述目标信号的仿真期望结果对应的第二采样时刻序列;采样模块,用于基于所述第一采样时刻序列对所述时序仿真结果进行采样,得到采样值序列,以及基于所述第二采样时刻序列对所述仿真期望结果进行采样,得到期望值序列;验证模块,用于基于所述第一采样时刻序列、所述第二采样时刻序列、所述采样值序列和所述期望值序列生成验证结果记录文件;优化模块,用于基于所述验证结果记录文件对所述待验证芯片电路进行优化调整。

11、根据本公开的再一个方面,提供一种电子设备,包括:处理器;以及存储器,用于存储处理器的可执行指令;其中,处理器配置为经由执行可执行指令来执行上述任意一项所述的时序仿真验证方法。

12、根据本公开的又一个方面,提供一种计算机可读存储介质,其上存储有计算机程序,计算机程序被处理器执行时实现上述任意一项所述的时序仿真验证方法。

13、本公开的实施例所提供的时序仿真验证方案,通过跟踪待验证芯片的读使能信号,以基于读使能信号触发配置出第一采样时刻序列和第二采样时刻序列,以基于第一采样时刻序列和第二采样时刻序列分别对目标信号的时序仿真结果和仿真期望结果进行采样操作,得到采样值序列和期望值序列,进而基于采样时刻序列和采样值序列生成验证结果记录文件,从而基于验证结果记录文件对待验证芯片电路进行优化调整,该验证方案由于不需要依赖外部时钟信号,能够保证目标信号的检测范围的最大化,从而有利于提升时序验证操作的可靠性和验证精度。进一步地,配置出的采样时刻序列能够降低采集到错误干扰点的概率,即防止在时序验证过程中检测到其它电路问题,从而保证时序仿真验证的验证精度。

14、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本公开。

- 还没有人留言评论。精彩留言会获得点赞!