主板及计算设备的制作方法

本技术涉及计算,尤其涉及一种主板及计算设备。

背景技术:

1、服务器通常会支持很多硬盘,不同的服务器的硬盘管理方式也有差异。例如,一些服务器支持raid(redundant array of independent disks,独立硬盘冗余阵列)管理方式,在该管理方式下,cpu(central processing unit,中央处理器)与raid芯片电连接,而raid芯片电连接于硬盘。此时,cpu可以将pcie(peripheral component interconnectexpress,外围互联总线)协议信号发送至raid芯片,而raid芯片可以将pcie协议信号转化为sas(serial attached scsi,串行连接scsi)协议信号,并将sas协议信号发送至硬盘,以此对硬盘进行管理。又例如,一些服务器支持直通管理方式,在该管理方式下,南桥芯片与硬盘电连接,南桥芯片可以输出sata(serial advanced technology attachment,串行ata)协议信号,sata协议信号可以传输至硬盘,以此对硬盘进行管理。为了使得服务器可以支持上述两种硬盘管理方式,通常会在服务器中设置两种信号传输链路,服务器虽然可以支持两种硬盘管理方式,但是在服务器产品中会采用上述两种硬盘管理方式中的一种对硬盘进行管理。上述两种硬盘管理方式所对应的信号传输链路完全不同,导致服务器的成本较高。

技术实现思路

1、本技术的实施例提供一种主板及计算设备,能够降低计算设备的成本。

2、一方面,本技术的实施例提供一种主板。该主板包括:板体、南桥芯片、中央处理器和第一转接连接器。南桥芯片设置于板体上;中央处理器设置于板体上;第一转接连接器设置于板体上,第一转接连接器包括第一引脚组和第二引脚组;其中,第一引脚组连接于南桥芯片,且第二引脚组用于与存储组件耦接。当第一转接连接器连接于直通板卡时,第一引脚组和第二引脚组通过直通板卡耦接,南桥芯片用于输出sata协议信号,sata协议信号能够依次通过第一引脚组、直通板卡和第二引脚组传输至存储组件。当第一转接连接器连接于独立硬盘冗余阵列板卡时,中央处理器与独立硬盘冗余阵列板卡耦接,独立硬盘冗余阵列板卡与第二引脚组耦接,其中,中央处理器用于将pcie协议信号发送至独立硬盘冗余阵列板卡,独立硬盘冗余阵列板卡能够将pcie协议信号转化为sas协议信号,sas协议信号能够通过第二引脚组传输至存储组件。

3、其中,在第一转接连接器连接于直通板卡的情况下,南桥芯片所输出的sata协议信号,能够依次通过第一引脚组、直通板卡和第二引脚组传输至存储组件,此时南桥芯片可以对存储组件进行管理。在第一转接连接器连接于独立硬盘冗余阵列板卡的情况下,中央处理器所输出的pcie协议信号可以发送至独立硬盘冗余阵列板卡,独立硬盘冗余阵列板卡能够将pcie协议信号转化为sas协议信号,sas协议信号能够通过第二引脚组传输至存储组件,此时,中央处理器可与对存储组件进行管理。因此,在第一转接连接器连接于直通板卡或者独立硬盘冗余阵列板卡的两种情况下,主板都可以实现对存储组件的管理,进而可以使得主板具有较高的兼容性。因此,可以避免因改变目标板卡而导致需要重新设计主板,以此可以节约成本。此外,在第一转接连接器连接于直通板卡或者独立硬盘冗余阵列板卡的两种情况下,直通板卡或者独立硬盘冗余阵列板卡所接收的信号均可以传输至第二引脚组,并通过第二引脚组传输至存储组件。因此,第二引脚组、以及第二引脚组与存储组件之间的连接链路可以在上述两种情况下复用,从而可以降低主板的成本。

4、在一些实现方案中,主板还包括:第二转接连接器,其设置于板体上,第二转接连接器连接于中央处理器。当第一转接连接器连接于独立硬盘冗余阵列板卡时,独立硬盘冗余阵列板卡还连接于第二转接连接器,中央处理器所输出的pcie协议信号能够通过第二转接连接器传输至独立硬盘冗余阵列板卡。

5、其中,第二转接连接器电连接于中央处理器,而第二转接连接器又可以电连接于独立硬盘冗余阵列板卡,以此,中央处理器所生成的pcie协议信号可以通过第二转接连接器传输至独立硬盘冗余阵列板卡。进一步地,独立硬盘冗余阵列板卡能够将pcie协议信号转化为sas协议信号,sas协议信号能够通过第二引脚组传输至存储组件,从而实现中央处理器与对存储组件的管理。

6、在一些实现方案中,第一转接连接器还包括第一在位引脚,第二转接连接器还包括第二在位引脚。主板还包括:设置于板体上的电压电路和可编程逻辑器件。电压电路连接于第一在位引脚和第二在位引脚,在第一在位引脚未连接于目标板卡的情况下,电压电路能够使第一在位引脚的电压在第二电压阈值范围内;在第一在位引脚连接于目标板卡的情况下,电压电路和目标板卡共同使第一在位引脚的电压在第一电压阈值范围内;在第二在位引脚未连接于目标板卡的情况下,电压电路能够使第二在位引脚的电压在第二电压阈值范围内;在第二在位引脚连接于目标板卡的情况下,电压电路和目标板卡共同使第二在位引脚的电压在第一电压阈值范围内;其中,目标板卡为直通板卡和独立硬盘冗余阵列板卡中的一个。可编程逻辑器件连接于第一在位引脚和第二在位引脚;可编程逻辑器件用于:检测第一在位引脚的电压和第二在位引脚的电压;并且,在第一在位引脚的电压和第二在位引脚的电压均在第一电压阈值范围内的情况下,确定第一转接连接器所连接的板卡为独立硬盘冗余阵列板卡;在第一在位引脚的电压在第一电压阈值范围内,第二在位引脚的电压在第二电压阈值范围内的情况下,确定第一转接连接器所连接的板卡为直通板卡。

7、如此设置,通过在第一转接连接器上设置第一在位引脚且第二转接连接器上设置第二在位引脚,使得当目标板卡(即直通板卡或独立硬盘冗余阵列板卡)连接于第一转接连接器时,可编程逻辑器件可以自动检测目标板卡的种类。

8、在一些实现方案中,主板还包括:基本输入输出单元,其设置于板体上;基本输入输出单元连接于可编程逻辑器件和南桥芯片;基本输入输出单元用于:在可编程逻辑器件确定第一转接连接器所连接的目标板卡为独立硬盘冗余阵列板卡的情况下,控制南桥芯片停止输出sata协议信号。

9、如此设置,在第一转接连接器所连接的目标板卡为独立硬盘冗余阵列板卡的情况下,南桥芯片停止输出sata协议信号,因此第二引脚组不会接收到南桥芯片所输出的sata协议信号,可以避免独立硬盘冗余阵列板卡所输出的sas协议信号和南桥芯片所输出的sata协议信号在第二引脚组上发生冲突,对其他引脚组上的信号产生干扰。

10、在一些实现方案中,第二转接连接器包括第三引脚组和第四引脚组,第三引脚组连接于中央处理器,第四引脚组用于与独立硬盘冗余阵列板卡耦接。主板还包括设置于板体上的第一现场可编程门阵列芯片,第一现场可编程门阵列芯片连接于第四引脚组,且能够与存储组件电连接。当第一转接连接器连接于独立硬盘冗余阵列板卡时,第四引脚组用于接收独立硬盘冗余阵列板卡输出的第一低速信号,并将第一低速信号传输至第一现场可编程门阵列芯片。第一现场可编程门阵列芯片用于将第一低速信号传输至存储组件。

11、其中,通过在第二转接连接器上设置第四引脚组,以及在板体上设置第一现场可编程门阵列芯片,而第一现场可编程门阵列芯片可以电连接于存储组件,而第四引脚组可以电连接于第一现场可编程门阵列芯片,进而独立硬盘冗余阵列芯片所输出的第一低速信号可以通过第四引脚组传输至第一现场可编程门阵列芯片,而后第一现场可编程门阵列芯片可以将第一低速信号转发至存储组件,从而独立硬盘冗余阵列芯片可以与存储组件之间进行低速信号的交互。

12、在一些实现方案中,主板还包括第二现场可编程门阵列芯片,其设置于板体上,且连接于南桥芯片和存储组件。当第一转接连接器连接于直通板卡时,南桥芯片还用于:输出第二低速信号。第二现场可编程门阵列芯片用于接收第二低速信号,并将第二低速信号传输至存储组件。

13、其中,通过设置第二现场可编程门阵列芯片,且第二现场可编程门阵列芯片可以与南桥芯片和存储组件电连接,进而南桥芯片可以将第二低速信号传输至第二现场可编程门阵列芯片,第二现场可编程门阵列芯片又可以将第二低速信号传输至存储组件上,以此南桥芯片与存储组件之间还可以进行低速信号的交互。

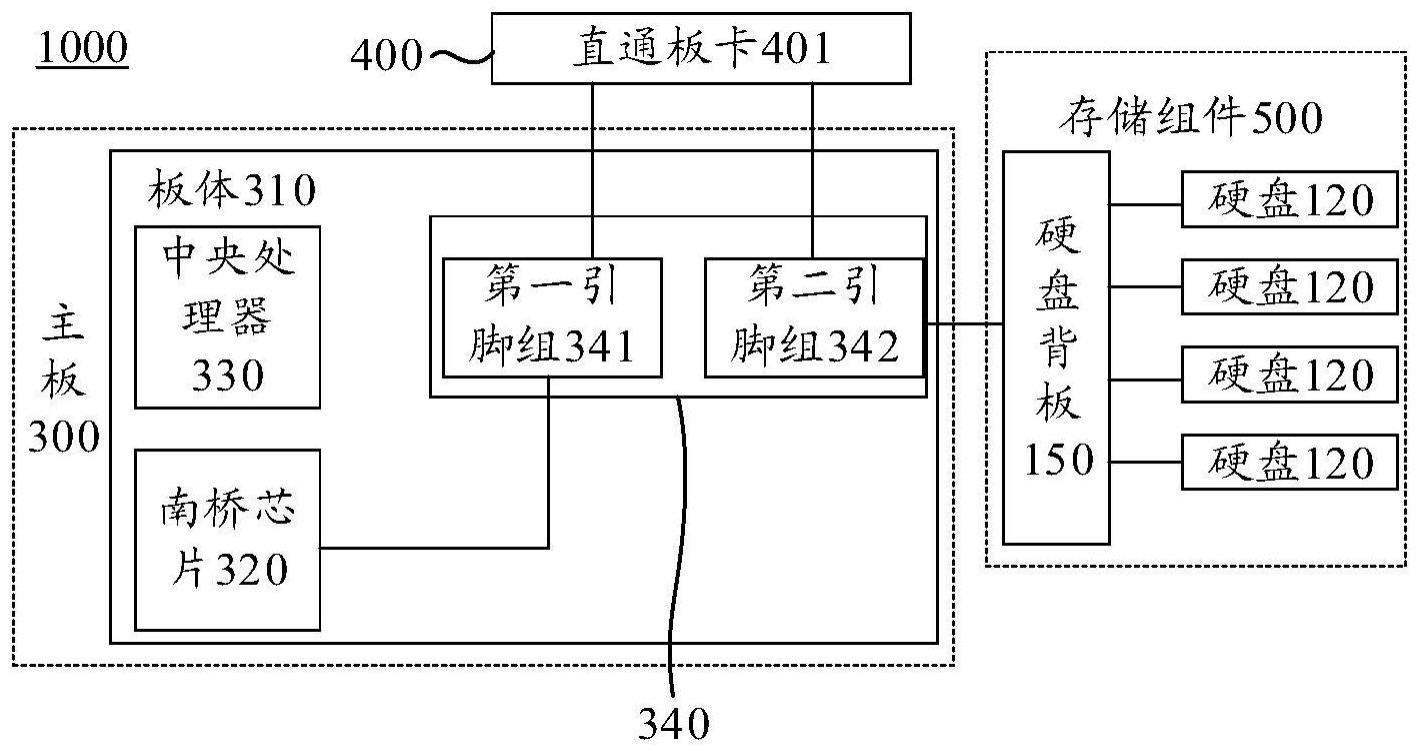

14、另一方面,本技术的实施例提供了一种计算设备,该计算设备包括:存储组件、目标板卡和以上一些实现方案所提供的主板。目标板卡为直通板卡或独立硬盘冗余阵列板卡。主板的第一转接连接器连接于目标板卡。其中,当第一转接连接器所连接的目标板卡为直通板卡时,第一转接连接器的第一引脚组和第二引脚组通过直通板卡耦接,主板的南桥芯片用于输出sata协议信号,sata协议信号能够依次通过第一引脚组、直通板卡和第二引脚组传输至存储组件。当第一转接连接器所连接的目标板卡为独立硬盘冗余阵列板卡时,主板的中央处理器与独立硬盘冗余阵列板卡耦接,独立硬盘冗余阵列板卡与第二引脚组耦接,其中,中央处理器用于将pcie协议信号发送至独立硬盘冗余阵列板卡,独立硬盘冗余阵列板卡能够将pcie协议信号转化为sas协议信号,sas协议信号能够通过第二引脚组传输至存储组件。

15、其中,在目标板卡为直通板卡的情况下,或者目标板卡为独立硬盘冗余阵列板卡的情况下,主板都可以实现对存储组件的管理,进而可以使得主板具有较高的兼容性。因此,可以避免因改变目标板卡而需要导致重新设计主板,以此可以节约成本。此外,在目标板卡为直通板卡的情况下,或者目标板卡为独立硬盘冗余阵列板卡的情况下,目标板卡所接收的信号均可以传输至第二引脚组,并通过第二引脚组传输至存储组件。因此,第二引脚组、以及第二引脚组与存储组件之间的连接链路可以在上述两种情况下复用,从而可以降低主板的成本。

16、在一些实现方案中,主板还包括第二转接连接器,第二转接连接器设置于主板的板体上,且连接于中央处理器。当第一转接连接器所连接的目标板卡为独立硬盘冗余阵列板卡时,独立硬盘冗余阵列板卡还连接于第二转接连接器,中央处理器所输出的pcie协议信号通过第二转接连接器发送至独立硬盘冗余阵列板卡。

17、其中,第二转接连接器电连接于中央处理器,而第二转接连接器又可以电连接于独立硬盘冗余阵列板卡,以此,中央处理器所生成的pcie协议信号可以通过第二转接连接器传输至独立硬盘冗余阵列板卡。进一步地,独立硬盘冗余阵列板卡能够将pcie协议信号转化为sas协议信号,sas协议信号能够通过第二引脚组传输至存储组件,从而实现中央处理器与对存储组件的管理。

18、在一些实现方案中,目标板卡包括转接电路板、第一输入引脚组和第一输出引脚组,第一输入引脚组和第一输出引脚组耦接,且均设置于转接电路板上,第一输出引脚组连接于第二引脚组。其中,当第一转接连接器连接于直通板卡时,第一输入引脚组连接于第一引脚组。当第一转接连接器连接于独立硬盘冗余阵列板卡时,第一输入引脚组连接于第二转接连接器。

19、其中,当第一转接连接器连接于独立硬盘冗余阵列板卡时,第一输入引脚组连接于第二转接连接器。而第二转接连接器又电连接于中央处理器,第一输入引脚组又电连接于第一引脚组,从而中央处理器所输出的pcie协议信号可以依次经过第二转接连接器和第一输入引脚组传输至独立硬盘冗余阵列芯片。独立硬盘冗余阵列芯片可以对pcie协议信号进行处理,将pcie协议信号转化为sas协议信号。当中央处理器通过独立硬盘冗余阵列芯片对硬盘进行管理时,独立硬盘冗余阵列芯片可以使得多台硬盘可并行工作,提高了数据传输率,并且能够提高数据的安全性。

20、当第一转接连接器连接于直通板卡时,第一输入引脚组连接于第一引脚组,南桥芯片所输出的sata协议信号可以依次通过第一引脚组、第一输入引脚组、第一输出引脚组和第二引脚组传输至存储组件。此时,南桥芯片可以对存储组件上的多个硬盘进行管理,计算设备的成本较低。

21、在一些实现方案中,当目标板卡为独立硬盘冗余阵列板卡时,目标板卡还包括:设置于转接电路板上的第二输出引脚组和独立硬盘冗余阵列芯片,第二输出引脚组电连接于独立硬盘冗余阵列芯片和第一引脚组。当独立硬盘冗余阵列芯片将pcie协议信号转化为sas协议信号后,sas协议信号传输至第一输出引脚组和第二输出引脚组。

22、其中,第二输出引脚组所接收的sas协议信号无需通过第二引脚组传输至存储组件,因此,可以使得独立硬盘冗余阵列芯片所输出的sas协议信号有多余,而多余的sas协议信号则可以通过第二引脚组传输至第一引脚组,此时,第一引脚组既能够接收第二输出引脚所传输过来的多余的sas协议信号,还可以接收南桥芯片传输过来的sata协议信号,从而第一引脚组中的至少部分引脚可以实现复用,以此可以减少第一转接连接器上的引脚的数量。

23、在一些实现方案中,第一转接连接器还包括第一在位引脚,第二转接连接器还包括第二在位引脚;目标板卡包括设置于转接电路板上的第一电压端和第三在位引脚,第一电压端和第三在位引脚连接;当目标板卡为直通板卡时,目标板卡包括一个第三在位引脚,第三在位引脚与第一在位引脚连接。当目标板卡为独立硬盘冗余阵列板卡时,目标板卡包括两个第三在位引脚,其中,一个第三在位引脚与第一在位引脚连接,另一个第三在位引脚与第二在位引脚电连接。主板还包括:设置于板体上的电压电路和可编程逻辑器件。电压电路连接于第一在位引脚和第二在位引脚;其中,在第一在位引脚未连接于第三在位引脚的情况下,电压电路能够使第一在位引脚的电压在第二电压阈值范围内;在第一在位引脚连接于第三在位引脚的情况下,电压电路和第一电压端共同使第一在位引脚的电压在第一电压阈值范围内;在第二在位引脚未连接于第三在位引脚的情况下,电压电路能够使第二在位引脚的电压在第二电压阈值范围内;在第二在位引脚连接于第三在位引脚的情况下,电压电路和第一电压端共同使第二在位引脚的电压在第一电压阈值范围内。可编程逻辑器件连接于第一在位引脚和第二在位引脚,可编程逻辑器件用于:检测第一在位引脚的电压和第二在位引脚的电压;并且,在第一在位引脚的电压和第二在位引脚的电压均在第一电压阈值范围内的情况下,确定第一转接连接器所连接的目标板卡为独立硬盘冗余阵列板卡;在第一在位引脚的电压在第一电压阈值范围内,第二在位引脚的电压在第二电压阈值范围内的情况下,确定第一转接连接器所连接的目标板卡为直通板卡。

24、其中,当主板的第一转接连接器所连接的目标板卡为直通板卡时,直通板卡的第三在位引脚可以与第一在位引脚电连接,而第二在位引脚则处于悬置状态。此时,第一在位引脚可以通过第三在位引脚电连接于第一电压端。此外,第一在位引脚还可以通过电阻电连接于第二电压端,此时,在电压电路和第一电压端的共同作用下,第一在位引脚的电压可以与第一电压端的电压相同,此时,第一在位引脚的电压在第一电压阈值范围内。而第二在位引脚的电压则在处于第二电压阈值范围内。当主板的第一转接连接器所连接的目标板卡为独立硬盘冗余阵列板卡时,独立硬盘冗余阵列板卡的两个第三在位引脚分别电连接于第一在位引脚和第二在位引脚。此时,第一在位引脚和第二在位引脚均可以电连接于第一电压端和电压电路。此时,第一在位引脚和第二在位引脚的电压均处于第一电压阈值范围内。因此,当目标板卡连接于第一转接连接器时,可编程逻辑器件可以自动检测目标板卡的种类。

25、在一些实现方案中,第二转接连接器包括第三引脚组和第四引脚组,第三引脚组连接于中央处理器。主板还包括设置于板体上的第一现场可编程门阵列芯片,第一现场可编程门阵列芯片连接于第四引脚组和存储组件。当目标板卡为独立硬盘冗余阵列板卡时,目标板卡还包括:设置于转接电路板上的独立硬盘冗余阵列芯片和第二输入引脚组,独立硬盘冗余阵列芯片连接于第一输入引脚组、第一输出引脚组和第二输入引脚组,第二输入引脚组电连接于第四引脚组。独立硬盘冗余阵列芯片用于输出第一低速信号,第一低速信号能够通过第二输入引脚组和第四引脚组传输至第一现场可编程门阵列芯片。第一现场可编程门阵列芯片用于将第一低速信号传输至存储组件。

26、其中,通过在转接电路板上设置与独立硬盘冗余阵列芯片电连接的第二输入引脚组,以及在板体上设置第四引脚组和第一现场可编程门阵列芯片,而第一现场可编程门阵列芯片可以电连接于存储组件,其中,第二输入引脚组可以与第四引脚组电连接,从而独立硬盘冗余阵列芯片所输出的第一低速信号可以通过第二输入引脚组、第四引脚组传输至第一现场可编程门阵列芯片,而后第一现场可编程门阵列芯片可以将第一低速信号转发至存储组件,从而独立硬盘冗余阵列芯片可以与存储组件之间进行低速信号的交互。

27、在一些实现方案中,当目标板卡为独立硬盘冗余阵列板卡时,目标板卡还包括:第三转接连接器和第四转接连接器,第一输出引脚组设置于第三转接连接器,第一输入引脚组设置于第四转接连接器;其中,第三转接连接器用于与第一转接连接器插接,第四转接连接器用于与第二转接连接器插接。

28、其中,第三转接连接器与第一转接连接器插接,可以使得第三转接连接器与第一转接连接器之间的连接关系更加稳定,以此可以提高转接电路板与板体之间的连接的可靠性。第四转接连接器与第二转接连接器插接,可以使得第四转接连接器与第二转接连接器之间的连接关系更加稳定,以此可以提高转接电路板与板体之间的连接的可靠性。

29、在一些实现方案中,当目标板卡为直通板卡时,目标板卡还包括设置于转接电路板上的导电件,导电件的一端电连接于第一输入引脚组,另一端电连接于第一输出引脚组。

30、其中,导电件的两端分别与第一输入引脚组和第一输出引脚组电连接,进而第一输入引脚组从第一引脚组所接收的sata协议信号可以通过导电件传输至第一输出引脚组。

31、在一些实现方案中,当目标板卡为直通板卡时,目标板卡还包括第五转接连接器,第一输入引脚组和第一输出引脚组均设置于第五转接连接器,其中,第五转接连接器用于与第一转接连接器插接。

32、其中,第五转接连接器与第一转接连接器插接,因此,第五转接连接器与第一转接连接器之间的连接关系比较可靠,进而可以提高目标板卡与第一转接连接器连接的可靠性。

33、在一些实现方案中,主板还包括设置于板体上的第二现场可编程门阵列芯片,其连接于南桥芯片和存储组件;南桥芯片用于:输出第二低速信号,并传输至第二现场可编程门阵列芯片;第二现场可编程门阵列芯片用于:接收第二低速信号,并将第二低速信号发送至存储组件。

34、其中,通过设置第二现场可编程门阵列芯片,且第二现场可编程门阵列芯片可以与南桥芯片和存储组件电连接,进而南桥芯片可以将第二低速信号传输至第二现场可编程门阵列芯片,第二现场可编程门阵列芯片又可以将第二低速信号传输至存储组件上,以此南桥芯片与存储组件之间还可以进行低速信号的交互。

35、在一些实现方案中,主板还包括:设置于主板上的第六转接连接器,第六转接连接器连接于第二引脚组。存储组件包括硬盘背板和多个硬盘,其中,多个硬盘与硬盘背板插接,硬盘背板与第六转接连接器插接。

36、其中,通过设置第六转接连接器,使得硬盘背板与第六转接连接器插接,而第二引脚组与第六转接连接器电连接,进而第二引脚组所接收的信号可以通过第六转接连接器传输至硬盘背板。其中,第六转接连接器与硬盘背板插接,进而二者之间的连接关系比较可靠。

- 还没有人留言评论。精彩留言会获得点赞!